可靠的電壓監控器IC,一直是工業界的行業需求。因為它可以提高系統可靠性,并在電壓瞬變和電源故障時提升系統性能。當前,半導體制造商都在不斷提高電壓監控器IC的性能,以尋求突破。

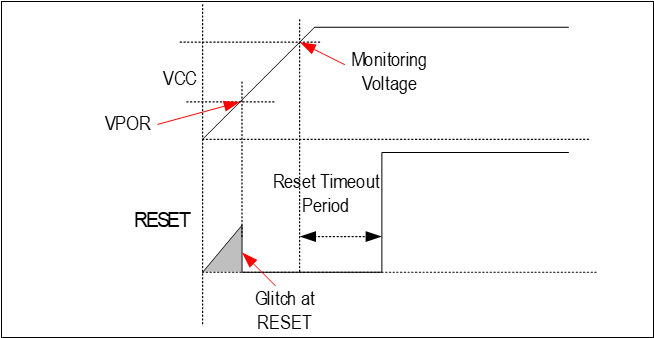

監控器IC需要一個稱為上電復位(VPOR)的最低電壓來生成明確或可靠的復位信號,而在此最低電源電壓到來之前,復位信號的狀態是不確定的。一般來說,將其稱之為復位毛刺。

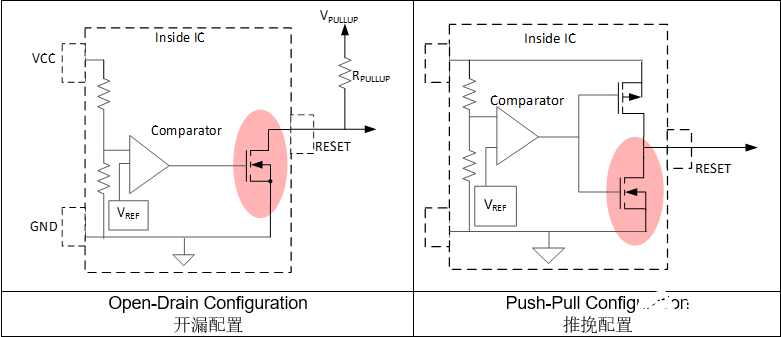

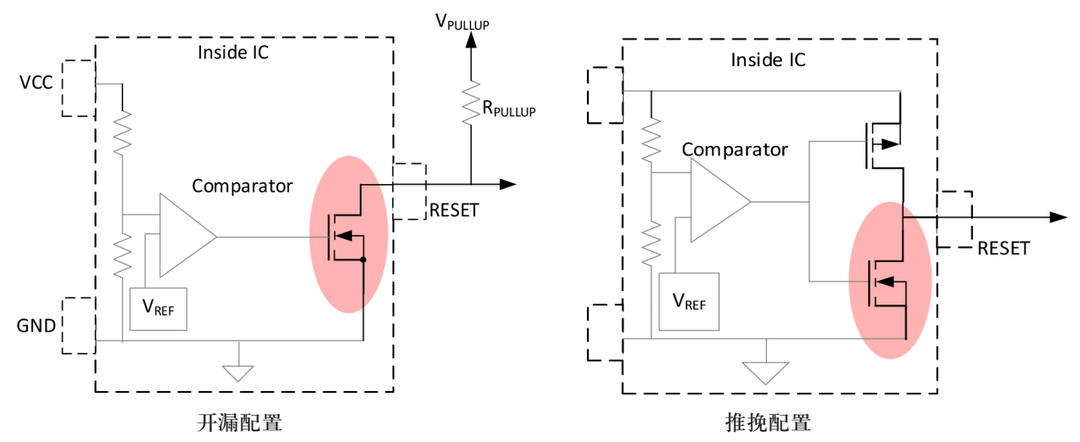

復位引腳主要有兩種不同的拓撲結構,即開漏和推挽(圖1)。兩種拓撲結構都使用NMOS作為下拉MOSFET。

圖1、顯示了復位拓撲的開漏配置和推挽配置

上電期間,如果電源電壓低于VPOR,就沒有足夠的電壓能驅動內部MOSFET工作,因此MOSFET關閉。此時,監控器無法對復位電壓進行控制。復位電壓將與上拉電壓(VPULLUP)成比例上升。而一旦電源電壓高于VPOR,內部MOSFET將驅動RESET引腳進入有效狀態。

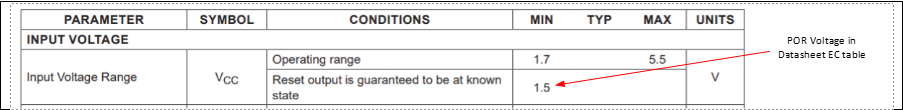

圖2、顯示了復位電壓如何與上拉電壓(VPULLUP)成比例上升,從而導致通常所說的復位毛刺。

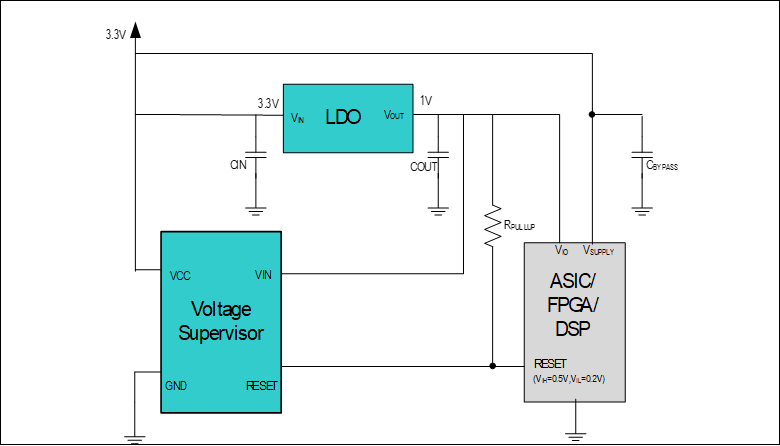

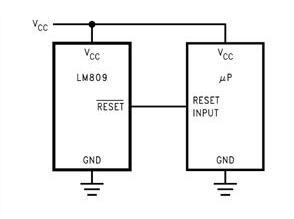

電壓監控器可用于監控FPGA、ASIC或DSP的低電源軌,其電壓可低至1V。在低供電電壓處理器中,I/O的邏輯電平非常敏感,其VIH可低至0.5V,如圖3所示。

上電期間,FPGA、ASIC或DSP需要處于RESET狀態,直到所有電源軌穩定。當VDD低于VPOR時,RESET引腳可能會出現毛刺,該毛刺可能會觸發FPGA的未知狀態。一旦VDD高于VPOR,內部MOSFET就會開啟并將RESET連接到GND,并使RESET引腳輸出正確的邏輯低電平。

圖3、顯示了監控器與低供電電壓ASIC/FPGA/DSP的接口

圖4、顯示了帶毛刺復位信號的上電時序。

隨著電子行業向低壓半導體發展,模擬芯片制造商也在傳統監控器的基礎上努力實現無毛刺監控器。制造商可以通過改進工藝來降低VPOR,但實現真正的無毛刺監控器需要一個全新的架構。

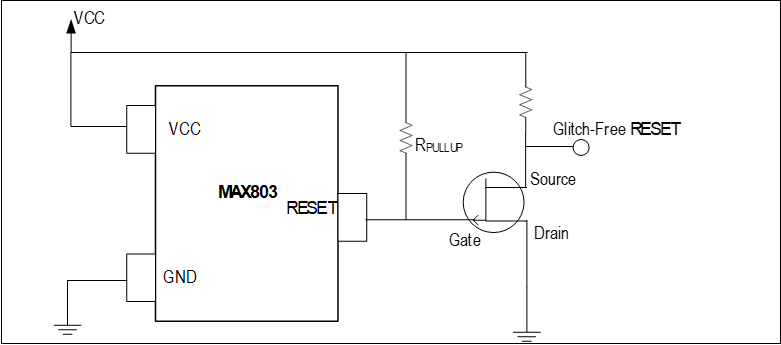

目前,系統工程師使用帶有傳統監控器的外部電路來模擬圖5所示的無毛刺監控功能。添加一個配置為源極跟隨器的標準JFET可以實現這一功能,源極的電壓將取決于柵極電壓VG與JFET閾值電壓的差。JFET閾值電壓會在VG和VOUT之間產生大約1V的壓降,從而避免監控器的輸出電壓在內部MOSFET關斷時升高,直到監控器的內部MOSFET開始正常工作。

圖5、顯示了一個帶有外部P-JFEF的傳統監控器,可實現無毛刺工作。

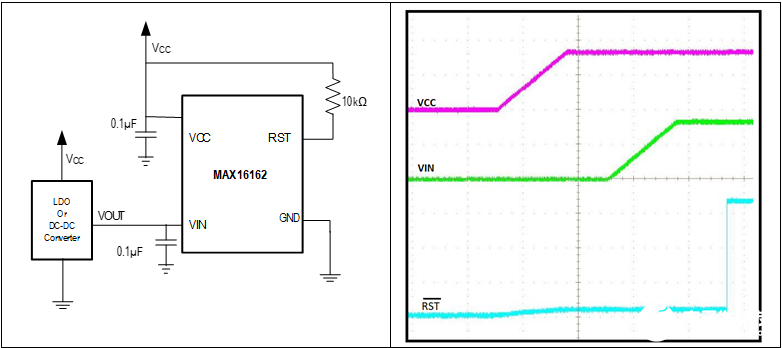

真正的無毛刺監控器可以通過復位吸入電流,即使當VCC為零時也會將復位引腳強制拉到接地電位。圖6顯示了一種真正無毛刺監控器的示例電路。ADI的MAX16161/MAX16162無需任何外部組件即可實現無毛刺工作,小巧且經濟。

圖6、MAX16162的應用示意圖和相應的時序圖

總結:

真正的無毛刺監控器IC不再只是一個概念。設計人員現在已擁有了一款可在零電源電壓下產生可靠復位信號的監控器IC,使系統工程師能夠使用該IC來監控低供電壓(低于1V)的電子器件。而且MAX16161/MAX16162為微型nanoPower IC,靜態電流僅為825nA,有助于延長系統電池壽命。

-

ADI

+關注

關注

146文章

45819瀏覽量

249754 -

復位信號

+關注

關注

0文章

54瀏覽量

6314

發布評論請先 登錄

相關推薦

電源IC 電流和電力監控器、調節器

如何選擇合適的電壓檢測器、監控器和復位IC?

電壓檢測器和監控器和復位IC怎么選擇

使用TPS386000和LM3880創建時序電壓監控器(復位IC)

如何提高電壓監控器IC的性能

如何提高電壓監控器IC的性能

評論