VADJ 引腳是 VITA 57.1 FMC 標準的一部分,承載著從載卡到 I/O 夾層模塊的可調節電壓等級的電源。

這通過 FMC 卡上的 IPMI 支持型 EEPROM 定義。如欲了解有關 VADJ 行為及初始化的更多詳情,敬請查看(67103)。

如果所選 I/O 夾層模塊上沒有準確定義 VADJ 電壓(按照 VITA 57.1 規范),可能必須手動控制 VADJ 電壓的上電,才能確保系統上電準確無誤。

在 UltraScale 評估套件上,VADJ 電壓可通過系統控制器的 FMC 菜單手動開關。VADJ 可使用下列程序手動啟用,但必須謹慎。

解決方法:

UltraScale 評估套件支持 VITA 57.1 規范中定義的 EEPROM IPMI 格式。

如果所連接的 I/O 夾層模塊(FMC 卡)有一個空白或損壞的 EEPROM,就無法啟用 VADJ 軌。

從 UltraScale 系列開始的所有 Xilinx 評估套件均已實現該行為方式。

評估套件都能使用系統控制器 UART 菜單手動重載 VADJ:

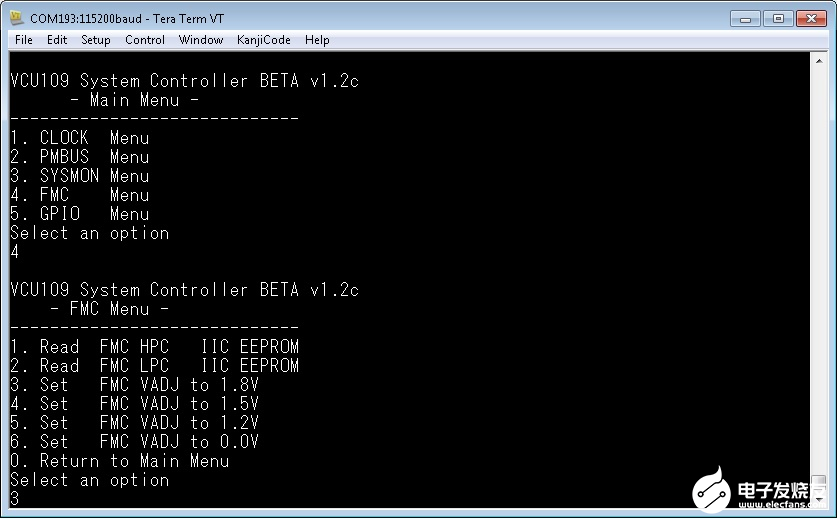

1. 請通過 USB UART(選擇 增強型 COM 端口、波特率為 115200)連接系統控制器。

2. 在您的終端程序(例如 TeraTerm)中,在設置選項卡下打開“串聯端口”并選擇波特率為 115200、數據為 8 位、無奇偶校驗、停止 1 位、流量控制為無。 Click OK.

3. 系統控制器主菜單將出現在終端窗口中,請選擇“4.FMC 菜單”。

4. 選擇選項 3 到 6,手動將 VADJ 設置為適當的電壓等級,就可完成您的設置。

-

控制器

+關注

關注

113文章

16573瀏覽量

180411 -

System

+關注

關注

0文章

165瀏覽量

37221 -

開發板

+關注

關注

25文章

5210瀏覽量

99120 -

UltraScale

+關注

關注

0文章

118瀏覽量

31564

發布評論請先 登錄

相關推薦

Zynq UltraScale+ MPSoC的ZCU102開發套件的開發流程

Virtex UltraScale+ FPGA VCU110開發套件的特點性能演示

RF開發板和評估板套件無線系統設計中的應用

基于Xilinx Zynq ultraScale+ 系列FPGA的AXU2CGB 開發板評測

UltraScale開發板與套件-使用System Controller手動調整VADJ

UltraScale開發板與套件-使用System Controller手動調整VADJ

評論