本文概覽

因為NI LabVIEW是數(shù)據(jù)流編程語言,開發(fā)者們可以編寫并行的應用程序,這些應用程序可以直接映射到并行的硬件(如多核心處理器和FPGA等)上以獲得最優(yōu)異的性能。這篇白皮書討論了什么是數(shù)據(jù)流編程以及為什么說NI LabVIEW是多核系統(tǒng)編程的首選。

免費午餐結(jié)束了

近幾年來,處理器的速度遭遇到了瓶頸。摩爾定律表明,每隔18~24個月芯片中晶體管的數(shù)量就會增加一倍。這在過去的40年里始終是適用的,但是芯片性能卻不再保持線性增加了。過去,芯片生產(chǎn)廠商通過增加處理器的時鐘速度來提高芯片的性能,如從100~200MHz,再到最近的數(shù)GHz的范圍。

但是在今天,由于功耗和散熱的限制,通過提高時鐘速度來增加性能的方法行不通了。芯片廠商開始轉(zhuǎn)向另一種全新的芯片構架,就是在單芯片上集成多個處理器內(nèi)核。相對于單核處理器,程序員們可以使用多核處理器完成更多的任務。為了充分利用多核處理器,程序員們需要重新考慮開發(fā)應用程序的方法。微軟公司的軟件設計師Herb Sutter曾說過,對于那些期望最終用戶簡單的將計算機升級到更快的處理器就可以立即看到軟件程序性能提升的開發(fā)者而言,“免費午餐結(jié)束了”。簡而言之,在相當長的一段時間里,軟件開發(fā)是這樣的,但是現(xiàn)在情況不同了。

正在轉(zhuǎn)向在單個處理器上集成多個核心的方法。

順序執(zhí)行的程序在處理器的速度提升后將得到性能的改善,將電腦升級到更快的CPU意味著一個序列中每個單獨的指令都將運行得更快。為了在多核系統(tǒng)中繼續(xù)獲得性能提升,你需要設計一個在內(nèi)核間分配任務的應用程序,從本質(zhì)上說來就是開發(fā)并行應用程序來取代順序執(zhí)行的程序。

LabVIEW――一種圖形化數(shù)據(jù)流式編程語言

在LabVIEW中開發(fā)應用程序的主要優(yōu)勢是這種語言有著直觀、圖形化的特點。在LabVIEW中,用戶解決工程問題就像是在紙上畫框圖一樣。現(xiàn)代多核處理器技術使得LabVIEW成為一種更適合的編程工具,因為它有著并行化表達和執(zhí)行任務的能力。

LabVIEW的數(shù)據(jù)流特性使得如果連線中存在著分支,或者是框圖中存在并行序列,那么LabVIEW執(zhí)行機構會嘗試著并行的執(zhí)行程序。在計算機科學術語中,這稱為“潛在的并行化”,因為你不需要根據(jù)并行運行的需要明確地編寫并行代碼,編程語言自己會進行一定程度的并行化。

從單核到雙核計算機,理論上講,獲得的性能應該是原來的兩倍。但是,與這個極限接近的程度取決于用戶應用程序運行的并行化程度。LabVIEW程序員們可以很方便的以并行方式來表示他們的解決方案。對于普通的LabVIEW應用程序而言,如果不考慮多核心編程技術,在不改寫代碼的情況下,與最初的程序相比,可以獲得25%到35%的性能提升,這都是緣于普通LabVIEW程序所具有的并行特性。

圖2是一個簡單的應用程序的例子。其中,LabVIEW代碼中的分支簡化了兩個分析任務――一個濾波器操作和一個快速傅立葉變換(FFT),使它們可以在雙核機器上并行執(zhí)行。在圖表中沒有顯示的性能測試代碼,它首先在單核模式下(關掉其中的一個核)運行“for loop”一次,然后在雙核的模式下運行。因為這兩項任務都是計算量很高的,利用任務并行化獲得的性能改進為原來的1.8倍。

基于文本的編程語言如C語言等,在代碼中利用特殊標記來表示并行化代碼,創(chuàng)建并行任務(也就是創(chuàng)建獨立的線程)。管理這些多線程的應用程序?qū)⑹且粋€挑戰(zhàn)。

在C語言中,用戶必須使用鎖操作、互斥量、原子操作和其他高級編程技術來管理同步。當多線程變得難于跟蹤調(diào)試,通常的編程缺陷便出現(xiàn)了,如下所示:

1. 由于線程太多而導致效率低下。

2. 死鎖――線程一直在等待某些而不能進行處理。

3. 競爭狀況- 代碼運行的時序沒有被正確管理,在需要數(shù)據(jù)時,數(shù)據(jù)不是沒有準備好就是已經(jīng)被覆蓋掉了。

4. 存儲器沖突――與代碼中存儲器管理相關的問題。

由于使用C語言進行開發(fā)面臨的這些挑戰(zhàn),LabVIEW程序員們可以獲得比以往更高的效率。

LabVIEW是利用實時SMP支持,處于“Multicore Ready”軟件層的最上層Intel公司定義了用戶需要評估的四個軟件層次來確定多核系統(tǒng)的可用程度。如果所用的應用程序庫和設備驅(qū)動不是為多核而設計的,或者操作系統(tǒng)不能夠在多個核心上進行負載均衡,那么并行程序在多核心系統(tǒng)上并不會運行得更快。

審核編輯 黃宇

因為NI LabVIEW是數(shù)據(jù)流編程語言,開發(fā)者們可以編寫并行的應用程序,這些應用程序可以直接映射到并行的硬件(如多核心處理器和FPGA等)上以獲得最優(yōu)異的性能。這篇白皮書討論了什么是數(shù)據(jù)流編程以及為什么說NI LabVIEW是多核系統(tǒng)編程的首選。

免費午餐結(jié)束了

近幾年來,處理器的速度遭遇到了瓶頸。摩爾定律表明,每隔18~24個月芯片中晶體管的數(shù)量就會增加一倍。這在過去的40年里始終是適用的,但是芯片性能卻不再保持線性增加了。過去,芯片生產(chǎn)廠商通過增加處理器的時鐘速度來提高芯片的性能,如從100~200MHz,再到最近的數(shù)GHz的范圍。

但是在今天,由于功耗和散熱的限制,通過提高時鐘速度來增加性能的方法行不通了。芯片廠商開始轉(zhuǎn)向另一種全新的芯片構架,就是在單芯片上集成多個處理器內(nèi)核。相對于單核處理器,程序員們可以使用多核處理器完成更多的任務。為了充分利用多核處理器,程序員們需要重新考慮開發(fā)應用程序的方法。微軟公司的軟件設計師Herb Sutter曾說過,對于那些期望最終用戶簡單的將計算機升級到更快的處理器就可以立即看到軟件程序性能提升的開發(fā)者而言,“免費午餐結(jié)束了”。簡而言之,在相當長的一段時間里,軟件開發(fā)是這樣的,但是現(xiàn)在情況不同了。

正在轉(zhuǎn)向在單個處理器上集成多個核心的方法。

順序執(zhí)行的程序在處理器的速度提升后將得到性能的改善,將電腦升級到更快的CPU意味著一個序列中每個單獨的指令都將運行得更快。為了在多核系統(tǒng)中繼續(xù)獲得性能提升,你需要設計一個在內(nèi)核間分配任務的應用程序,從本質(zhì)上說來就是開發(fā)并行應用程序來取代順序執(zhí)行的程序。

LabVIEW――一種圖形化數(shù)據(jù)流式編程語言

在LabVIEW中開發(fā)應用程序的主要優(yōu)勢是這種語言有著直觀、圖形化的特點。在LabVIEW中,用戶解決工程問題就像是在紙上畫框圖一樣。現(xiàn)代多核處理器技術使得LabVIEW成為一種更適合的編程工具,因為它有著并行化表達和執(zhí)行任務的能力。

LabVIEW的數(shù)據(jù)流特性使得如果連線中存在著分支,或者是框圖中存在并行序列,那么LabVIEW執(zhí)行機構會嘗試著并行的執(zhí)行程序。在計算機科學術語中,這稱為“潛在的并行化”,因為你不需要根據(jù)并行運行的需要明確地編寫并行代碼,編程語言自己會進行一定程度的并行化。

從單核到雙核計算機,理論上講,獲得的性能應該是原來的兩倍。但是,與這個極限接近的程度取決于用戶應用程序運行的并行化程度。LabVIEW程序員們可以很方便的以并行方式來表示他們的解決方案。對于普通的LabVIEW應用程序而言,如果不考慮多核心編程技術,在不改寫代碼的情況下,與最初的程序相比,可以獲得25%到35%的性能提升,這都是緣于普通LabVIEW程序所具有的并行特性。

圖2是一個簡單的應用程序的例子。其中,LabVIEW代碼中的分支簡化了兩個分析任務――一個濾波器操作和一個快速傅立葉變換(FFT),使它們可以在雙核機器上并行執(zhí)行。在圖表中沒有顯示的性能測試代碼,它首先在單核模式下(關掉其中的一個核)運行“for loop”一次,然后在雙核的模式下運行。因為這兩項任務都是計算量很高的,利用任務并行化獲得的性能改進為原來的1.8倍。

基于文本的編程語言如C語言等,在代碼中利用特殊標記來表示并行化代碼,創(chuàng)建并行任務(也就是創(chuàng)建獨立的線程)。管理這些多線程的應用程序?qū)⑹且粋€挑戰(zhàn)。

在C語言中,用戶必須使用鎖操作、互斥量、原子操作和其他高級編程技術來管理同步。當多線程變得難于跟蹤調(diào)試,通常的編程缺陷便出現(xiàn)了,如下所示:

1. 由于線程太多而導致效率低下。

2. 死鎖――線程一直在等待某些而不能進行處理。

3. 競爭狀況- 代碼運行的時序沒有被正確管理,在需要數(shù)據(jù)時,數(shù)據(jù)不是沒有準備好就是已經(jīng)被覆蓋掉了。

4. 存儲器沖突――與代碼中存儲器管理相關的問題。

由于使用C語言進行開發(fā)面臨的這些挑戰(zhàn),LabVIEW程序員們可以獲得比以往更高的效率。

LabVIEW是利用實時SMP支持,處于“Multicore Ready”軟件層的最上層Intel公司定義了用戶需要評估的四個軟件層次來確定多核系統(tǒng)的可用程度。如果所用的應用程序庫和設備驅(qū)動不是為多核而設計的,或者操作系統(tǒng)不能夠在多個核心上進行負載均衡,那么并行程序在多核心系統(tǒng)上并不會運行得更快。

審核編輯 黃宇

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權轉(zhuǎn)載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學習之用,如有內(nèi)容侵權或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

-

FPGA

+關注

關注

1629文章

21729瀏覽量

603002 -

芯片

+關注

關注

455文章

50714瀏覽量

423149 -

LabVIEW

+關注

關注

1970文章

3654瀏覽量

323324 -

C語言

+關注

關注

180文章

7604瀏覽量

136692 -

編程

+關注

關注

88文章

3614瀏覽量

93686

發(fā)布評論請先 登錄

相關推薦

工業(yè)機器人的四種編程(示教編程、離線編程、自增強現(xiàn)實編程主編程)剖析!

和工作量,提高編程效率,實現(xiàn)編程的自適應性,從而提高生產(chǎn)效率,是機器人編程技術發(fā)展的終極追求。本文將就機器人編程技術的發(fā)展作一介紹,希望能給讀者帶來一些啟發(fā)。對工業(yè)

多核CPU的優(yōu)勢是什么

多核CPU(Central Processing Unit,中央處理器)作為現(xiàn)代計算機技術的重要里程碑,其優(yōu)勢在于顯著提升了計算性能、多任務處理能力、系統(tǒng)穩(wěn)定性以及能效比等多個方面。以下將詳細闡述

risc-v多核芯片在AI方面的應用

多核芯片在AI方面的應用具有廣闊的前景和巨大的潛力。隨著技術的不斷進步和應用的深入,我們期待看到更多基于RISC-V多核芯片的AI解決方案在實際應用中得到驗證和推廣。

發(fā)表于 04-28 09:20

淺談物聯(lián)網(wǎng)技術的電氣火災智能監(jiān)控系統(tǒng)平臺設計

淺談物聯(lián)網(wǎng)技術的電氣火災智能監(jiān)控系統(tǒng)平臺設計 張穎姣 安科瑞電氣股份有限公司 上海嘉定 201801 摘要:為了提高電氣火災監(jiān)控效果,該文設計了基于無線通信技術的電氣火災智能監(jiān)控

淺談無線物聯(lián)網(wǎng)技術的電氣火災監(jiān)控系統(tǒng)設計

淺談無線物聯(lián)網(wǎng)技術的電氣火災監(jiān)控系統(tǒng)設計 張穎姣 安科瑞電氣股份有限公司?上海嘉定 201801 摘要:電氣故障是引起火災的重要原因。由于傳統(tǒng)的火災報警器都是獨立存在的,不僅沒有組網(wǎng),數(shù)據(jù)也不同步

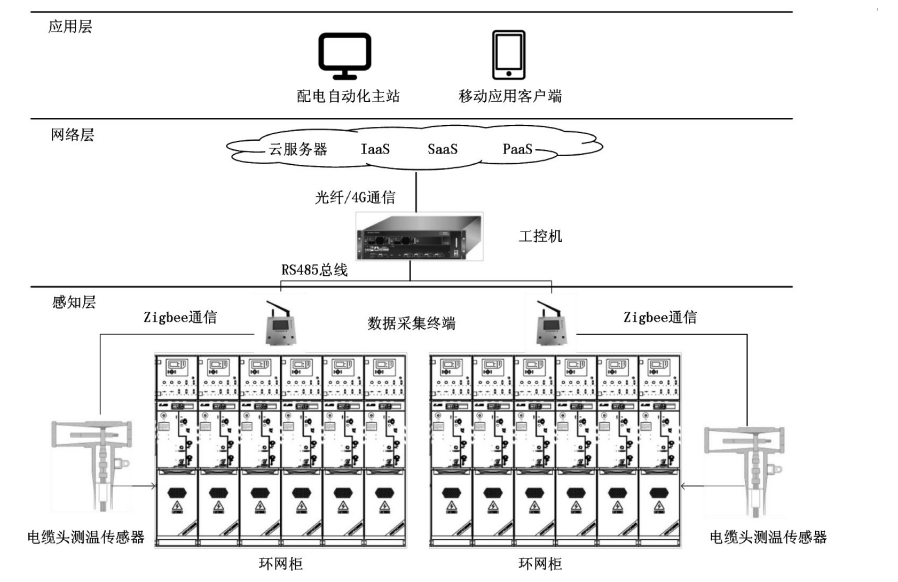

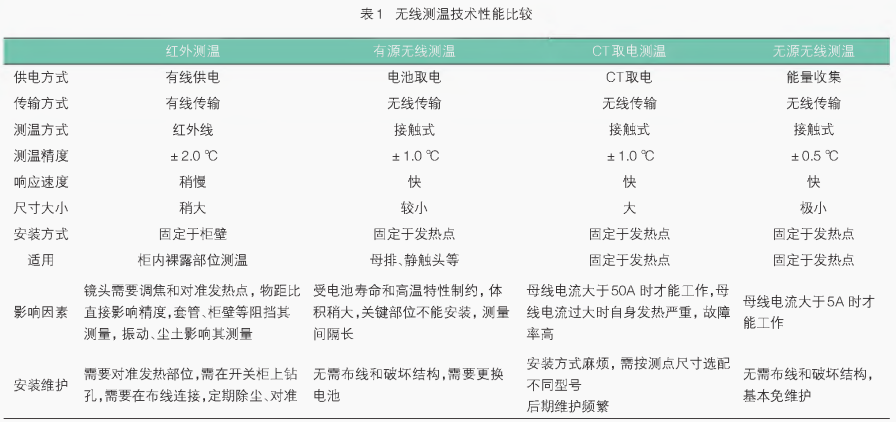

淺談基于物聯(lián)網(wǎng)技術的無線測溫系統(tǒng)設計

淺談基于物聯(lián)網(wǎng)技術的無線測溫系統(tǒng)設計 張穎姣 安科瑞電氣股份有限公司 上海嘉定 201801 摘要: 傳統(tǒng)10kV環(huán)網(wǎng)柜存在智能化程度低、電纜頭故障率高、測溫困難等問題,缺乏一種有效的在線測溫

多核異構通信框架(RPMsg-Lite)

概要 隨著科技的飛速發(fā)展,計算需求日益復雜和多樣化,傳統(tǒng)的單核處理器已難以滿足所有應用場景的需求。在這樣的背景下,異構多核系統(tǒng)應運而生,成為推動計算領域進步的重要力量。異構多核系統(tǒng)不僅

碩博電子推出一款基于CoDeSys3.5編程技術的高性能主控制器

碩博電子自主研發(fā)的移動控制器SPC-SFMC-X2214A,采用了CoDeSys3.5編程技術,為分布式應用場合提供了理想的主控制器解決方案。

AURIX系列MCU多核系統(tǒng)和時鐘有關系嗎?

AURIX系列MCU多核系統(tǒng)和時鐘有關系嗎?2.如何系統(tǒng)的理解GTM的時鐘結(jié)構(以前用的ST的片子,發(fā)現(xiàn)英飛凌MCU的時鐘樹和ST的很不一樣,有些時鐘實現(xiàn)的功能和原理是一樣的)?3.編寫應用程序是不是不能脫離底層比較好?

發(fā)表于 02-05 06:10

淺談無線測溫系統(tǒng)在電廠的研究和應用

淺談無線測溫系統(tǒng)在電廠的研究和應用 摘要: 采集關鍵電力設備接電的實時溫度,克服有線溫度監(jiān)測系統(tǒng)存在的諸如線路多,布線復雜,維護困難等不足,將無線無源傳感器與Zigbee無線通信技術相

淺談多CPU、多核CPU、超線程技術、SMP

Local APIC: APIC全稱是Advanced Programmable Interrupt Controller,翻譯過來就是高級可編程中斷控制器,用來處理CPU中斷。

淺談多核系統(tǒng)編程技術

淺談多核系統(tǒng)編程技術

評論