1 可重構測控系統的提出

測控系統一般是指基于計算機實現數據采集和控制的系統。測控系統在工業現場控制、家庭數字化管理、通信和網絡等方面應用廣泛,并不斷向低成本、高速、高性能、智能化、開放化方向邁進。但現代測控系統在設計和應用中仍然面臨不少的難題:

①設計速度難以適應產品更新換代的快速變化。一般測控系統的設計都是針對某個特定的任務,從設計到投入使用的周期至少1~2年,甚至長達4~5年。因此,在設計階段堪稱先進的方案往往在投入使用伊始就已落后了。

②設計方案功能固定,通用性差,難以滿足不同層次、不斷變化的用戶需求。測控系統設計針對具體用戶,配置各異,通用性較差。如何滿足不同用戶、不同層次的需要,尤其是多任務用戶需要是一大難題。

③虛擬儀器技術的應用使得軟件重構成為可能,但是達到還難以達到硬件重構和“即插即用”的效果。

因此,研究一種軟硬件可重構、開放化、普適性的測控系統,對于實現測控系統的快速、開放式設計,降低用戶使用成本具有很高的應用價值。本文基于現代測控系統的通用化結構特征和可重構的現場可編程門陣列FPGA技術的發展,提出一種可重構測控系統(Reconfigurable Mo―nitoring System,RMS)的設計構想,并給出其應用實例。

1.1 測控系統的結構模式和多任務特征

隨著計算機軟硬件技術和測控技術的不斷深入融合,現代測控系統在結構上呈現出通用化特征,即“系統前端(信息的數據采集(A/D))+數字信號處理(DSP)+系統后端(輸出(D/A)及顯示)”的模式。這種清晰的、通用化的結構模式為用戶實現測控系統的自組織、重定義和再利用創造了條件。

現代測控系統一般都具備多任務性,即系統需要同時完成幾個單獨的空間相關的(并行性)任務,或順序完成幾個時間相關的(順序性)任務。傳統的多任務設計方法,是通過增加硬件的數量,或加大軟件的控制功能來實現多任務性。一方面,增加了工程設計、調試的難度和成本,使得應用系統越來越龐大、復雜;另一方面,電路和軟件的復雜帶給用戶眾多的麻煩。可重構技術的出現為解決多任務問題提供了新的思路。

1.2 可重構技術與可重構器件

可重構技術是21世紀初以來信息技術的研究熱點,是一種可以根據系統功能變化的需要重組自身資源,實現軟硬件結構自我優化、自我生成的計算機技術。可重構技術包括硬件重構和軟件重構兩個方面。根據應用任務的需要進行軟件重構,在傳統的系統設計中已普遍存在,而硬件重構(指系統的硬件邏輯結構發生改變)則是傳統的系統設計無法實現的。可重構技術的廣泛應用必須以提供可編程資源的可重構硬件為物質基礎。

隨著微電子技術的不斷發展,20世紀末出現的可編程邏輯器件(PLD)和可編程模擬器件(PAD)為測控系統的功能重構提供了硬件基礎。可重構器件主要包括以下幾種:

(1)可重構邏輯器件FPGA

FPGA的可編程器件是基于SRAM的,可以快速地重新編程,即所謂“現場可編程”。這一特性使FPGA獲得廣泛應用,并成為可重構測控系統發展的持續驅動力量。FPGA是構建可重構測控系統必不可少的關鍵器件。

(2)可重構模擬器件

可編程模擬器件(PAD)既屬于模擬集成電路,具有信號調理、模擬計算、中高頻應用等典型功能;又同PLD器件一樣,可由用戶通過現場編程和配置來改變其內部連接和元件參數,從而獲得所需要的電路功能。配合相應的開發工具,其設計和使用均可以像PLD一樣方便、靈活和快捷。例如Lattice公司的可編程模擬芯片ispPAC30內含4個輸入儀表放大器、2個獨立的內部可控參考源和2個增強型DAC,提供了系統與測控對象的模擬接口,可用于連接模擬輸入,實現系統的數據采集功能;利用其可編程功能,可針對不同應用重構其功能。但相對于可編程邏輯器件,可編程模擬器件問世較晚,品種偏少,還不能作為主流的可重構器件。

(3)可重構DSP器件

DSP器件適用于計算密集、算法復雜、并發性和實時性要求突出的場合,如帶有智能邏輯的消費類產品、生物信息識別終端、帶有加解密算法的鍵盤、ADSL接入、實時語音壓解、虛擬現實顯示等。這類智能化算法一般運算量較大,特別是向量運算、指針、線性尋址等較多,這些正是DSP處理器的長處所在。但常規的DSP無硬件重構功能,而支持DSP器件硬件重構的技術尚在研發中,難以投入大規模的應用。當然,可以通過傳統的軟件重構設計實現DSP功能重定義,但這不是我們在此討論的內容。一種實現可重構DSP器件的實用方法是利用FPGA器件實現可重構的DSP功能(如參考文獻),其實質是以可重構的FPGA器件為基礎實現DSP功能的重構。

綜上所述,FPGA器件的現場可編程特征成為可重構技術應用的關鍵,為可重構測控系統的設計提供了可行性。RMS就是以可重構器件構建系統硬件平臺,并在軟件平臺控制下產生不同的重載數據流來改變FPGA形成的硬件結構,以滿足不同任務要求。其實質是一種軟硬件協同設計技術。

2 基于FPGA的RMS的設計

2.1 基于FPGA的RMS的設計原則

進行可重構測試系統的設計應遵循以下基本原則:

(1)接口標準化

在測控系統的接口設計上,盡量采用開放式、標準化體系的接口標準,例如采用通用的讀寫、控制總線結構、標準的伺服驅動接口等。

(2)功能實現模塊化

RMS的軟件和硬件設計均采用模塊化的設計思想。依功能進行模塊劃分,合理分配給FPGA器件和DSP器件。對于FPGA器件的功能,采用硬件描述語言進行邏輯描述,經功能設計、時序仿真、電路測試、模塊封裝,制作成專門的測控IP,供設計平臺調用。

(3)系統集成化、開放化

將自己開發的測控IP和從其他IP供應商處購買到的標準IP,利用專門的綜合軟件集成為測控系統。還可以通過裁剪和重整不同的IP來改變設計,達到既能實現功能定制、滿足目前測控要求,又具有開放性、能適應未來功能擴展的目標。

(4)根據系統規模靈活選用主控制器

作為RMS的核心,可重構主控制器是體現RMS規模和功能不同的關鍵器件。可以根據測控對象的需要靈活選擇其實現器件及功能模塊,以實現功能和造價的合理平衡。可以選用低成本的FPGA方案,以有限狀態機(FSM)模式完成功能設計,以JTAG被動串行方式下載實現靜態重構,用于簡單、低速的數據采集;也可以選用高性能的SOPC方案,實現可動態重構,以滿足高速、復雜數據處理的需要。

(5)嵌入式特征

RMS具有功能可裁剪、結構重定義和軟硬件協同設計特征,是典型的嵌入式系統。

2.2 基于FPGA的RMS的結構與設計

RMS可以視為一個通用的測控設計平臺。

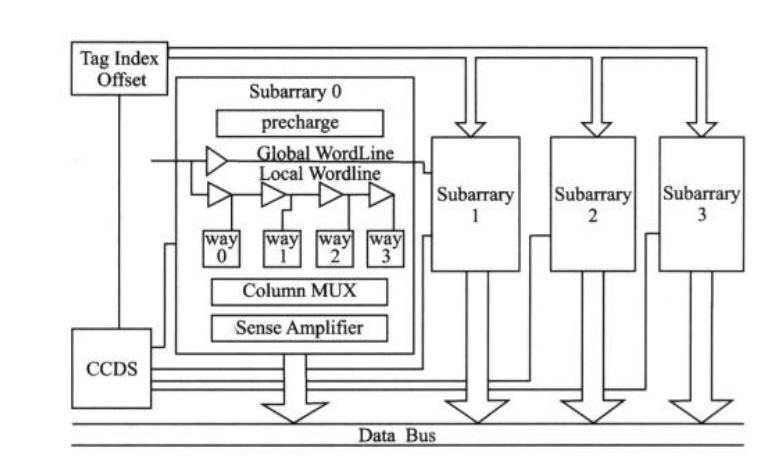

該測控系統由主控計算機和相對獨立的基于FPGA器件的測控系統兩大部分,通過通信接口連接而成。主控計算機主要實現人機對話功能,包括測試數據的處理、顯示及儀器軟面板的控制,可以利用虛擬儀器技術實現。基于FPGA器件的測控系統包括數據采集與輸出控制單元、FPGA單元和DSP單元,3個單元均有可重構功能,并接受主控制器單元的控制。基本功能塊是指作為計算機系統通用的不可或缺的電源、系統監控模塊及存儲器模塊。

2.2.1 可重構數據采集與輸出控制單元

該單元作為RMS的前向、后向通道與被測控對象直接相連。其中的信號調理電路可以設計成通用形式,并根據測控對象的數量、量程、模擬/數字類型、濾波參數等進行重定義和調整。例如可以采用可重構PAD器件直接與模擬測試對象相連,并由主控計算機完成設計、仿真、測試,通過主控制器單元實現重構。

2.2.2 可重構FPGA單元和可重構DSP單元

FPGA單元和DSP單元的功能可以預先根據實際測試對象的需要進行合理劃分,并在主控計算機上以IP核的方式完成設計、仿真、測試和整合的全過程,最后的配置數據流文件預先存放于相應的配置存儲器中(一般為SRAM或Flash存儲器)。這種靜態重構方式適用于對配置實時性要求不太高的一般場合,選用基于SRAM的FPGA器件和通用DSP即可。如果對配置切換的實時性要求較高,則可以選用特定的適于動態配置的FPGA器件,但成本要高昂得多。

2.2.3 可重構主控制器

主控制器單元是實現可重構功能的關鍵部分,它既是測控系統與主控計算機數據傳遞的通道,又是數據采集與輸出控制單元、FPGA單元和DSP單元的控制中樞。在系統重構模式下,它接收主控計算機的重構指令和數據,對FPGA和DSP的配置存儲器進行在線編程;在正常測控模式下,主控制器從FPGA和DSP獲得采集和處理的數據,并送主控計算機處理。

主控制器的設計可以根據系統規模合理選擇,可以采用通用MCU(如51系列單片機)、嵌入式SoC(如ARM);也可利用FPGA器件實現,例如選用A1tera公司的Nios軟處理器核基于SOPC方法進行設計。

2.2.4 通信結構

RMS通信結構的選擇對系統的工作速度、實時性以及成本來說至關重要。

從通用性角度考慮,RMS的通信結構可以根據系統規模的需要選擇不同的形式。大型測控系統可以選用專用測控總線(如GPIB、CPI、CPCI等),以標準化、模塊化插卡形式與主控計算機相連;小型系統則可以根據需要選用通用總線(如RS232、UART、USB、CAN總線),有選擇地添加可編程I/O口、ZigBee無線通信接口、TCP/IP協議、以太網接口等通信、網絡擴展接口,以滿足無線通信和網絡測控功能擴展的需要。不論規模大小,接口類型各異,都可用IP模塊的形式進行設計并配置到FPGA器件上,以滿足不同應用需要。

值得注意的是,測控系統的通信結構設計不僅要包括系統總線的設計,還包括FPGA片內通信結構的設計。典型的可重構FPGA片內通信結構通常有片上總線和片上網絡兩種策略。片上網絡結構雖能較好地體現結構參數要求,但面積花費巨大;而片上總線結構憑借靈活性高、可延展、設計開銷小、帶寬要求較低、時延較短等優點,成為RMS的首選。考慮到FPGA的配置需要,在通信模塊、主控制器模塊和FPGA器件內都應設計相應的JTAG接口,以滿足數據流配置和在線測試的需要。

2.2.5 軟件重構

軟件重構是作為軟硬件協同設計實現的測控系統重構的必要內容。傳統的測控軟件常常是針對具體的測控、對象和硬件資源設計的,從而限制了不同型號、不同廠家、不同硬件接口的測控器件的使用。為實現測控系統的軟件重構,應打破傳統測控軟件的設計思路,采用“基于程序框架和可復用構件”的軟件復用思路”。將測控軟件劃分為測控軟件平臺和測控驅動程序兩部分,其間通過軟件平臺提供的軟件接口來實現動態鏈接。測控軟件平臺主要實現主控計算機功能的控制,以及主控計算機與測控系統的驅動程序之間的數據通信

測控終端應用軟件的可重構、可識別包含兩個方面:其一,測控軟件平臺的可重構,即不同測控應用的軟件平臺能夠識別相同的控制指令,準確完成主控計算機分配的測控任務;其二,測控驅動程序的可重構,即各種不同類型的測量、控制應用的驅動程序可以動態鏈接到軟件平臺上,實現“熱拔插”。

測控軟件的重構平臺有多種選擇:可以是專用的基于圖形化GUI的虛擬儀器軟件,如Labview(通過CLF節點實現與儀器驅動程序的接口,儀器驅動程序以動態鏈接庫的形式給出,將與儀器有關的I/0操作都封裝成函數,并通過訪問USB或其他接口驅動實現數據的輸入、輸出);也可以采用通用的可視化軟件編程環境,如VB、VC等。對于小型、較簡單的測控系統,推薦選用圖形化、高效的Labview。

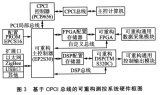

3 基于CPCI總線的RMS的實現

下面給出的實例是應用于雷達信號實時偵測的基于CPCI總線的RMS。傳統的雷達偵測,由于信號特征和處理方式不同,需要研制多種獨立的偵測卡(如脈沖雷達偵測卡、連續波雷達偵測卡、敵我識別信號偵測卡等十幾種設備)及對應測控軟件。采用通用的硬件平臺,由1個CPCI工業控制計算機和2塊CPCI可重構硬件電路板卡構成,根據不同種類的雷達信號分別進行FPGA和DSP的設計,并將配置文件存儲在計算機中。實際工作時,針對不同的雷達信號,通過應用軟件選擇對應的軟硬件配置文件進行動態可重構,達到了小型化、通用化和軟硬件可重構化的效果,研發成本節約近70%,并縮短50%的開發周期。

核心器件――可重構主控制器EP2$30是通過可重構FPGA和DSP器件來連接信號采集與控制處理輸出部分,實現測控功能的控制中心通過CPCI總線與主控計算機進行數據交換的通道。基于SOPC的設計思想.使用Altera公司的NiosII處理器IP軟核及外圍邏輯編程實現主控制器功能。主控制器與CPCI控制器通過PCI局部總線交換指令和數據,通過自定義總線和DSP總線與FPGA和DSP交換采集和輸出數據。在系統重構模式下,主控制器通過CPCI控制器接收主機的重構指令和數據,對FPGA的配置存儲器和DSP的程序存儲器進行在線編程;同時也可以直接對FPGA進行在線并行加載,完成系統的硬件重構。在系統正常工作模式下,主控制器把從采集部分獲得的實時數據通過CPCI總線傳輸給主控計算機,或送往DSP進行數據處理并控制輸出。

對于數據采集模塊和控制輸出模塊,“可重構”的含義是指其模塊組成可以根據測控需要進行裁剪,例如可選用PAD模塊、基于FPGA實現的電動機轉速控制模塊、步進電機控制模塊等。

結 語

本文根據測控系統的通用結構模型和FPGA的可重構功能特點,提出了一種基于FPGA器件,針對嵌入式應用有效縮短開發周期和設計與應用成本,滿足并行性、多任務、開放化和集成化要求的RMS的平臺式設計思想,實現了測控系統“只能由廠家定義、設計,用戶只能使用”模式和“單任務”模式的突破。RMS技術在工業現場控制、城市市政管理、智能樓宇監控、智能家居等領域應用前景廣闊,在遠程重構和網絡測控方面亦有研究價值。

審核編輯:彭菁

-

FPGA

+關注

關注

1645文章

22034瀏覽量

617805 -

接口

+關注

關注

33文章

8991瀏覽量

153649 -

虛擬儀器

+關注

關注

23文章

777瀏覽量

88012 -

測控系統

+關注

關注

2文章

192瀏覽量

24131 -

軟硬件

+關注

關注

1文章

313瀏覽量

19679

發布評論請先 登錄

FPGA的重構方式

MPU+FPGA結構的可重構系統的結構特

可重構設計的測控站監控系統研究與實現

可重構技術分析及動態可重構系統設計

基于FPGA硬件平臺的可重構系統調度算法詳解

評論