今天我們要介紹的時序分析命令是 uncertainty ,簡稱時鐘不確定性。主要用來定義Clock信號到時序器件的Clock端可能早到或晚到的時間,降低了時鐘抖動jitter對有效時鐘周期的影響。

值得注意的是,在setup check中,clock uncertainty是代表著降低了時鐘的有效周期;而在hold check中,clock uncertainty是代表著hold check所需要滿足的額外margin。

來看下面一條reg2reg path. 對照著如下時鐘波形圖。可以寫出下面的約束。

set_clock_uncertainty-from VIRTUAL_SYS_CLK -to SYS_CLK -hold 0.05

set_clock_uncertainty -from VIRTUAL_SYS_CLK -to SYS_CLK -setup 0.3

set_clock_uncertainty -from SYS_CLK -to CFG_CLK -hold 0.05

set_clock_uncertainty -from SYS_CLK -to CFG_CLK -setup 0.1

在pre-CTS的時候,我們將時鐘的不確定性設定為target的skew和jitter值之和來模擬真實的時鐘;而post-CTS之后,時鐘樹propagate delay已經確定,skew真實存在,所以uncertainty就是時鐘的真實抖動值。因此preCTS的target skew不能設置的太大或者太小,這樣會造成preCTS和postCTS的correlation不好。總結一下:

在pre-CTS中,

setup的clock uncertainty = jitter + clock tree skew

hold的clock uncertainty = clock tree skew

在post-CTS中,

setup的clock uncertainty = jitter

hold的clock uncertainty = 0

對于uncertainty的設置,每種工藝,或者每種設計來說,都不盡相同。一般來說,頻率較高的時鐘,我們可以設置相對較小的clock uncertainty;而頻率較低的或者經過分頻的時鐘,我們可以把clock uncertainty加大一些。

對設計的不同階段,clock uncertainty的設置也不一樣,從design的initial階段,經過place, cts, route, extraction, signoff等步驟,每個階段都應該設置不同的clock uncertainty,給后續每個步驟預留margin,而且數值是越來越小的趨勢。

-

時序分析

+關注

關注

2文章

127瀏覽量

22569 -

CTS

+關注

關注

0文章

35瀏覽量

14117 -

時序分析器

+關注

關注

0文章

24瀏覽量

5280

發布評論請先 登錄

相關推薦

時序分析基本概念介紹<Operating Condition>

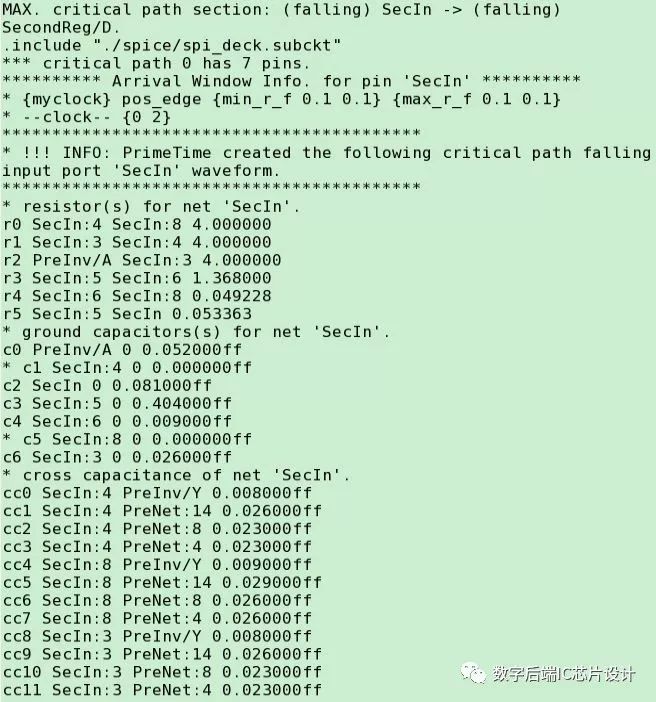

時序分析基本概念介紹&lt;spice deck&gt;

時序分析基本概念介紹&lt;generate clock&gt;

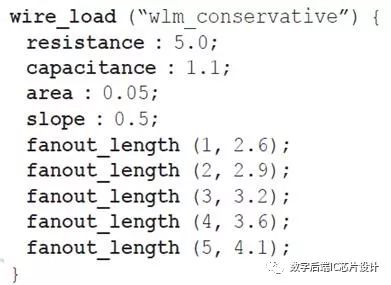

時序分析基本概念介紹&lt;wire load model&gt;

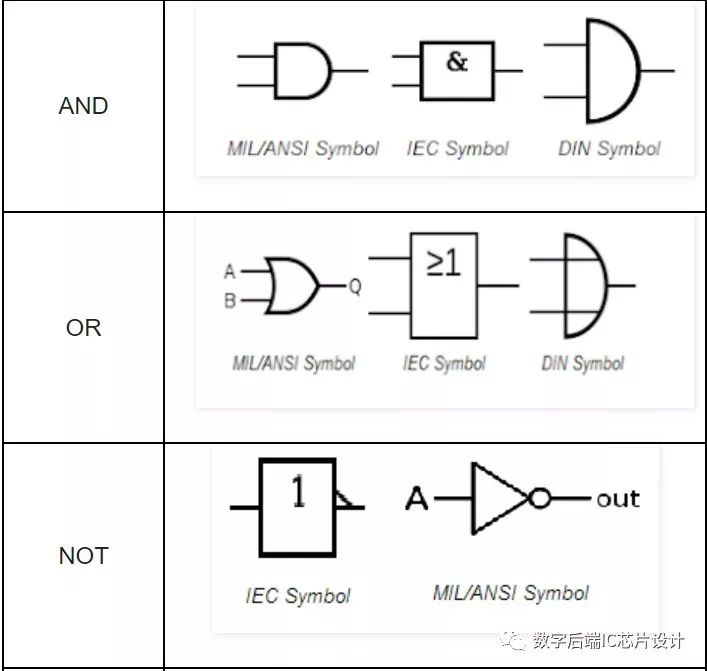

時序分析基本概念介紹&lt;Combinational logic&gt;

時序分析基本概念介紹<Uncertainty>

時序分析基本概念介紹<Uncertainty>

評論