筆者在校的科研任務,需要用FPGA搭建OFDM通信系統,而OFDM的核心即是IFFT和FFT運算,因此本文通過Xilinx FFT IP核的使用總結給大家開個頭,詳細內容可查看官方文檔PG109。

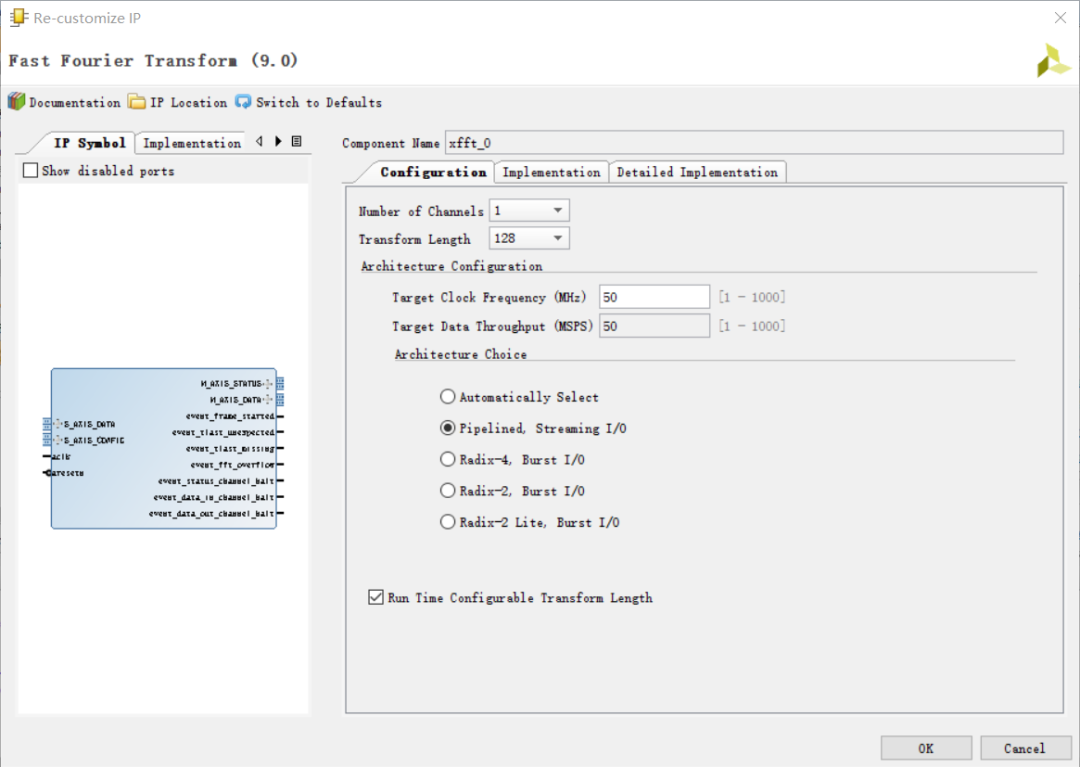

我們直接來看看FFT IP核配置界面:

由于OFDM接收機中大多是數據串并轉換后的連續低速并行數據流輸入FFT,故這里采用流水線結構。之后根據OFDM子載波數選擇變換長度。該IP核僅支持50MHZ采樣率數據的流水線處理,如果數高速通信場合,可以再次將數據串并轉換用多個FFT IP核并行運算,也就是FPGA設計中常用的“面積換速度”。

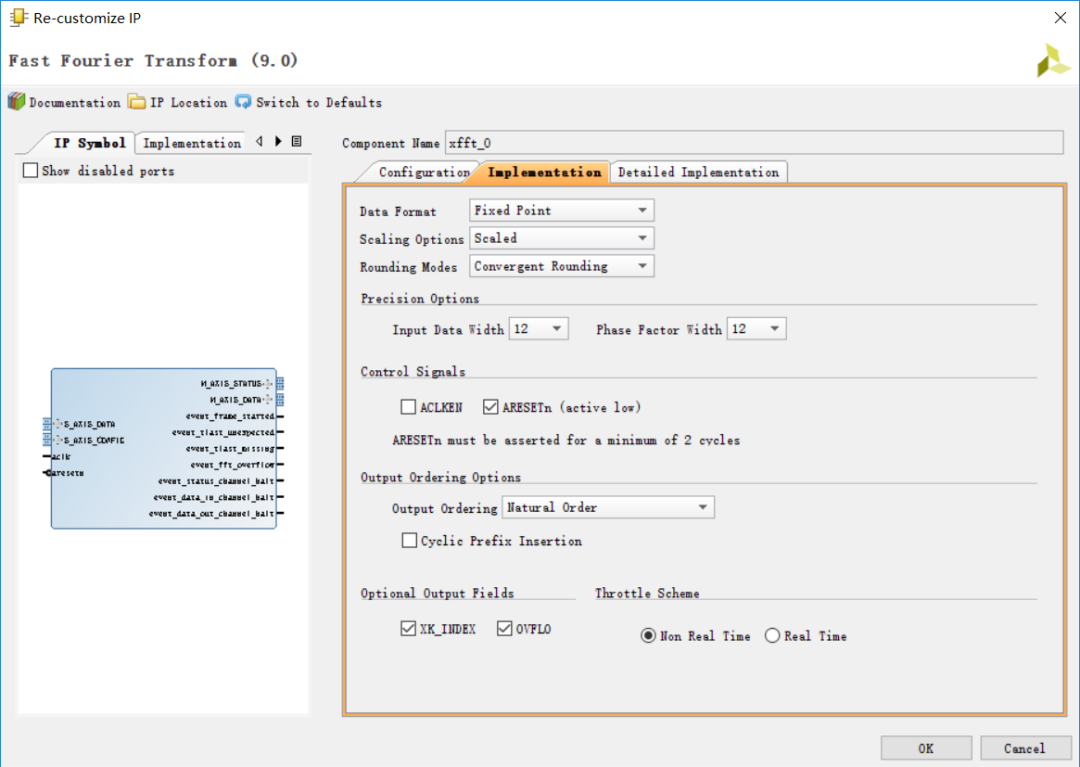

第二頁中比較重要的是選擇數據格式和縮減 截斷處理。此IP核支持浮點運算,但隨之會消耗大量的硬件資源,且延遲也較大,所以多采用定點運算方式。定點運算中固定的bit位寬很容易出現數據溢出,在蝶形運算過程中僅保留高位而整體右移可把計算過程中增加的位寬去除掉,最后再左移即可,顯然這種做法是在犧牲計算精度來降低硬件資源。設置Scaling Options為Scaled則在FFT IP核配置通道可以自定義縮減因子。當設置縮減位寬后,選中本頁左下角的OVFLO溢出信號,仿真過程中可以通過溢出信號確定合適的縮減因子。

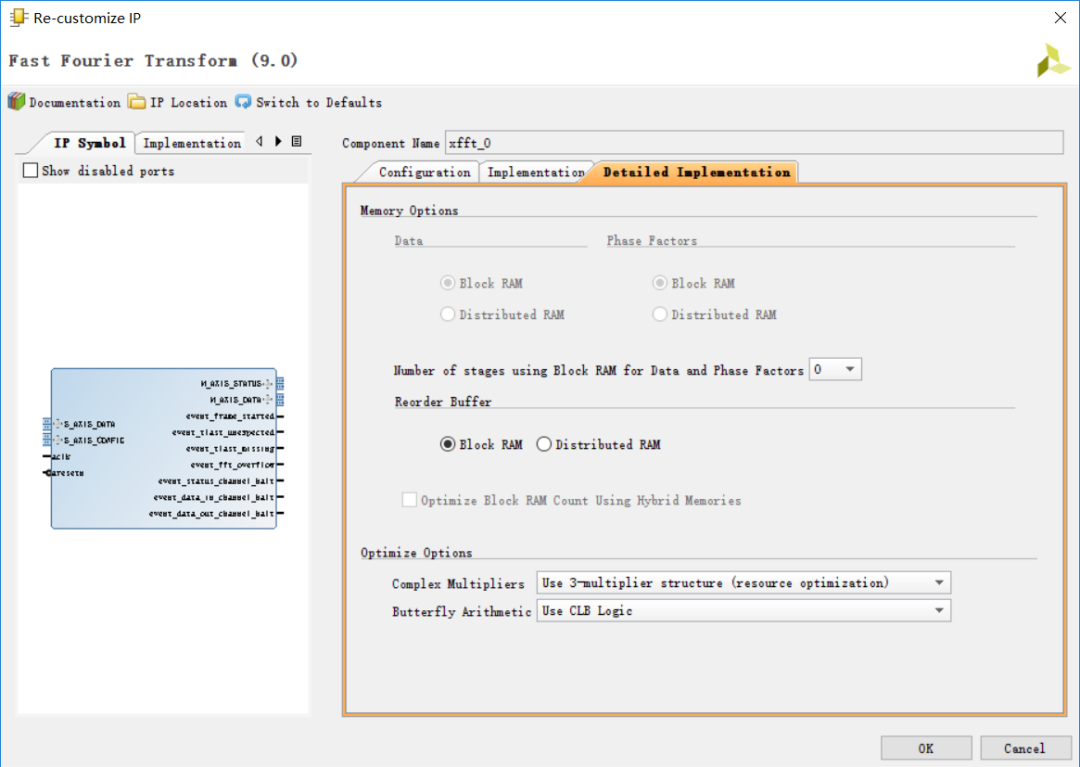

第三頁主要是設置底層資源,對功能沒有多大影響。存儲部分可以用BRAM和DRAM兩種資源,這里普及下:兩者主要的區別在于BRAM是FPGA內部專用的硬件存儲資源,用不用都在那里(你見或者不見,我就在那里,不來不去。。。好像在哪里見過),而DRAM是利用SLICEM中的LUT搭建出來的,相當于是BRAM的補充。在存儲量較小時,DRAM可能會表現出更好的功耗和速率優勢。正如官方文檔介紹的,在變換長度小于1024,即占用存儲資源少的情況下可使用DRAM。而下面的Optimize Options則可以權衡使用CLB和DSP Slices。

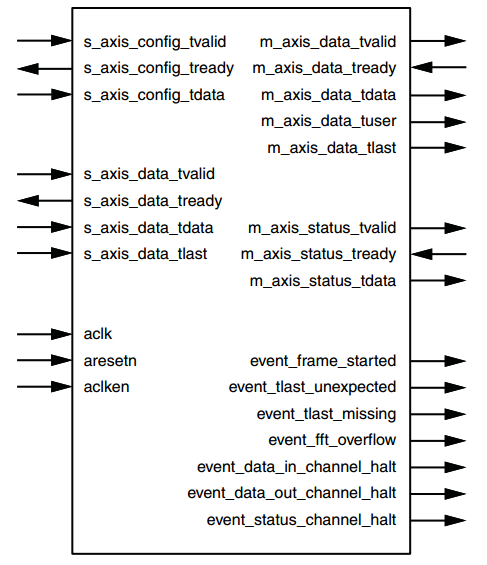

接口和配置可以說是所有IP核使用的重中之重。

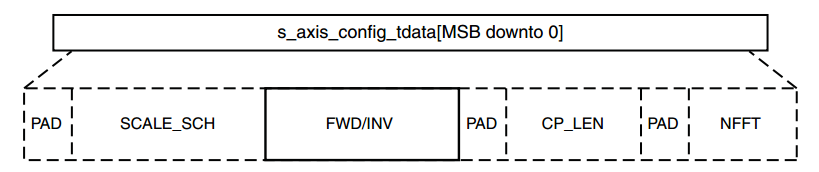

AXI總線的統一封裝給IP核調用帶來了很多方便,各部分功能通道相互分開結構非常清晰。每個通道的data以字節為單位的packet傳輸信息,如config通道信息如下:

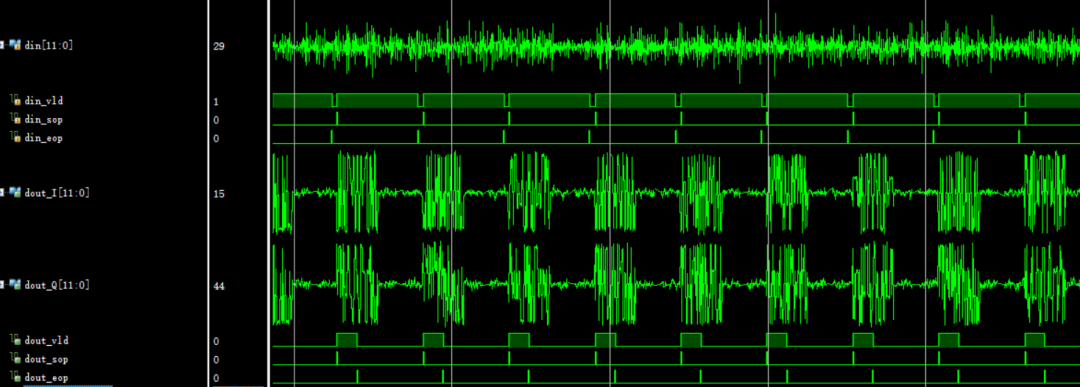

在這一通道中要在數據進入前設置好變換方式和縮減因子,此處配置為正變換,縮減因子[1 1 1 1]。給大家看下OFDM接收機工程中FFT運算部分的仿真波形圖:

din是DD-OFDM ADC 接收數據,只有一路實部信號。dout_I,dout_Q分別是FFT運算后復數中的實部和虛部。顯然FFT運算后得到了信號的不同頻率成分,下面的dout_vld負責提取赫比特對稱中數據載波。希望本文能起到拋磚引玉的作用,歡迎交流~

審核編輯:湯梓紅

-

FPGA

+關注

關注

1629文章

21729瀏覽量

603007 -

ofdm

+關注

關注

6文章

349瀏覽量

57001 -

Xilinx

+關注

關注

71文章

2167瀏覽量

121305 -

FFT

+關注

關注

15文章

434瀏覽量

59366 -

通信系統

+關注

關注

6文章

1187瀏覽量

53328

原文標題:從Xilinx FFT IP核到FPGA實現OFDM

文章出處:【微信號:Hack電子,微信公眾號:Hack電子】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

adc采樣后數據無法實現ofdm(fft)解調

基于FPGA的FFT和IFFT IP核應用實例

【Mill】Xilinx ip FFT變換,為什么你的matlab數據無法嚴格比對?——無線通信連載

通過Xilinx FFT IP核的使用實現OFDM

從Xilinx FFT IP核到FPGA實現OFDM

從Xilinx FFT IP核到FPGA實現OFDM

評論