本系列將帶來FPGA的系統(tǒng)性學習,從最基本的數(shù)字電路基礎開始,最詳細操作步驟,最直白的言語描述,手把手的“傻瓜式”講解,讓電子、信息、通信類專業(yè)學生、初入職場小白及打算進階提升的職業(yè)開發(fā)者都可以有系統(tǒng)性學習的機會。

系統(tǒng)性的掌握技術(shù)開發(fā)以及相關(guān)要求,對個人就業(yè)以及職業(yè)發(fā)展都有著潛在的幫助,希望對大家有所幫助。后續(xù)會陸續(xù)更新 Xilinx 的 Vivado、ISE 及相關(guān)操作軟件的開發(fā)的相關(guān)內(nèi)容,學習FPGA設計方法及設計思想的同時,實操結(jié)合各類操作軟件,會讓你在技術(shù)學習道路上無比的順暢,告別技術(shù)學習小BUG卡破腦殼,告別目前忽悠性的培訓誘導,真正的去學習去實戰(zhàn)應用。話不多說,上貨。

SPI 協(xié)議驅(qū)動設計

本篇實現(xiàn)基于叁芯智能科技的SANXIN -B01 FPGA開發(fā)板,以下為配套的教程,如有入手開發(fā)板,可以登錄官方淘寶店購買,還有配套的學習視頻。SANXIN-B01 Verilog教程-郝旭帥團隊

SPI是串行外設接口(Serial Peripheral Interface)的縮寫。SPI,是一種高速的,全雙工,同步的通信總線,并且在芯片的管腳上只占用四根線,節(jié)約了芯片的管腳,同時為PCB的布局上節(jié)省空間,提供方便,正是出于這種簡單易用的特性,如今越來越多的芯片集成了這種通信協(xié)議。

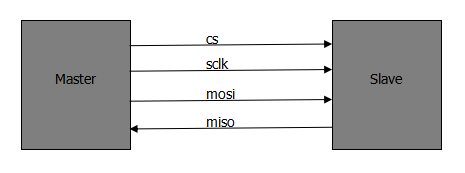

SPI的通信原理很簡單,它以主從方式工作,這種模式通常有一個主設備和一個或多個從設備,中間靠三線或者四線連接(三線時為單向傳輸或者數(shù)據(jù)線雙向傳輸)。所有基于SPI的設備共有的,它們是MISO、MOSI、SCLK、CS。

MISO– Master Input Slave Output,主設備數(shù)據(jù)輸入,從設備數(shù)據(jù)輸出。

MOSI– Master Output Slave Input,主設備數(shù)據(jù)輸出,從設備數(shù)據(jù)輸入。

SCLK – Serial Clock,時鐘信號,由主設備產(chǎn)生。

CS – Chip Select,從設備使能信號,由主設備控制。

cs是從芯片是否被主芯片選中的控制信號,也就是說只有片選信號為預先規(guī)定的使能信號時(高電位或低電位),主芯片對此從芯片的操作才有效。這就使在同一條總線上連接多個spi設備成為可能。

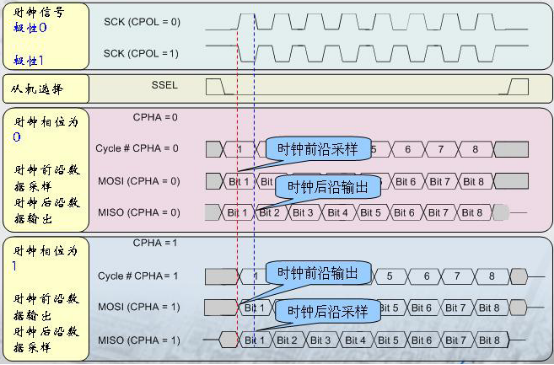

通訊是通過數(shù)據(jù)交換完成的,由sclk提供時鐘脈沖,mosi、miso則基于此脈沖完成數(shù)據(jù)傳輸。數(shù)據(jù)輸出通過 mosi線,數(shù)據(jù)在時鐘上升沿或下降沿時改變,在緊接著的下降沿或上升沿被讀取。完成一位數(shù)據(jù)傳輸,輸入也使用同樣原理。因此,至少需要N次時鐘信號的改變(上沿和下沿為一次),才能完成N位數(shù)據(jù)的傳輸。

spi通信有四種不同的模式,不同的從設備可能在出廠時就已經(jīng)配置為某種模式。通信的雙方必須是工作在同一模式下,所以我們可以對主設備的spi模式進行配置,通過CPOL(時鐘極性)和CPHA(時鐘相位)來控制我們主設備的通信模式。

mode0:CPOL=0,CPHA=0;

mode1:CPOL=0,CPHA=1;

mode2:CPOL=1,CPHA=0;

mode3:CPOL=1,CPHA=1;

時鐘極性CPOL是用來配置SCLK在空閑時,應該處于的狀態(tài);時鐘相位CPHA用來配置在第幾個邊沿進行采樣。

CPOL=0,表示在空閑狀態(tài)時,時鐘SCLK為低電平。

CPOL=1,表示在空閑狀態(tài)時,時鐘SCLK為高電平。

CPHA=0,表示數(shù)據(jù)采樣是在第1個邊沿。

CPHA=1,表示數(shù)據(jù)采樣是在第2個邊沿。

即:

CPOL=0,CPHA=0:此時空閑態(tài)時,SCLK處于低電平,數(shù)據(jù)采樣是在第1個邊沿,也就是SCLK由低電平到高電平的跳變,所以數(shù)據(jù)采樣是在上升沿,數(shù)據(jù)發(fā)送是在下降沿。

CPOL=0,CPHA=1:此時空閑態(tài)時,SCLK處于低電平,數(shù)據(jù)發(fā)送是在第1個邊沿,也就是SCLK由低電平到高電平的跳變,所以數(shù)據(jù)采樣是在下降沿,數(shù)據(jù)發(fā)送是在上升沿。

CPOL=1,CPHA=0:此時空閑態(tài)時,SCLK處于高電平,數(shù)據(jù)采集是在第1個邊沿,也就是SCLK由高電平到低電平的跳變,所以數(shù)據(jù)采集是在下降沿,數(shù)據(jù)發(fā)送是在上升沿。

CPOL=1,CPHA=1:此時空閑態(tài)時,SCLK處于高電平,數(shù)據(jù)發(fā)送是在第1個邊沿,也就是SCLK由高電平到低電平的跳變,所以數(shù)據(jù)采集是在上升沿,數(shù)據(jù)發(fā)送是在下降沿。

硬件簡介

FLASH閃存 的英文名稱是"Flash Memory",一般簡稱為"Flash",它屬于內(nèi)存器件的一種,是一種非易失性( Non-Volatile )內(nèi)存。

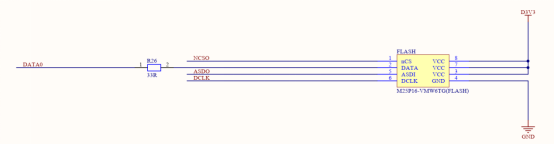

在開發(fā)板上有一塊flash(M25P16),用來保存FPGA的硬件配置信息,也可以用來存儲用戶的應用程序或數(shù)據(jù)。

M25P16是一款帶有寫保護機制和高速SPI總線訪問的2M字節(jié)串行Flash存儲器,該存儲器主要特點:2M字節(jié)的存儲空間,分32個扇區(qū),每個扇區(qū)256頁,每頁256字節(jié);能單個扇區(qū)擦除和整片擦除;每扇區(qū)擦寫次數(shù)保證10萬次、數(shù)據(jù)保存期限至少20年。

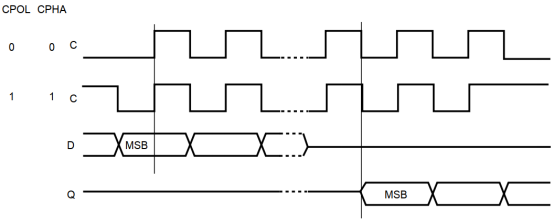

C(serial clock:串行時鐘)為D和Q提供了數(shù)據(jù)輸入或者輸出的時序。D的數(shù)據(jù)總是在C的上升沿被采樣。Q的數(shù)據(jù) 在C的下降沿被輸出。

ˉS(Chip Select:芯片選擇端),當輸入為低時,該芯片被選中,可以允許進行讀寫操作。當輸入為高時,該芯片被釋放,不能夠進行操作。

對于H——o——l——d——和W——, 為保持功能和硬件寫保護功能,在本設計中不使用此管腳,在硬件設計時,這兩個管腳全部被拉高了,即全部失效。

flash采用spi的通信協(xié)議,flash當做從機。serial clcok等效于spi中的sclk,chip select等效于spi中的cs,D等效于spi中的mosi,Q等效于spi中的miso。

flash可以支持mode0和mode3,這兩種模式中,都是在時鐘的上升沿采樣,在時鐘的下降沿發(fā)送數(shù)據(jù)。

flash的每一頁都可以被寫入,但是寫入只能是把1改變?yōu)?。擦除可以把0改變?yōu)?。所以在正常寫入數(shù)據(jù)之前,都要將flash進行擦除。

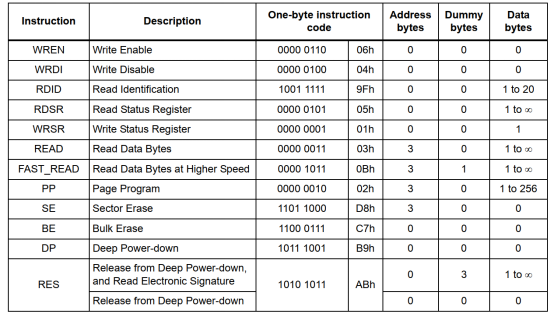

flash的命令表如下:

下面介紹幾個常用的命令

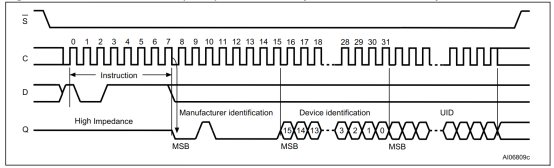

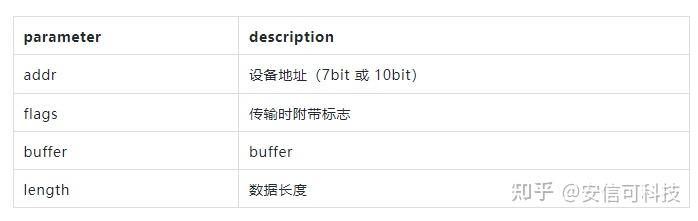

RDID(Read Identification :讀ID):發(fā)送命令RDID(9F),然后接收第1個字節(jié)的memory type(20H),第二個字節(jié)的memory capacity(15H)。后續(xù)的字節(jié)暫不關(guān)心。

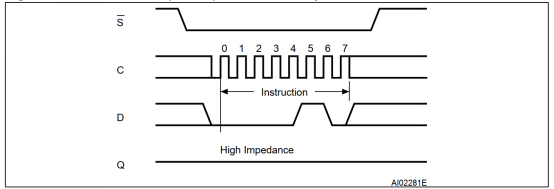

WREN(Write Enable :寫使能):在任何寫或者擦除的命令之前,都必須首先打開寫使能。打開寫使能為發(fā)送命令WREN(06h)。

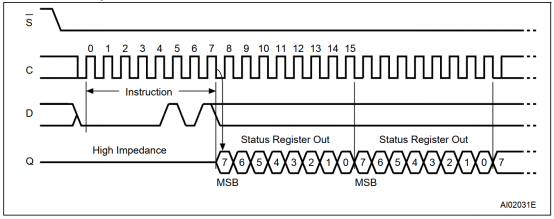

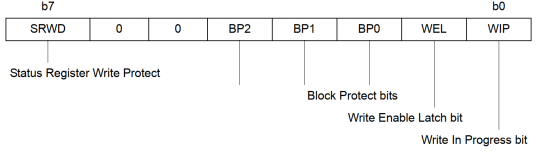

RDSR(Read Status Register:讀狀態(tài)寄存器):發(fā)送命令RDSR(05h),然后返回一個字節(jié)的狀態(tài)值。

狀態(tài)寄存器的格式如下:

WIP(Write In Progress bit)表示flash內(nèi)部是否正在進行內(nèi)部操作,寫和擦除都會導致flash內(nèi)部進行一段時間的工作,在內(nèi)部工作期間,外部的命令會被忽略,所以在進行任何命令之前,都需要查看flash內(nèi)部是否正在工作。WIP為1時,表示flash內(nèi)部正在工作;WIP為0時,表示flash內(nèi)部沒有在工作。

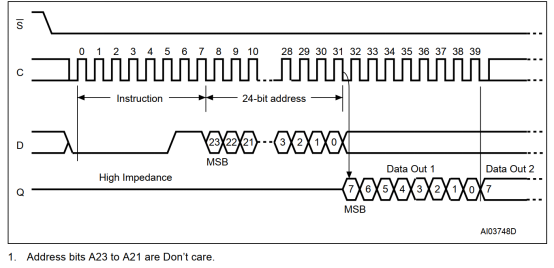

READ(Read DATA Bytes:讀數(shù)據(jù)):發(fā)送命令READ(03H),后續(xù)發(fā)送3個字節(jié)的地址,然后就可以接收數(shù)據(jù),內(nèi)部的地址會不斷遞增。一個讀命令就可以把整個flash全部讀完。

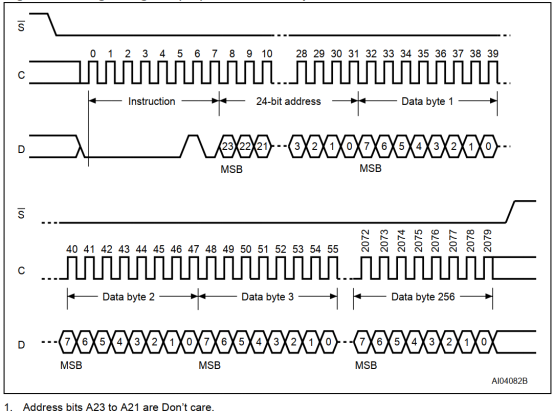

PP(Page Program :頁編寫):發(fā)送命令PP(02H),接著發(fā)送3個字節(jié)的地址,然后發(fā)送數(shù)據(jù)即可。切記所寫的數(shù)據(jù)不能超過本頁的地址范圍。

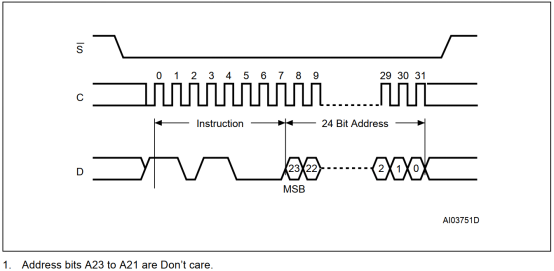

SE(Sector Erase :扇區(qū)擦除):發(fā)送命令SE(D8H),接著發(fā)送3個字節(jié)的地址。

BE(Bulk Erase:整片擦除):發(fā)送命令BE(C7H)。

關(guān)于flash的其他的介紹,可以參考03_芯片手冊->FLASH->M25P16.pdf。

設計要求

設計flash(M25P16)控制器。

設計分析

根據(jù)M25P16的數(shù)據(jù)手冊得知,其接口為spi接口,且支持模式0和模式3,本設計中選擇模式0。

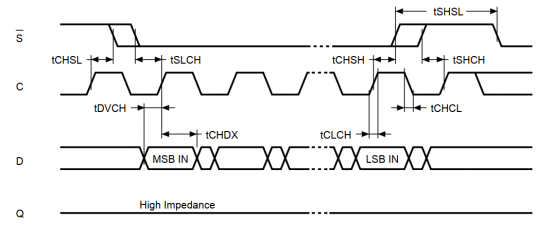

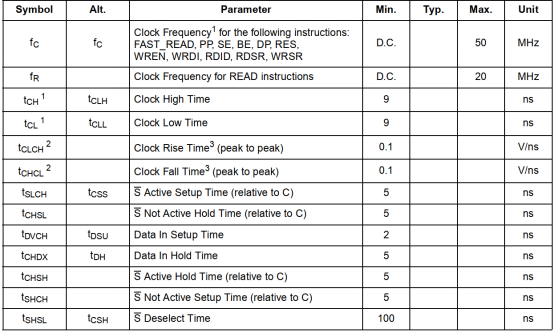

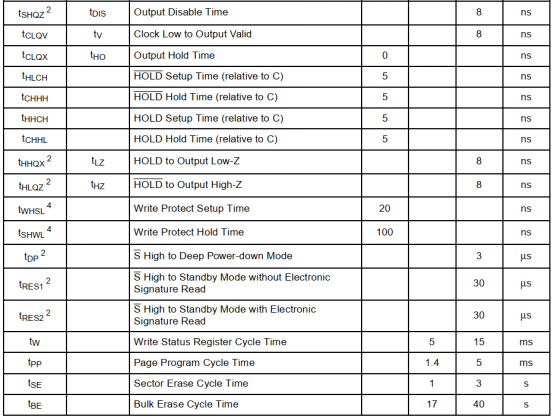

輸入時序圖如下:

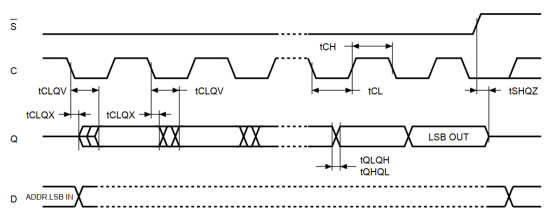

輸出時序如下:

時序圖中所對應的符號說明:

根據(jù)輸入和輸出的時序圖以及參數(shù)表,將SPI的時鐘的頻率定為10MHz。

在設計中,F(xiàn)PGA作為主機,M25P16作為從機。

架構(gòu)設計和信號說明

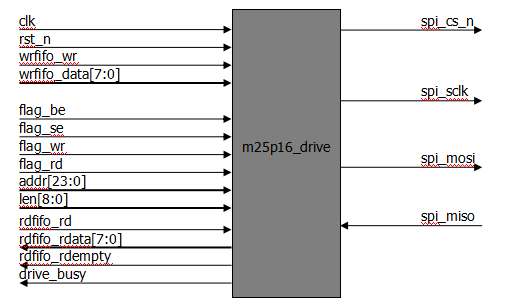

此模塊命名為m25p16_drive。

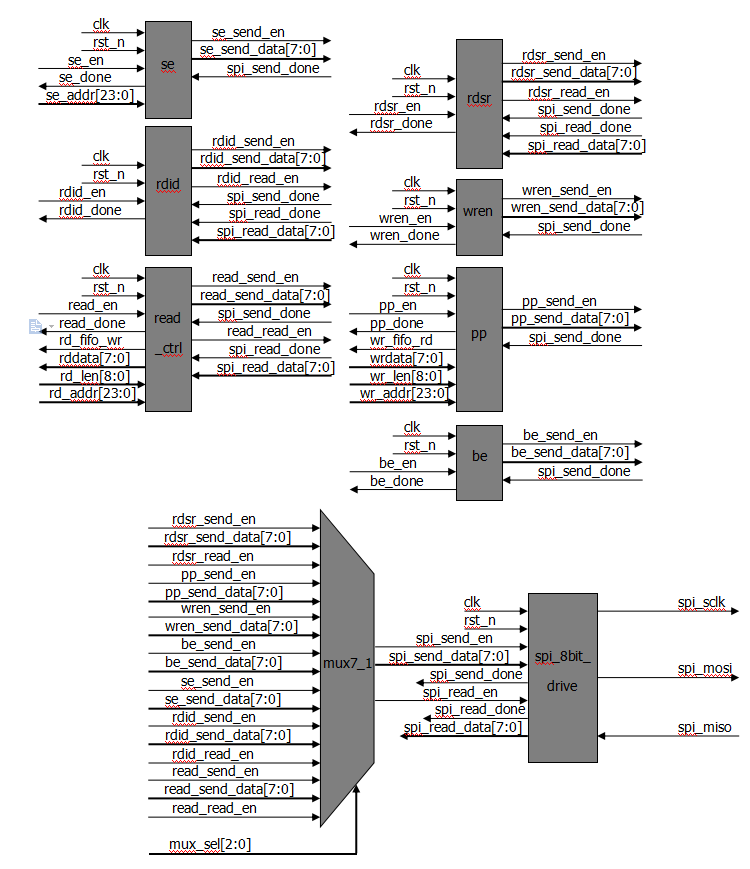

二級模塊(分模塊)(第一頁)

二級模塊(分模塊)(第二頁)

設計中,各個命令單獨寫出控制器,通過多路選擇器選擇出對應的命令,然后控制spi_8bit_drive將數(shù)據(jù)按照spi的協(xié)議發(fā)送出去。各個命令的脈沖通過ctrl模塊進行控制各個命令控制器,寫入的數(shù)據(jù)首先寫入到寫緩沖區(qū),讀出的數(shù)據(jù)讀出后寫入到讀緩沖區(qū)。

暫不分配的端口,在應用時都是由上游模塊進行控制,本設計測試時,編寫上游模塊進行測試。

各個模塊的功能,和連接線的功能在各個模塊設計中說明。

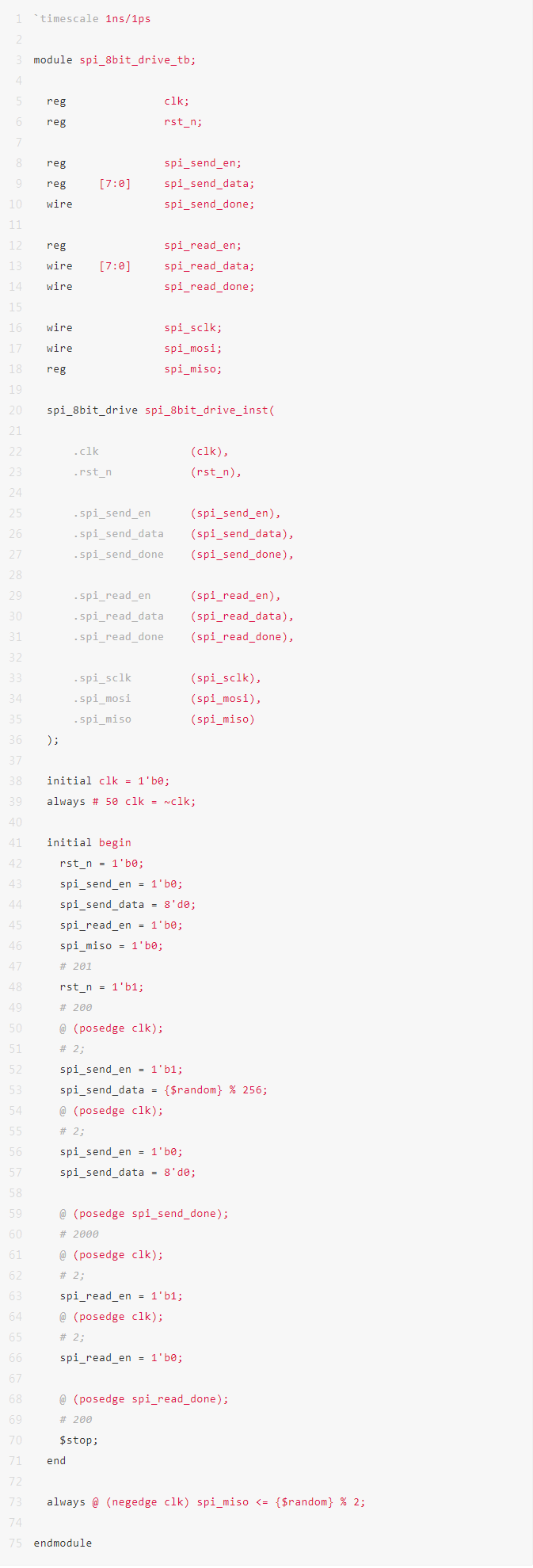

spi_8bit_drive設計實現(xiàn)

本模塊負責將8bit的并行數(shù)據(jù)按照spi協(xié)議發(fā)送出去,以及負責按照spi協(xié)議接收數(shù)據(jù),將接收的數(shù)據(jù)(8bit)并行傳輸給各個模塊。

spi_send_en為發(fā)送數(shù)據(jù)使能信號(脈沖信號),spi_send_data為所要發(fā)送數(shù)據(jù),spi_send_done為發(fā)送完成信號(脈沖信號)。

spi_read_en為接收數(shù)據(jù)使能信號(脈沖信號),spi_read_data為所接收的數(shù)據(jù),spi_read_done為接收完成信號(脈沖信號)。

在發(fā)送邏輯控制中,全部的信號采用下降沿驅(qū)動。利用外部給予的spi_send_en作為啟動信號,啟動send_cnt。send_cnt在不發(fā)送數(shù)據(jù)時為8,發(fā)送數(shù)據(jù)時,從0到7。

在接收邏輯中,全部的信號采用上升沿驅(qū)動。利用外部給予的spi_read_en作為啟動信號,啟動rec_en,經(jīng)過移位接收數(shù)據(jù)。

在spi_sclk輸出時,采用組合邏輯。由于設計采用spi的模式0,故而spi_sclk不發(fā)送或者接收數(shù)據(jù)時為0,接收數(shù)據(jù)時為時鐘信號。因為要求為模式0,所以在接收數(shù)據(jù)時,spi_sclk的輸出不能夠先有下降沿,即要求spi_sclk的控制信號不能由上升沿信號驅(qū)動,所以將rec_en同步到下降沿的rec_en_n。

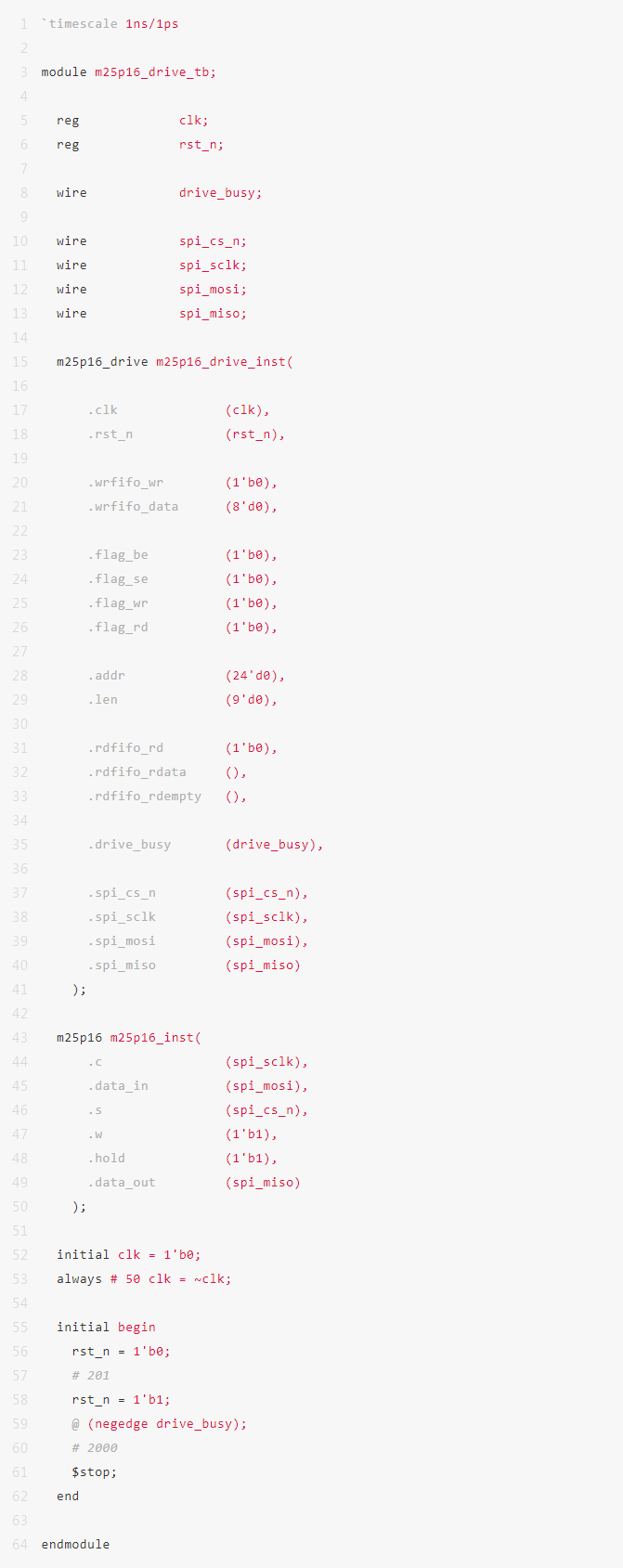

仿真代碼為:

在仿真中,將時鐘設置為10MHz。

所有的信號采用上升沿驅(qū)動。發(fā)送一個8bit的隨機數(shù)值,接收一個8bit的隨機數(shù)值。

spi_miso信號為從機下降沿驅(qū)動信號。

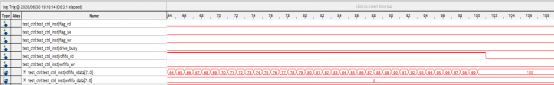

通過RTL仿真,可以看出發(fā)送和接收全部正常。

mux7_1設計實現(xiàn)

本模塊負責將7個命令模塊發(fā)出的命令(寫使能、寫數(shù)據(jù)和讀使能)經(jīng)過選擇發(fā)送給spi_8bit_drive模塊。

在設計中,有的命令模塊不需要進行讀取(pp和se等等),此時將輸出的讀使能信號輸出為低電平。

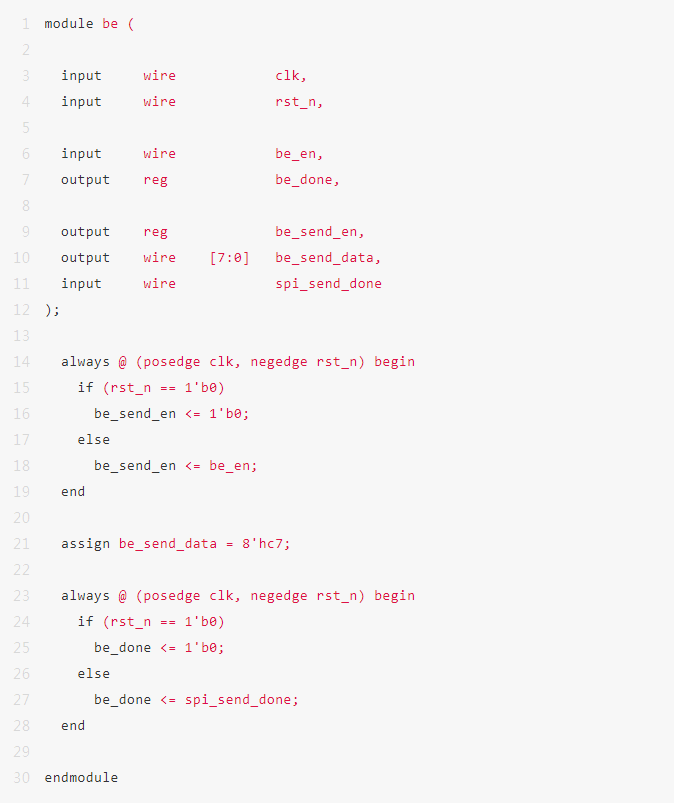

be設計實現(xiàn)

該模塊接收到be_en(整片擦除的脈沖信號)信號后,發(fā)送對應的使能和數(shù)據(jù),等待發(fā)送完成脈沖。發(fā)送完成后,輸出擦除完成的脈沖。

整片擦除的命令為8’hc7。

wren設計實現(xiàn)

該模塊接收到wren_en(打開flash內(nèi)部的寫使能的脈沖信號)信號后,發(fā)送對應的使能和數(shù)據(jù),等待發(fā)送完成脈沖。發(fā)送完成后,輸出擦除完成的脈沖。

打開flash內(nèi)部寫使能的命令碼為8’h06。

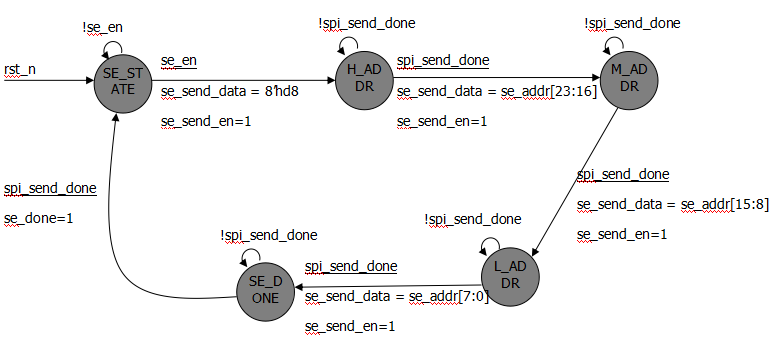

se設計實現(xiàn)

該模塊接收到se_en(擦除扇區(qū)的寫使能的脈沖信號)信號后,發(fā)送對應的使能和數(shù)據(jù),等待發(fā)送完成脈沖。發(fā)送完成后,接著發(fā)送高八位地址,中間八位地址和低八位地址。全部發(fā)送完成后,發(fā)送se_done信號。

該模塊采用狀態(tài)機實現(xiàn)。SE_STATE(扇區(qū)擦除命令發(fā)送)、H_ADDR(高八位地址發(fā)送)、M_ADDR(中間八位地址發(fā)送)、L_ADDR(低八位地址發(fā)送)、SE_DONE(扇區(qū)擦除完成)。所有的脈沖信號在未標注的時刻,輸出全部為0。

設計代碼為:

在發(fā)送過程中,由于是每8bit發(fā)送一次,所以在時序上將看到發(fā)送時,每8個脈沖一組,中間會有明顯的間隔。

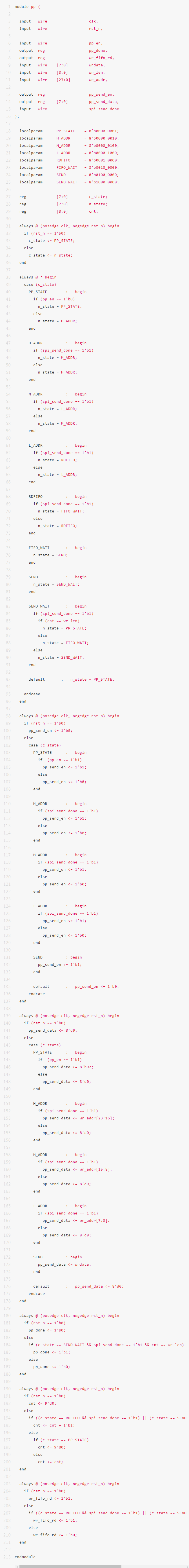

pp設計實現(xiàn)

該模塊負責將外部寫fifo中的數(shù)據(jù)寫入到flash中。wr_fifo_rd為寫fifo的讀使能信號,wrdata為從寫fifo中讀出的數(shù)據(jù),wr_len為需要寫入flash中數(shù)據(jù)的長度,wr_addr為寫入地址。

該模塊采用狀態(tài)機實現(xiàn)。PP_STATE(發(fā)送pp命令),H_ADDR(發(fā)送高八位地址)、M_ADDR(發(fā)送中間八位地址),L_ADDR(發(fā)送低八位地址)、RDFIFO(讀寫fifo)、FIFO_WAIT(等待讀寫fifo的數(shù)據(jù)輸出)、SEND(發(fā)送8bit數(shù)據(jù))、SEND_WAIT(發(fā)送等待,發(fā)送完成后判斷是否發(fā)送完成)。對于所有的脈沖信號,沒有賦值的位置,全部賦值為0。

cnt為記錄已經(jīng)發(fā)送的數(shù)據(jù)個數(shù)。

設計代碼為:

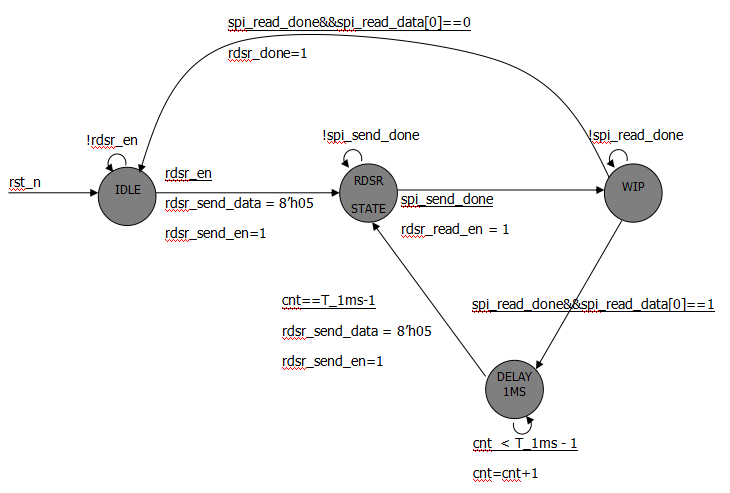

rdsr設計實現(xiàn)

本模塊的功能為讀取m25p16的狀態(tài)寄存器,主要檢測狀態(tài)寄存器的最低位(WIP)。

WIP(write in progress :正在進行寫進程),該bie位表示了flash內(nèi)部是否在進行寫進程。如果處于寫進程時,flash忽略外部所有的命令,所以建議在執(zhí)行任何命令前,首先進行檢測該位。1表示正在寫進程中,0表示不處于寫進程。

如果檢測到正在寫進程中,進行延遲1ms,然后再次讀取該位狀態(tài)。直到寫進程結(jié)束。

本模塊采用狀態(tài)機設計實現(xiàn)。ILDE(發(fā)送讀狀態(tài)寄存器命令)、RDSRSTATE(發(fā)送讀使能)、WIP(判斷wip位)、 DELAY1ms(延遲1ms)。cnt為延遲1ms的計數(shù)器。

設計代碼為:

rdid設計實現(xiàn)

該模塊負責讀取flash的ID(2015),驗證ID的正確性。

該模塊采用狀態(tài)機的方式實現(xiàn)。IDLE(等待讀取ID的命令)、IDSTATE1(讀取高八位ID)、IDSTATE2(讀取中間八位ID)、IDSTATE3(讀取低八位ID)、ID_CHECK(檢測ID的正確性)。

狀態(tài)轉(zhuǎn)移圖如下:

設計代碼為:

read_ctrl設計實現(xiàn)

該模塊負責將flash的數(shù)據(jù)讀出,寫入到輸出緩存中。

該模塊采用狀態(tài)機實現(xiàn)。RD_STATE(等待讀命令)、H_ADDR(發(fā)送高八位地址)、M_ADDR(發(fā)送中間八位地址)、L_ADDR(發(fā)送低八位地址)、RDDATA(讀取數(shù)據(jù))、WRFIFO(將讀出的數(shù)據(jù)寫入到FIFO中)、CHECK_LEN(判斷讀取的長度)。

狀態(tài)轉(zhuǎn)移圖如下:

設計代碼為:

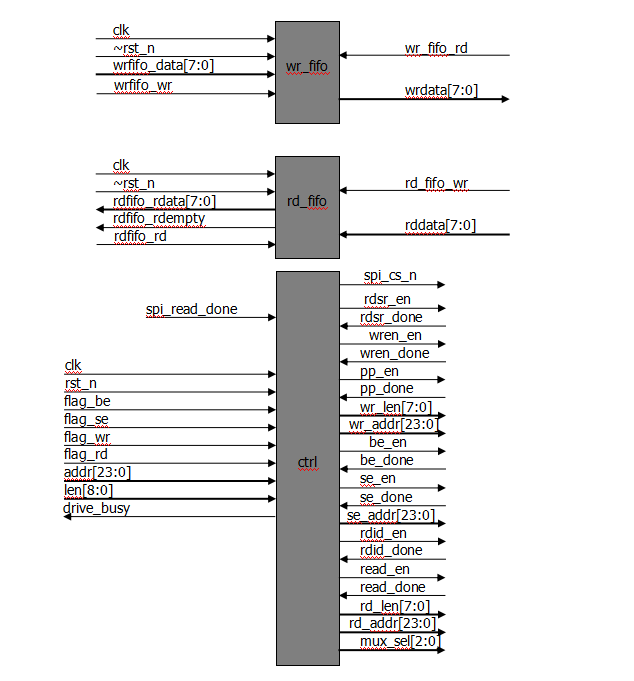

wr_fifo和rd_fifo調(diào)用

兩個fifo的寬度設置為8,深度設置為256,同步fifo,帶有復位。

ctrl設計實現(xiàn)

該模塊根據(jù)外部的命令,按照m25p16的執(zhí)行規(guī)則,進行控制各個模塊的執(zhí)行。

該模塊采用狀態(tài)機實現(xiàn)。INIT_RDSR(讀WIP),INIT_RDID(讀ID),INIT_ID(判斷ID),WIP(讀WIP),WIP_DONE(等待WIP),IDLE(空閑狀態(tài)),**STATE(執(zhí)行對應的命令),**WREN(打開flash的寫使能)。在進行任何命令前,都檢查wip。

狀態(tài)轉(zhuǎn)移圖如下:

在不同的狀態(tài),mux_sel選擇對應的命令通過。

drive_busy只有在IDLE狀態(tài)才是低電平。

spi_cs_n信號, DLE狀態(tài)為高電平、WIP_DONE(INIT_RDID)中spi_read_done信號為高時 (保證能夠多次讀取狀態(tài)寄存器)、在其他狀態(tài)發(fā)生切換時,spi_cs_n 為高電平,否則為低電平。

設計代碼為:

m25p16_drive設計實現(xiàn)

本模塊負責連接所有二級模塊,實現(xiàn)所有的功能。

RTL仿真

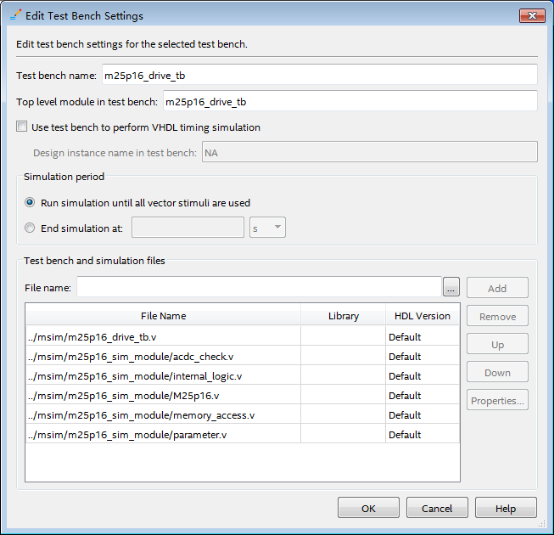

本次設計涉及到讀取flash的id以及狀態(tài)寄存器,所以在仿真時需要加入仿真模型。仿真模型放在msim的m25p16_sim_module中。m25p16為仿真模型的頂層文件。

由于讀寫和擦除的時間較長,RTL仿真中,將只仿真RDSR和RDID,其他的功能測試在板級測試時進行。

仿真代碼如下:

在設置testbench時,注意將所有文件全部添加到文件中。

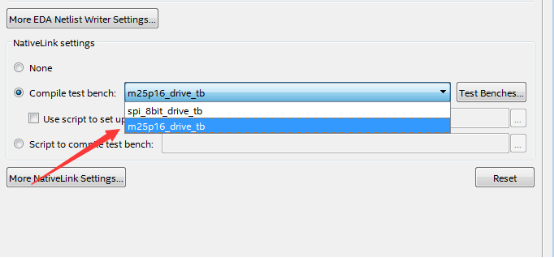

選擇testbench時,注意選中設置的m25p16_drive_tb。

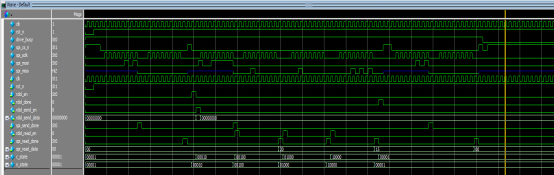

利用modelsim仿真,可以得出如下RTL仿真波形。

讀到ID,以及檢測WIP都是正確的。

板級測試

由于m25p16的時序原因,整個設計工作在10MHz(利用PLL產(chǎn)生)。

在進行測試控制時,對最后一個扇區(qū)進行擦除;對最后一個扇區(qū)的第一頁進行寫入數(shù)據(jù)100個(1至100);對最后一個扇區(qū)的第一個進行讀取,驗證數(shù)據(jù)是否為1至100。

測試的控制模塊命名為test_ctrl。

此模塊采用狀態(tài)機實現(xiàn)。WRFIFO(將1至100寫入wrfifo中)、SE(扇區(qū)擦除)、PP(寫入flash)、RD(讀出flash)、WAIT_RD(等待讀取)、CHECK( 檢測讀出的數(shù)據(jù)的正確性)。

設計代碼為:

將test模塊設置為頂層。在test模塊中,m25p16_drive例化中,對于整片擦除不做控制,對于addr直接指向最后一個扇區(qū)的第一頁,len指定為100。

代碼為:

由于開發(fā)板上的flash是為FPGA進行保存配置信息的,所以管腳都連接在專用管腳上,本次實驗需要將這專用管腳配置為普通io。

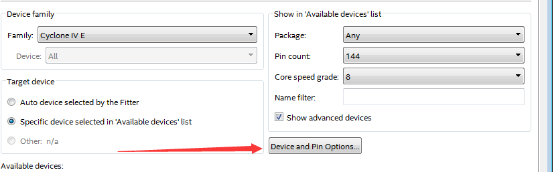

右擊器件型號,選擇device。

點擊device and pin options。

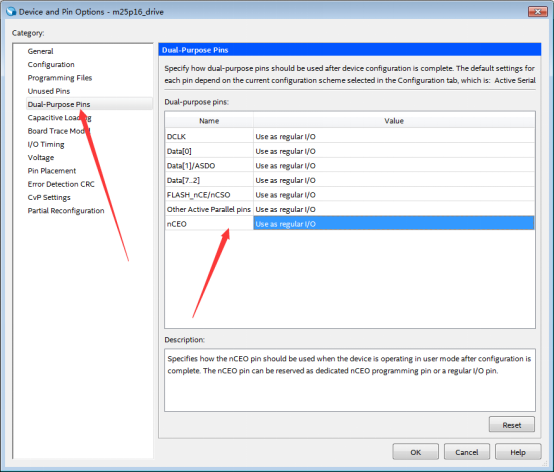

選擇Dual-purpose pins,將其中所有的功能改為普通IO。

點擊ok后,即可進行綜合分析。

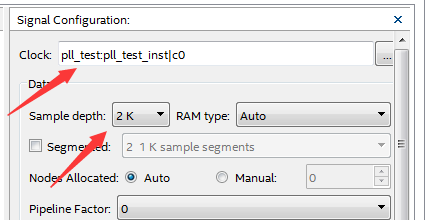

連接開發(fā)板和PC,打開邏輯分析儀。

采樣時鐘選擇10MHz(PLL 的c0),采樣深度設置為2K。

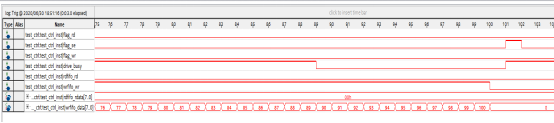

觀測信號如下圖所示。

首先將wrfifo_wr的觸發(fā)條件設置為上升沿。點擊觸發(fā)后,按下復位按鍵。觸發(fā)后,可以看到寫入數(shù)據(jù)1至100后,然后進行SE命令。

將rdfifo_rd的觸發(fā)條件設置為上升沿(將wrfifo_wr觸發(fā)條件修改為donot care)。點擊觸發(fā)后,按下復位按鍵。

通過仿真和下板實測,驗證控制器設計正確。

更多熱點文章閱讀

-

電子技術(shù)

+關(guān)注

關(guān)注

18文章

890瀏覽量

55979 -

電子發(fā)燒友論壇

+關(guān)注

關(guān)注

4文章

197瀏覽量

1086

原文標題:【教程分享】FPGA零基礎學習:SPI 協(xié)議驅(qū)動設計

文章出處:【微信號:gh_9b9470648b3c,微信公眾號:電子發(fā)燒友論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

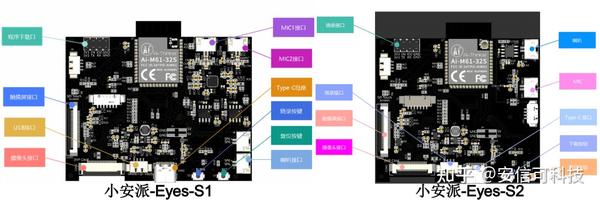

零基礎開發(fā)小安派-Eyes-S1外設篇——I2S

零基礎開發(fā)小安派-Eyes-S1【外設篇】——FLASH

零基礎開發(fā)小安派-Eyes-S1 外設篇 ——I2C

spi master接口的fpga實現(xiàn)

采用Xilinx FPGA的AFE79xx SPI啟動指南

【S32K146 RT-thread】之 SPI驅(qū)動適配

零基礎開發(fā)小安派-Eyes-S1外設篇——GPIO中斷編程

零基礎嵌入式開發(fā)學習路線

零基礎開發(fā)小安派-Eyes-S1外設篇——GPIO 輸入輸出

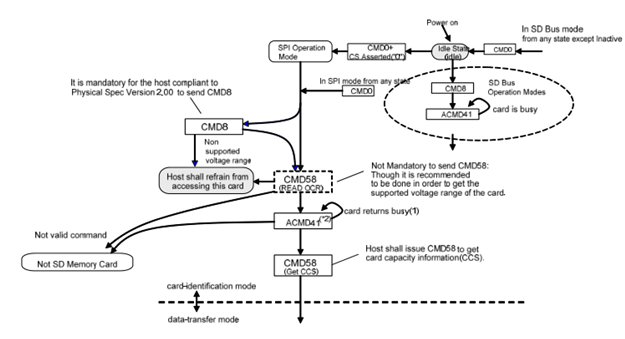

瀚海微SD NAND之SD 協(xié)議(36)SPI模式

FPGA做深度學習能走多遠?

從入門到放棄……為什么你會覺得FPGA難學?如何學習FPGA?

【教程分享】FPGA零基礎學習:SPI 協(xié)議驅(qū)動設計

【教程分享】FPGA零基礎學習:SPI 協(xié)議驅(qū)動設計

評論