對于下面這個傳輸門來說,只有當CLK為高電平,即傳輸門打開時,輸入端I的電平才會被傳輸到輸出端O,這是一個正常的傳輸過程。

不過,傳輸過程不是一蹴而就的,一方面,CLK的切換需要時間(也就是我們所說的transition time),另一方面,如果在傳輸門打開到關閉的切換過程中,I輸入的電壓也在變換,而在CLK關閉后,O的輸出剛好在高電平與低電平的一半,或者通俗一些說,剛好是0.5VDD。

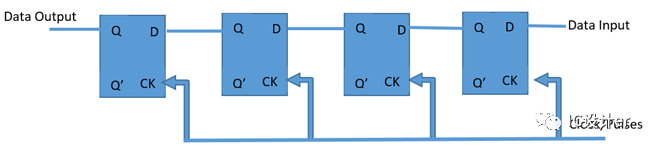

如果這種情況出現在寄存器的U2傳輸門上,會發生什么?沒錯了,D’只有0.5VDD,那么一級一級傳下去,D’’、Q’’、Q都是多少呢?

0.5VDD只是一個假設,實際上我們知道,對于CMOS傳輸曲線來說,當輸入端電壓處于一個較為穩定的接近于傳輸曲線中間位置,則輸出端Q會出現不穩定的狀態,我們就把這種情況稱之為寄存器出現了亞穩態。

那么亞穩態是X[2]嗎?亞穩態是中間態嗎?亞穩態輸出就一定是0.5VDD嗎?這些問題,在任何企業、學校都會有熱烈的討論。

實際上,亞穩態既然叫做亞穩態,那么就是可能因為周圍環境的不同,其輸出會向一個方向偏移,比如說電子偏多的時候,可能偏向于低電平,空穴偏多的時候,可能偏向于高電平[3]。但由于不是被VDD或地直接驅動,變化速度會偏慢,實際表現就和下面這幅圖一樣,原本應該一下就變化的,可能需要一個緩慢的變化過程。

寄存器的setup和hold時序概念

通過亞穩態部分的介紹,我們知道,當時鐘上升沿來到,并關閉輸入端第一級U2傳輸門時,如果D端發生數據變化,有可能導致Q端輸出產生亞穩態。

為了保證寄存器穩定工作,在設計電路時,需要滿足兩個時間窗口。

在時鐘上升沿來到前的一個時間段,數據必須建立完成,這個時間稱之為建立時間(setup time)。而在時鐘上升沿之后一個時間段,則需要保持住數據不變化,這個時間稱之為保持時間(hold time)。建立時間、保持時間與時鐘的關系如下圖所示。

現在大部分標準單元庫設計的寄存器都采用了0保持時間或負保持時間設計,也就是保持時間為0或為負數,當然這也在某種程度上增加了建立時間的時間窗大小,降低了系統工作頻率。好處是更容易幫助系統在各種不同的時序簽核(Timing sign-off)條件下,快速收斂,簡化了投片標準,加快了上市時間(Time to Market)。

在時序分析當中,還有一種路徑上的setup time與hold time概念,與寄存器的概念類似,但意思不同,千萬不要混淆了。

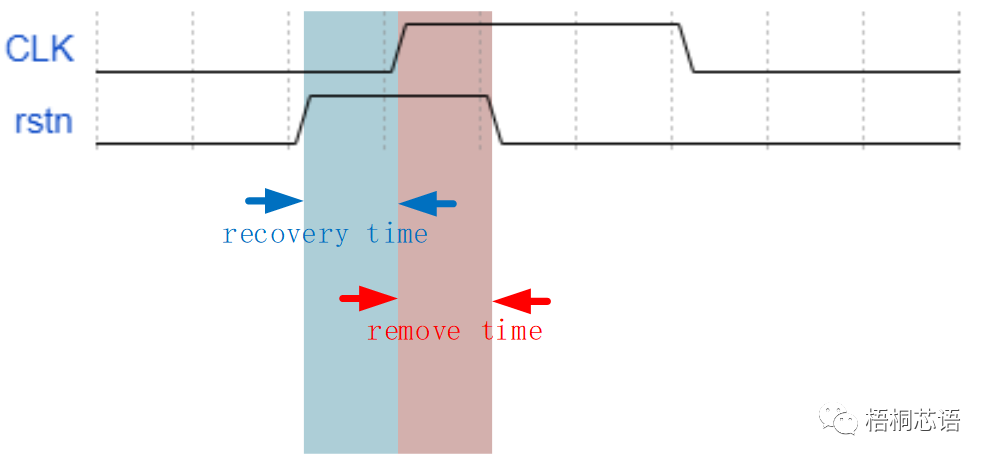

寄存器的recovery和remove時序概念

在建立時間和保持時間概念中,我們可以看到,當時鐘觸發沿到來時,為了保證電路穩定工作,需要在邊沿前后一段時間保持D端數據穩定。

而對于一個帶有異步復位或異步置位的寄存器來說,如果復位信號釋放(從有效變成無效)與時鐘觸發沿同時出現,也會帶來同樣的問題。

當寄存器處于復位狀態,且時鐘處于低電平,則采集部分和輸出部分由于傳輸門U6關閉,處于分割狀態。輸出部分電路,Q端輸出來源于異步復位rstn驅動;而采集部分電路中,D’由于傳輸門U2處于打開狀態,因此由D端輸入,假設D端剛好與Q端數據相反,則在該實例中為高電平。而D’’則來源于異步復位rstn驅動,為高電平。

可以試想,如果異步復位釋放,從有效變換成無效狀態,即示例中從低電平轉換成高電平,那么采集部分電路所有節點,將依靠D端進行翻轉,直到穩定,其中D’’與Q’’因為傳輸門U6關閉,要等待CLK為高的時候才會進行傳輸。之后待CLK從低電平變換成高電平后,U6打開,輸出部分電路再根據D’’進行翻轉,直到Q端輸出高電平,完成復位后,時鐘上升沿觸發工作效果。

但是如果在異步復位rstn釋放的同時,時鐘CLK出現上升沿,則可能出現U2還沒有關閉,但U5已經打開的情況,D’會因為D為高電平以及D’’為高電平發生沖突。如果當U2完全關閉后,D’未完全穩定在某個狀態,則可能導致后面電路失效,Q端在此出現亞穩態的情況。

因此與建立時間與保持時間類似,對于帶有異步復位或異步置位的寄存器來說,異步復位也需要在時鐘上升沿到來之前的一個時間窗穩定下來,稱之為recovery time,而在時鐘上升沿后一段時間內保持住,稱之為remove time。

-

寄存器

+關注

關注

31文章

5355瀏覽量

120547 -

變換器

+關注

關注

17文章

2100瀏覽量

109354 -

VDD

+關注

關注

1文章

312瀏覽量

33268 -

CMOS技術

+關注

關注

0文章

67瀏覽量

10278 -

CLK

+關注

關注

0文章

127瀏覽量

17182

發布評論請先 登錄

相關推薦

寄存器與內存的區別

GPIO寄存器

寄存器的時序要求有哪些?

寄存器的時序要求有哪些?

評論