既然RTL是寄存器傳輸級電路,那么電路設計就一定是以寄存器的特性為基礎進行設計。

一般來說,RTL電路設計我們建議3個主要的原則:

- 時序邏輯與組合邏輯分開

- 數據路徑與控制路徑分開

- 先畫電路,后寫代碼

以上3個原則,我們一個一個來看。

時序邏輯與組合邏輯分開

這里涉及到數字電路基礎知識,不懂的小朋友還是先把數字電路設計原理學一下。我們一般把寄存器(DFF)以及鎖存器(LATCH)看做是時序邏輯,也就是數據輸出與時鐘變化保持有一定的關系。具體的原理,可以參考之前關于寄存器工作原理分析的部分。而組合邏輯,則輸出與時鐘沒有關系,僅僅因為輸入信號的變化,會立即產生變化,如選擇器、與門、或門、非門等。

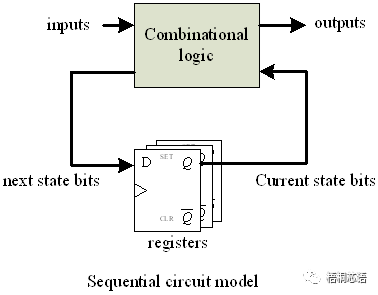

如下圖所示,就是一組完整電路的功能框圖模型:

其工作原理為:

(a) current state bits=↑(next state bits);

(b) next state bits=f1(inputs,current state bits);

(c) outputs=f2(inputs,current state bits);

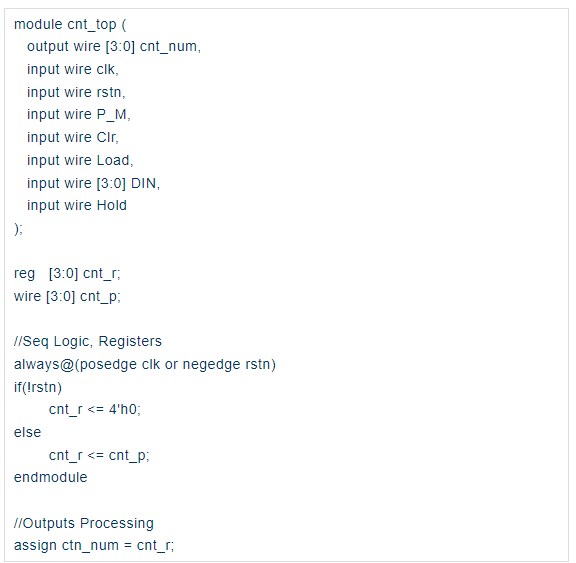

這里面f1和f2就是分別算出next state bits以及outputs的組合電路功能。可以明確的電路,在這里就是時序邏輯電路,或者說是寄存器。所以我們在描述電路的時候,先描述寄存器就好:

接下來我們看,組合邏輯電路怎么設計。

數據路徑與控制路徑分開

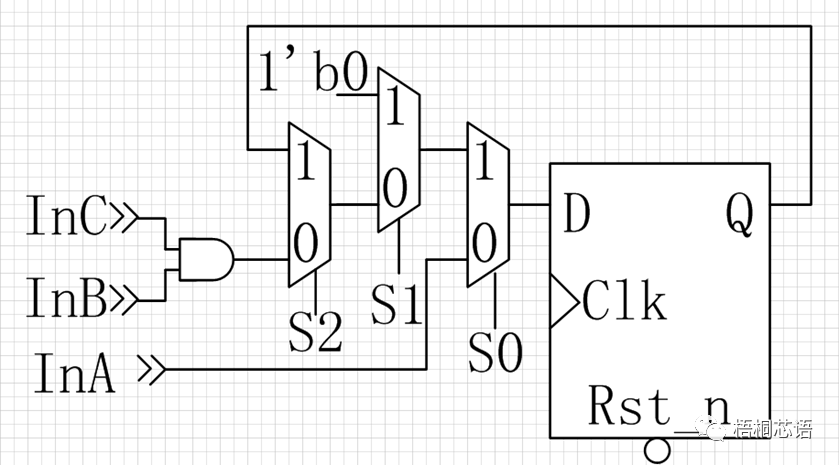

假設我們想描述以下電路:

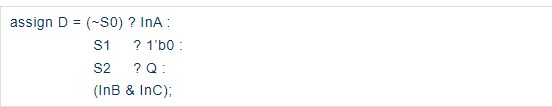

那么時序邏輯的輸入,也就是D端怎么獲得?在正常的思考情況下,我們一般這樣考慮問題,是有邏輯的:

如果滿足XX條件(這里假設S0為0)那么D端來自于InA,否則如果滿足XX條件(這里假設S1為1)則賦值為1'b0,否則如果滿足XX條件(這里假設S2為1)則來源于InC跟InB的與邏輯,否則就保持不變。

這種數據來源的邏輯思考,利用選擇器實現成電路,就是數據路徑的設計思路。而利用VerilogHDL來描述電路,就只需要用assign以及?,:的組合,實現選擇器的功能即可。而Synthesis綜合工具,會根據最終的電路進行優化,實現最優的組合邏輯結構。對設計者來說,首先能做用選擇器來設計數據路徑就可以了。

而S0、S1跟S2是怎么來的?設計S0、S1跟S2就相當于這個電路模型組合邏輯的控制邏輯設計。

當然S0、S1、S2又可以看做一種數據路徑進一步擴展設計,他們可能是組合邏輯直接賦值,也可能是時序邏輯寄存器的輸出。

先畫電路圖,后寫代碼

由于前些年軟件與互聯網產業的蓬勃發展,越來越多的人都把軟件視為生產力第一工具,卻忽略了工程師的主觀能動性。越來越多的年輕人投入到集成電路設計領域往往只是學習了VerilgHDL語言,就開始編寫電路。殊不知這樣的電路,往往會面臨大量不可預知的bug,以及調試人員茫然的眼神。

也許有同學說了,現在有很多代碼風格(coding style),寫電路的時候按照標準的代碼風格寫就好。也許作為一個接近20年電路設計經驗的老工程師來說,心中的電路已經非常清晰,按照coding style編寫的電路還是比較好的,但仍然會因為電路逐步復雜,有些部分無法把握,會遇到疏漏。

在這里我還是呼吁各位同學,先把電路設計功底做好,再考慮如何用描述語言描述出來。至少,這個才叫做電路吧。這樣做的好處主要有以下3點:

邏輯清晰,便于表達及傳遞思路

電路直觀,便于Debug以及修改

信號定義明確,Coding只需照抄

RTL電路設計的方法

其實根據RTL電路設計的原則,我們認為一個已知接口信號以及功能定義的模塊,可以從輸出開始往輸入推著寫。

比如說,我們要設計一個4bit計數器,其功能要求如下:

- 從0到15循環計數

- 加電平輸入信號P_M,P_M為1則往上加,P_M為0則往下減

- 加脈沖輸入信號Clr,Clr脈沖(高有效)來到,則計數器輸出為0

- 加脈沖輸入信號Load,電平輸入信號DIN[3:0],Load脈沖(高有效)來到則計數器輸出加載為DIN[3:0]的值

- 增加一個電平輸入信號Hold,當Hold為高電平時,計數器保持當前值,不做增減。

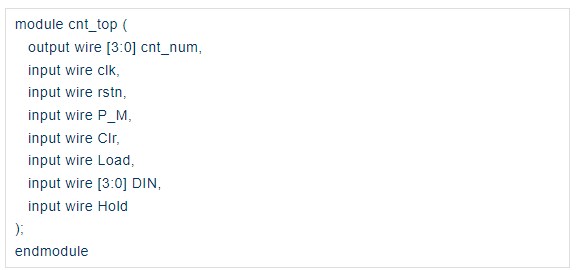

那么首先我們分析這個寄存器的輸入輸出。

輸出就是0~15的數值,需要4bit輸出信號cnt_num,而輸入除了時鐘復位(clk,rstn)外,有P_M,Clr,Load,DIN[3:0]以及Hold。因此我們先把輸入輸出整理出來。

接著我們從輸出設計開始往回(輸入)推導,先定義輸出需要的寄存器來存儲每個周期變化用的計數值,cnt_r,并描述出來:

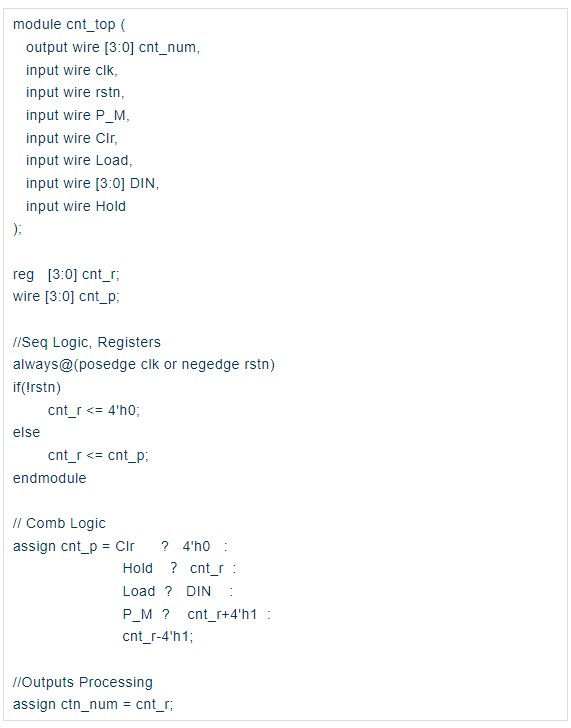

接著,根據功能定義,描述時序邏輯輸入端的數據路徑:

由于所有控制信號來源于輸入,這個電路可以不做控制路徑的設計。但有心的小伙伴應該發現了,如果Hold為高,則想加載DIN是無法實現的。因此這樣設計的電路,其實是存在優先級的。需要與模塊定義的朋友做深入交流,確保實際功能使用時不會出錯。

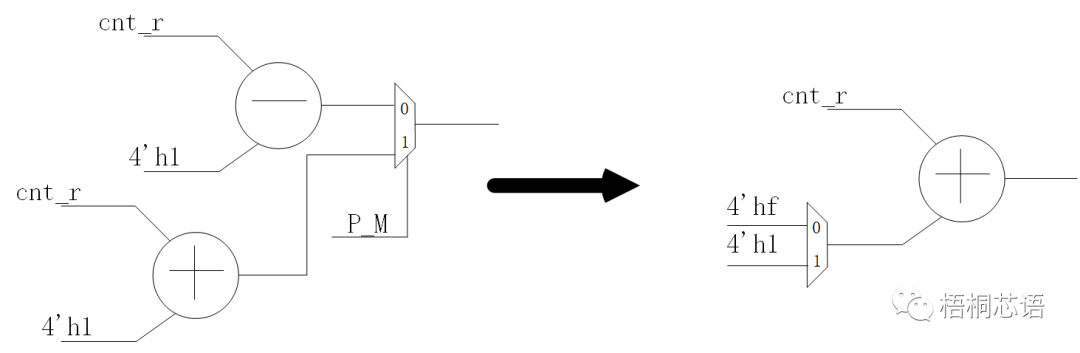

同時,我們看到這個電路里用到了1個加法器和一個減法器,如果想進一步優化電路面積,我們可以考慮加法器的復用:

這樣做電路應該怎么改呢?留給大家去思考了。

復雜電路系統設計方法

現在又要有小伙伴說了,我們的電路很復雜的,如果每個都畫出電路,那什么時候能投片。我的理解是,復雜電路都是簡單電路的衍生,按照功能將系統進行框架劃分,并定義出每個框架之間的接口信號及其時序要求,接著再通過畫電路的方法,設計框架里的電路。有些小的電路實際上是會被復用的。每個公司產品線,大部分時間都會處于一個逐步演進的過程,小電路設計多數是剛開始,后續的工作量會逐步降低。

但如果公司從一開始就不重視畫電路,只是電路描述做實現,也許前幾款產品可以正常跑,過了一段時間,客戶可能突然發現有些地方要優化,有些地方有bug,但之前設計人員可能已經離職。電路描述不好,電路圖也沒有,這個時候負責優化和解bug的小伙伴一定會郁悶的。

-

寄存器

+關注

關注

31文章

5342瀏覽量

120277 -

加法器

+關注

關注

6文章

183瀏覽量

30120 -

鎖存器

+關注

關注

8文章

906瀏覽量

41501 -

RTL

+關注

關注

1文章

385瀏覽量

59768 -

時序邏輯電路

+關注

關注

2文章

94瀏覽量

16540

發布評論請先 登錄

相關推薦

RTL電路的設計原則和方法

RTL電路的設計原則和方法

評論