在一個(gè)復(fù)雜的SoC(System on Chip)系統(tǒng)中,不可能只有一個(gè)時(shí)鐘。我們一般認(rèn)為,一個(gè)時(shí)鐘控制的所有寄存器集合處于該時(shí)鐘的時(shí)鐘域中。兩個(gè)時(shí)鐘域之間是可能有信號(hào)交互的,而且兩個(gè)時(shí)鐘域的時(shí)鐘信號(hào)都可能有源頭、相位以及頻率的區(qū)別,如果不是同源、同相位以及同頻率時(shí)鐘管理的時(shí)鐘域,交互信號(hào)是不能直接被使用的。主要面臨以下幾種情況:

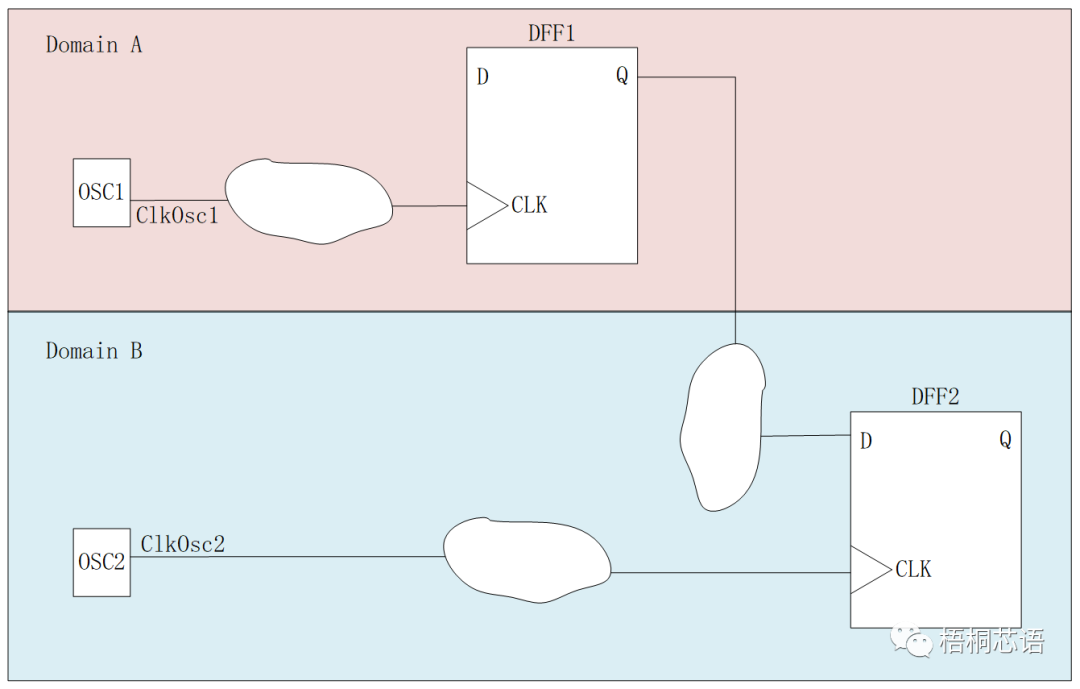

時(shí)鐘的源頭不同

比方說(shuō)時(shí)鐘域A是工作在振蕩器OSC1的輸出時(shí)鐘ClkOsc1下,而時(shí)鐘域B是工作在振蕩器OSC2的輸出時(shí)鐘ClkOsc2下。由于OSC1和OSC2的輸出時(shí)鐘完全不相關(guān),因此無(wú)論是頻率還是相位都不同,這叫做不同源不同頻不同相,如下圖所示,DFF1處于ClkOsc1的時(shí)鐘域A,而DFF2處于ClkOsc2的時(shí)鐘域B,那么DFF2輸入信號(hào)如果有來(lái)自于DFF1的輸出,是不能直接使用的,針對(duì)這種跨時(shí)鐘域的電路設(shè)計(jì)方法,本節(jié)后續(xù)部分會(huì)做詳細(xì)描述。

時(shí)鐘源頭相同

如下圖所示,DFF1、DFF2與DFF3的時(shí)鐘同樣來(lái)源于OSC1的輸出ClkOsc1,但DFF2的時(shí)鐘是ClkOsc1經(jīng)過(guò)某時(shí)序元件(電路)SEQ1(時(shí)序元件可以是寄存器、鎖存器、鎖相環(huán)等)處理后的輸出ClkSEQ1。ClkSEQ1可能是ClkOsc1的分頻、倍頻、門(mén)控時(shí)鐘,在相位和頻率上與ClkOsc1都會(huì)有區(qū)別。

因此,DFF1、DFF3工作在ClkOsc1的時(shí)鐘域A,而DFF2工作在ClkSEQ1的時(shí)鐘域B,至于其間交互數(shù)據(jù),從時(shí)鐘域A去往時(shí)鐘域B的LOG12,以及從時(shí)鐘域B去往時(shí)鐘A的LOG21,需要根據(jù)ClkOsc1和ClkSEQ1之間相位和頻率的關(guān)系進(jìn)行相應(yīng)的設(shè)計(jì)。針對(duì)這種跨時(shí)鐘域的電路設(shè)計(jì)方法,本節(jié)后續(xù)部分會(huì)做詳細(xì)描述。

電平信號(hào)轉(zhuǎn)脈沖信號(hào)處理電路(邊沿檢測(cè)電路)

電平信號(hào)與脈沖信號(hào)之間的轉(zhuǎn)換過(guò)程,是數(shù)字集成電路設(shè)計(jì)中最基本的信號(hào)轉(zhuǎn)換操作。

我們可以將電平信號(hào)看成一種狀態(tài)(status),一種標(biāo)志(flag),表示當(dāng)前電路所處于的一個(gè)穩(wěn)定態(tài)。比如說(shuō)busy信號(hào)為高,表示該電路處于工作狀態(tài)。比如說(shuō)test_mode信號(hào)為高,表示要求當(dāng)前系統(tǒng)工作在測(cè)試模式下。

而脈沖信號(hào)可以看做是一種觸發(fā)要求(trigger),一種狀態(tài)變化的通知(message)。比方說(shuō)要啟動(dòng)電路工作的狀態(tài),給電路一個(gè)脈沖信號(hào)run。比如某個(gè)模塊工作完成了,給個(gè)脈沖信號(hào)finished。

假設(shè)某個(gè)模塊對(duì)外只有一個(gè)busy狀態(tài)標(biāo)志,那么我們?cè)趺粗离娐烽_(kāi)始工作了,還是工作結(jié)束了呢?這就需要將狀態(tài)標(biāo)志busy,分別轉(zhuǎn)換成電路啟動(dòng)信號(hào)work,以及電路工作完成信號(hào)finished,以便告訴系統(tǒng)進(jìn)行下一步的工作。

下圖所示就是產(chǎn)生worked脈沖信號(hào)的電路:

可以看出,busy標(biāo)志為高的時(shí)候,表示電路正在工作,為低的時(shí)候,表示電路沒(méi)有在工作。那么如果busy從低電平轉(zhuǎn)換成高電平,表示電路啟動(dòng)工作了,產(chǎn)生的worked脈沖信號(hào),只有當(dāng)這種變化出現(xiàn)時(shí)才會(huì)為高,否則一直為低。這就將電平信號(hào)變化轉(zhuǎn)換成了脈沖信號(hào)。

Workded表示busy從低到高的一種變化,所以這種電平轉(zhuǎn)脈沖電路我們也可以稱(chēng)之為上升沿采集電路。

以上上升沿采集電路可以用以下Verilog HDL描述:

那么finished信號(hào),表示busy從高變成低的狀態(tài),電路工作結(jié)束,可以采用以下結(jié)構(gòu)實(shí)現(xiàn),當(dāng)然,也被稱(chēng)之為 下降沿采集電路 。

以上下降沿采集電路可以用以下Verilog HDL描述:

可能會(huì)有同學(xué)問(wèn),既然我們會(huì)選取帶異步復(fù)位或異步置位(低電平有效)的上升沿觸發(fā)寄存器,為什么畫(huà)圖的時(shí)候,看起來(lái)只是一個(gè)最簡(jiǎn)單的D觸發(fā)器元件。

這主要是因?yàn)镽TL設(shè)計(jì)時(shí)默認(rèn)采用同步設(shè)計(jì)方法,在同一個(gè)模塊中,所有寄存器都是用同一個(gè)時(shí)鐘源及復(fù)位源輸入,因此畫(huà)圖的時(shí)候做了簡(jiǎn)化處理,時(shí)鐘和復(fù)位在沒(méi)有特殊處理要求時(shí)都不做描述了。

本人所有電路在沒(méi)有特別說(shuō)明的情況下,都會(huì)按照該原則進(jìn)行描述。

脈沖信號(hào)轉(zhuǎn)電平信號(hào)處理電路

既然電平信號(hào)可以轉(zhuǎn)成脈沖信號(hào),表示在某種狀態(tài)變化的時(shí)候要求做一個(gè)動(dòng)作。那么需要因?yàn)槟撤N動(dòng)作的需要,改變一種狀態(tài)。這就是脈沖轉(zhuǎn)電平信號(hào)處理電路。

假設(shè)有兩個(gè)輸入信號(hào),一個(gè)是開(kāi)始信號(hào)start,一個(gè)是停止信號(hào)stop,都是脈沖信號(hào)。其中start脈沖來(lái)了后,要求電路開(kāi)始工作,run狀態(tài)寄存器從低電平變?yōu)楦唠娖健.?dāng)stop脈沖來(lái)了后,要求電路停止工作,run狀態(tài)寄存器從高電平變?yōu)榈碗娖健?/p>

則電路可以按照以下方式設(shè)計(jì),當(dāng)stop為高電平時(shí),把run拉低,當(dāng)start為高電平時(shí),把run置高,否則run保持:

以上脈沖轉(zhuǎn)電平電路可以用以下Verilog HDL描述:

相信還有很多同學(xué)會(huì)有一些不同的電路實(shí)現(xiàn)方式,但在RTL設(shè)計(jì)方法學(xué)中,有一種通用的數(shù)據(jù)路徑設(shè)計(jì)方式,用多路選擇器(Multiplexer),通過(guò)不同的控制信號(hào),選擇寄存器下一個(gè)周期數(shù)據(jù)的來(lái)源,相對(duì)來(lái)說(shuō),會(huì)更切合人類(lèi)思考的方式,同時(shí)對(duì)于硬件描述語(yǔ)言來(lái)說(shuō)也更加友好。

至于最終如何實(shí)現(xiàn)電路,可以交給邏輯綜合工具來(lái)處理。后續(xù)我們會(huì)重點(diǎn)介紹如何利用選擇器進(jìn)行通用電路設(shè)計(jì),這也是RTL設(shè)計(jì)的一種常見(jiàn)方法。

時(shí)鐘域的概念、電平信號(hào)和脈沖信號(hào)轉(zhuǎn)換電路,是作為跨時(shí)鐘信號(hào)采集電路設(shè)計(jì)的基礎(chǔ)。跨時(shí)鐘域的信號(hào)采集,一般分為三種情況,慢時(shí)鐘域到快時(shí)鐘的單位信號(hào)采集、快時(shí)鐘域到慢時(shí)鐘域的單位信號(hào)采集、跨時(shí)鐘域多信號(hào)采集。

***慢時(shí)鐘域到快時(shí)鐘域的單位信號(hào)采集電路

慢時(shí)鐘域到快時(shí)鐘域的單位信號(hào)采集電路,一般用于控制類(lèi)信號(hào)的傳遞。數(shù)據(jù)的源寄存器驅(qū)動(dòng)時(shí)鐘頻率低于驅(qū)動(dòng)采集信號(hào)寄存器的時(shí)鐘頻率。如下圖所示,A時(shí)鐘域寄存器DFFA,其輸出信號(hào)I是由ClkA驅(qū)動(dòng)輸出的,該信號(hào)需要由B時(shí)鐘域的寄存器采集使用,此時(shí)ClkB的頻率大于等于ClkA的頻率,則可以使用以下電路圖來(lái)實(shí)現(xiàn)采集:

如果在B時(shí)鐘域直接使用信號(hào)I,則可能因?yàn)镃lkA與ClkB的相位不同,由于亞穩(wěn)態(tài)原因,造成B時(shí)鐘域信號(hào)混亂,只需要使用去除亞穩(wěn)態(tài)的電路結(jié)構(gòu),確保在B時(shí)鐘域的信號(hào)完整可靠即可。以上電路的工作時(shí)序圖如下所示:

這里面Out1和Out2是電平信號(hào)輸出,通過(guò)去除亞穩(wěn)態(tài)電路處理,確保信號(hào)在ClkB的完整性,就可以在B時(shí)鐘域使用了。而Out3是該信號(hào)上升沿標(biāo)志位,也已經(jīng)在B時(shí)鐘域同步,也可根據(jù)需要選擇使用。

以上信號(hào)處理電路可以用以下Verilog HDL描述(此處不描述DFFA的電路,因?yàn)閬?lái)自于A(yíng)時(shí)鐘域的信號(hào)并不一定就是DFFA的輸出,也可能是DFFA經(jīng)過(guò)組合邏輯的輸出,電路中只是一個(gè)參考):

同樣的電路,用Chisel描述如下:

快時(shí)鐘域到慢時(shí)鐘域的單位信號(hào)采集電路

同樣的,快時(shí)鐘域到慢時(shí)鐘域的單位信號(hào)采集電路,一般也只能用于控制類(lèi)信號(hào)的傳遞。數(shù)據(jù)的源寄存器驅(qū)動(dòng)時(shí)鐘頻率高于驅(qū)動(dòng)采集信號(hào)寄存器的時(shí)鐘頻率,如果僅僅只是考慮去除亞穩(wěn)態(tài)采集,如果跨時(shí)鐘域輸出信號(hào)的有效時(shí)間小于一個(gè)慢時(shí)鐘域的時(shí)鐘周期,就可能根本踩不到。要處理該信號(hào),則同步處理電路相對(duì)較為復(fù)雜,需要有一個(gè)握手的過(guò)程:

如下圖所示,信號(hào)I是由ClkA驅(qū)動(dòng)輸出的,該信號(hào)需要由B時(shí)鐘域的寄存器采集使用,此時(shí)ClkB的頻率大于等于ClkA的頻率,可以采用下圖所示電路做信號(hào)同步采集:

整個(gè)電路的工作時(shí)序如下圖所示:

需要通過(guò)以下幾步,確保信號(hào)的完整傳輸:

A. I通過(guò)脈沖轉(zhuǎn)電平信號(hào)處理電路,轉(zhuǎn)換成電平信號(hào)Ilevel_A,并傳輸出給B時(shí)鐘域使用,這樣做無(wú)論I信號(hào)是脈沖信號(hào)還是電平信號(hào),只要ClrI_A這個(gè)清除信號(hào)沒(méi)有到來(lái),則一直會(huì)處于有效狀態(tài),確保B時(shí)鐘域能夠采集完成。

B. B時(shí)鐘域?qū)時(shí)鐘域傳輸過(guò)來(lái)的電平信號(hào)Ilevel_A做去除亞穩(wěn)態(tài)處理,并采集使用(Out1,Out2,Out3根據(jù)實(shí)際需要使用)。在B時(shí)鐘域采集到有效信號(hào),并使用的同時(shí),通知A時(shí)鐘域清除Ilevel_A。

C. A時(shí)鐘域采集到B時(shí)鐘域清除信號(hào)的需求,做亞穩(wěn)態(tài)處理后,清除Ilevel_A。

D. Ilevel_A被清除后,被B時(shí)鐘域采集,并清除采集到的信號(hào)Out1以及Out2。同時(shí)通知A時(shí)鐘域恢復(fù)ClrI同步電路的狀態(tài)。

E. ClrI同步電路恢復(fù)狀態(tài)。

以上信號(hào)處理電路可以用以下Verilog HDL描述(此處不描述DFFA的電路,因?yàn)閬?lái)自于A(yíng)時(shí)鐘域的信號(hào)并不一定就是DFFA的輸出,也可能是DFFA經(jīng)過(guò)組合邏輯的輸出,電路中只是一個(gè)參考):

同樣的電路,用Chisel描述如下:

跨時(shí)鐘域總線(xiàn)數(shù)據(jù)處理電路

前面介紹了單bit控制數(shù)據(jù)跨時(shí)鐘域處理的電路,這種電路的特點(diǎn)就是確保單根線(xiàn)可以在某個(gè)時(shí)刻穩(wěn)定傳遞到另一個(gè)時(shí)鐘域中,雖然電路圖中都是打兩個(gè)時(shí)鐘周期,但因?yàn)榭赡苡龅絹喎€(wěn)態(tài)傳遞的情況,實(shí)際傳遞的過(guò)程并不是真的2個(gè)時(shí)鐘周期采集到,可能2個(gè),也可能大于或小于2個(gè)。

假設(shè)參考慢時(shí)鐘域到快時(shí)鐘域傳輸采樣電路,只是簡(jiǎn)單去亞穩(wěn)態(tài)的,傳遞多bit數(shù)據(jù),則可能造成采集數(shù)據(jù)在某幾個(gè)時(shí)鐘周期發(fā)生多次跳動(dòng)的情況,并不會(huì)穩(wěn)定傳遞。如下圖所示,數(shù)據(jù)在傳輸過(guò)程中會(huì)因?yàn)閬喎€(wěn)態(tài)傳遞出一個(gè)變化過(guò)程,同時(shí)傳輸?shù)腷it位寬越大,則越不穩(wěn)定(如果采用格雷碼編碼方式傳遞,在某種應(yīng)用場(chǎng)景下,看起來(lái)是可以使用的):

而慢時(shí)鐘采快時(shí)鐘的電路就更不能這樣設(shè)計(jì)了。

這樣看來(lái),握手的過(guò)程仍然是需要的。那么如何握手呢?這個(gè)見(jiàn)仁見(jiàn)智,一般有2種基本的原則,一個(gè)是時(shí)間上的握手,一個(gè)是事件上的握手。

時(shí)間上的握手,相對(duì)比較容易理解,我們知道從A時(shí)鐘域到達(dá)B時(shí)鐘域數(shù)據(jù)傳遞需要一個(gè)時(shí)間,而這個(gè)信號(hào)穩(wěn)定的時(shí)間是可控的,那么只要超過(guò)這個(gè)最大時(shí)間,再行采集就可以了。這種電路常見(jiàn)于采集從模擬異步數(shù)據(jù)處理電路中輸出的數(shù)據(jù),比如說(shuō)下圖所示的嵌入式Flash這種非時(shí)鐘控制類(lèi)元件的輸出。

A時(shí)鐘域產(chǎn)生對(duì)E-Flash輸出控制的使能信號(hào)OE,當(dāng)E-Flash的OE信號(hào)被拉高后,需要一個(gè)時(shí)間,才能從DataOut上穩(wěn)定輸出數(shù)據(jù)。因此,將OE作為驅(qū)動(dòng)信號(hào)實(shí)現(xiàn)一個(gè)B時(shí)鐘計(jì)數(shù)器的使能信號(hào)TimerTrigger,使B時(shí)鐘域的計(jì)數(shù)器開(kāi)始計(jì)數(shù),比如說(shuō)B時(shí)鐘的200個(gè)時(shí)鐘周期,這個(gè)時(shí)間需要大于E-Flash從OE到DataOut的延時(shí)。

計(jì)數(shù)完成前,B時(shí)鐘域的采集電路一直保持,不會(huì)將數(shù)據(jù)送出去使用,確保了電路的穩(wěn)定性,直到計(jì)數(shù)完成,TimerFinished脈沖有效,才將數(shù)據(jù)傳輸出去。同時(shí)TimerFinshed脈沖有效又會(huì)反饋會(huì)A時(shí)鐘域,以便把OE拉低,準(zhǔn)備下一次傳輸。

因?yàn)锳時(shí)鐘域與B時(shí)鐘域不是同一個(gè)時(shí)鐘域(并不絕對(duì),只是舉例),因此OE轉(zhuǎn)換成TimerTrigger的電路以及TimerFinished轉(zhuǎn)換成OE的電路需要做時(shí)鐘域同步處理,只是一個(gè)單bit控制信號(hào)的傳遞,相對(duì)來(lái)說(shuō)就比較好設(shè)計(jì)了。

其實(shí)事件信號(hào)的握手與時(shí)間的握手,從機(jī)制上是一致的,主要是考慮一是什么時(shí)候數(shù)據(jù)被送出來(lái)了,二是數(shù)據(jù)是否已經(jīng)穩(wěn)定,三是數(shù)據(jù)是不是已經(jīng)被采集好,四是數(shù)據(jù)采集完成后需要恢復(fù)初始狀態(tài)準(zhǔn)備下一次數(shù)據(jù)發(fā)送。

第二點(diǎn),數(shù)據(jù)是否已經(jīng)穩(wěn)定,在時(shí)間握手的電路中,就體現(xiàn)在利用計(jì)數(shù)器實(shí)現(xiàn)判斷。因此時(shí)間的握手,其實(shí)也可以看成是一種特殊的事件握手。

如果是判斷數(shù)據(jù)是否穩(wěn)定采集,原理上可以通過(guò)多次比較,比如說(shuō)如果發(fā)生傳輸,且連續(xù)幾次收到的數(shù)據(jù)都是一致的,同時(shí)又與發(fā)送端數(shù)據(jù)一致,則認(rèn)為數(shù)據(jù)穩(wěn)定采集。電路的實(shí)現(xiàn)方式還是比較靈活的,有興趣的小伙伴可以自己動(dòng)手設(shè)計(jì)一下。

因此如果我們把同步電路分成數(shù)據(jù)路徑和控制路徑,那么就不難理解如何進(jìn)行同步了。數(shù)據(jù)不能同步,但控制信號(hào)是可以同步的。就像下面這幅框圖一樣:

異步FIFO

對(duì)于同步電路來(lái)說(shuō),穩(wěn)定的傳輸數(shù)據(jù),一定是最重要的。但分析上面提到的同步電路,小伙伴們應(yīng)該不難發(fā)現(xiàn),如果一次同步工作沒(méi)有完成,第二次同步需求是會(huì)被忽略掉的。那么我們可以采用異步FIFO的電路設(shè)計(jì)方法,來(lái)規(guī)避這個(gè)缺點(diǎn)。

FIFO,即First In First Out的縮寫(xiě),意味著先被寫(xiě)進(jìn)去的,會(huì)先被輸出來(lái),就像是火車(chē)鉆山洞那樣,火車(chē)頭先進(jìn)的山洞,那么也是火車(chē)頭先出的山洞。

異步FIFO的意思就是FIFO輸入和FIFO輸出是不同的兩個(gè)時(shí)鐘域。一個(gè)簡(jiǎn)單的異步FIFO電路結(jié)構(gòu)可以看下面這幅圖:

利用異步FIFO可以讓時(shí)鐘較連續(xù)的從一個(gè)時(shí)鐘域傳輸?shù)搅硪粋€(gè)時(shí)鐘域。

常見(jiàn)的異步FIFO結(jié)構(gòu)一般有2種,一種是如下讀指針和寫(xiě)指針控制同一塊存儲(chǔ)區(qū)域,這種操作,數(shù)據(jù)就像流水一樣,只要寫(xiě)進(jìn)去,就可以讀出來(lái):

另外一種是如下讀指針和寫(xiě)指針控制不同的存儲(chǔ)區(qū)域,寫(xiě)數(shù)據(jù)量較大,且連續(xù)的情況下,可以根據(jù)一次傳輸數(shù)據(jù)總量,先把數(shù)據(jù)存儲(chǔ)在一個(gè)區(qū)域,下次又來(lái)數(shù)據(jù)的時(shí)候,存入另一個(gè)區(qū)域。而讀的區(qū)域與寫(xiě)的區(qū)域直接分開(kāi),完全不受干擾。這種操作,又稱(chēng)為乒乓操作。

而FIFO設(shè)計(jì)中最重要的就是指針的設(shè)計(jì),指針類(lèi)似于一個(gè)計(jì)數(shù)器,隨著寫(xiě)或讀的次數(shù)發(fā)生遞增或遞減,而指針作為存儲(chǔ)塊的地址信號(hào),即可對(duì)存儲(chǔ)塊(一般是RAM或Register File)不同地址進(jìn)行操作了:

一般來(lái)說(shuō)我們建議使用二進(jìn)制計(jì)數(shù)做地址指針,而將其轉(zhuǎn)換成格雷碼用于做空滿(mǎn)控制,這是因?yàn)閿?shù)據(jù)信號(hào)直接傳輸,但控制信號(hào)需要同步,轉(zhuǎn)換成為格雷碼后,可以確保每次指針增減,都只有1bit數(shù)據(jù)在發(fā)生變換且用于同步,不會(huì)在同步過(guò)程中產(chǎn)生毛刺。

網(wǎng)上有不少異步FIFO的開(kāi)源代碼,有興趣的小伙伴可以下載下來(lái)進(jìn)行學(xué)習(xí)和使用。

-

鎖相環(huán)

+關(guān)注

關(guān)注

35文章

584瀏覽量

87747 -

振蕩器

+關(guān)注

關(guān)注

28文章

3832瀏覽量

139054 -

寄存器

+關(guān)注

關(guān)注

31文章

5342瀏覽量

120276 -

信號(hào)處理器

+關(guān)注

關(guān)注

1文章

254瀏覽量

25272 -

SoC系統(tǒng)

+關(guān)注

關(guān)注

0文章

52瀏覽量

10672

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

如何處理好FPGA設(shè)計(jì)中跨時(shí)鐘域問(wèn)題?

探尋FPGA中三種跨時(shí)鐘域處理方法

三種跨時(shí)鐘域處理的方法

三種FPGA界最常用的跨時(shí)鐘域處理法式

如何處理好FPGA設(shè)計(jì)中跨時(shí)鐘域間的數(shù)據(jù)

FPGA跨時(shí)鐘域處理簡(jiǎn)介

看看Stream信號(hào)里是如何做跨時(shí)鐘域握手的

FPGA界最常用也最實(shí)用的3種跨時(shí)鐘域處理的方法

從電路的角度出發(fā),提出了一種新的SOC跨時(shí)鐘域同步電路設(shè)計(jì)的方法

介紹3種方法跨時(shí)鐘域處理方法

如何去實(shí)現(xiàn)一種跨時(shí)鐘域電路的設(shè)計(jì)?

如何去實(shí)現(xiàn)一種跨時(shí)鐘域電路的設(shè)計(jì)?

評(píng)論