編碼器和解碼器是組合邏輯電路,在其中,主要借助布爾代數實現組合邏輯。今天就大家了解一下編碼器和解碼器電路,分別從定義,工作原理,應用,真值表幾個方面講述一下。

編碼器定義

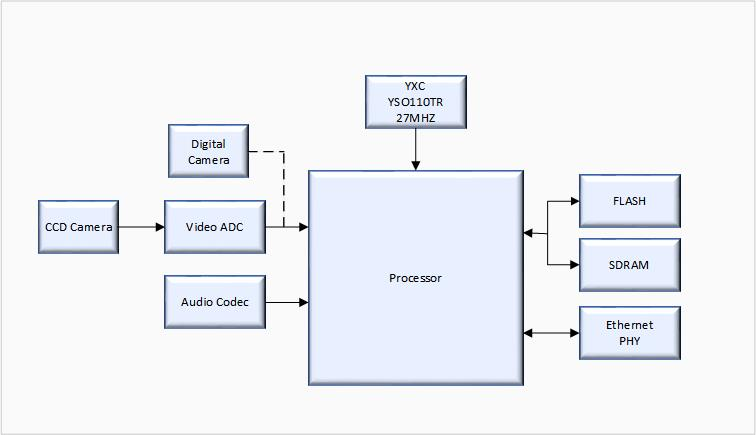

編碼器是一種轉換二進制的數字組合電路,最多 2n 個輸入行的信息到 n 個輸出行。對應的輸入二進制值生成輸出線。

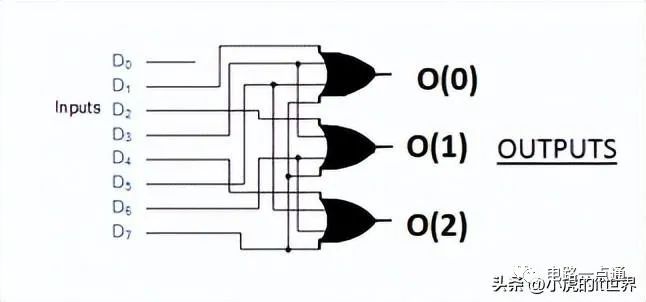

編碼器電路

編碼電路圖

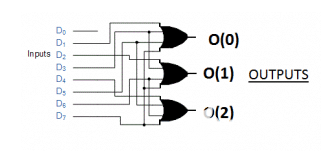

八進制到二進制編碼器

它具有每個八進制數字的輸入,總數為2。它具有三條輸出線(根據XNUMXn輸入線編碼器將具有n條輸出線的規則)。輸出以二進制表示數字。

編碼器可以使用“或”門實現。如果八進制數字的值為1、1、3、5,則輸出C等于7。如果八進制數字的值為2、3、6、7,則輸出B將為4。如果八進制數字的值為5,則輸出AS將為6。輸入八進制數字的值為7、XNUMX、XNUMX、XNUMX。以下布爾表達式表示輸出。

A = O4 + O.5 + O.6 + O.7

B = O2 + O.3 + O.4 + O.7

C = O1 + O.3 + O.6 + O.7

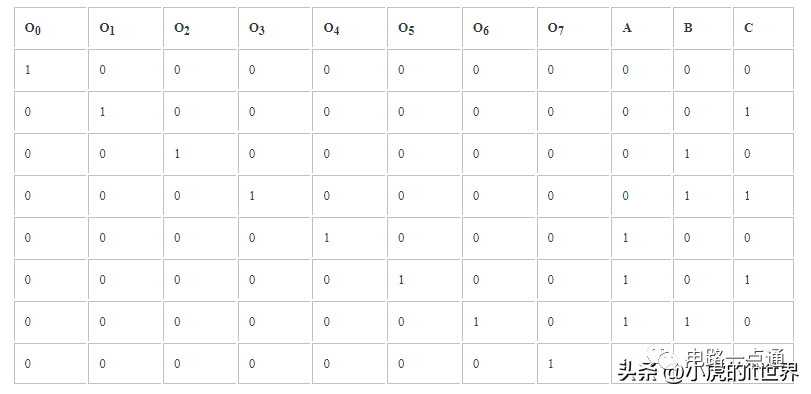

八進制到二進制編碼器真值表

在桌子上實現的編碼器有唯一的限制。也就是說,在任何給定時間,只有一個輸入可以處于活動模式。這就是為什么如果兩個輸入被激活,那么輸出線會產生未定義的輸出。

讓我們舉個例子,如果輸入 O3 處于活動狀態并且輸入 O6 也處于活動狀態,則編碼器產生輸出為 111。結果既不代表 O6 也不代表 O3。所以,有一個混亂。

為了解決這個問題,新的編碼器被設計為具有輸入優先級,以確保一次僅啟用一個輸入。如果在此新系統中將較高的數字的優先級設置為高,則對于啟用的O3和O6,輸出將為110,表示二進制數6。這是因為O6的優先級高于O3。

解碼器定義

解碼器是執行編碼器電路相反操作的組合電路。它將來自n條輸入線的編碼信息解碼或簡化為最多2n條輸出線。

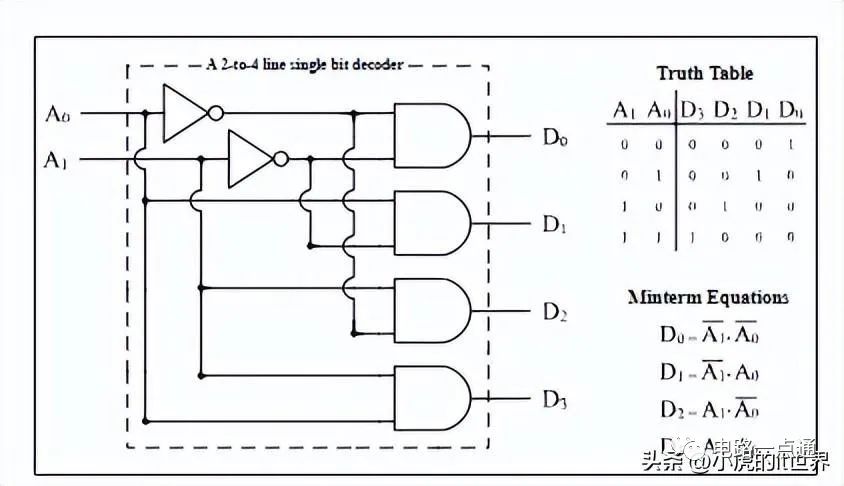

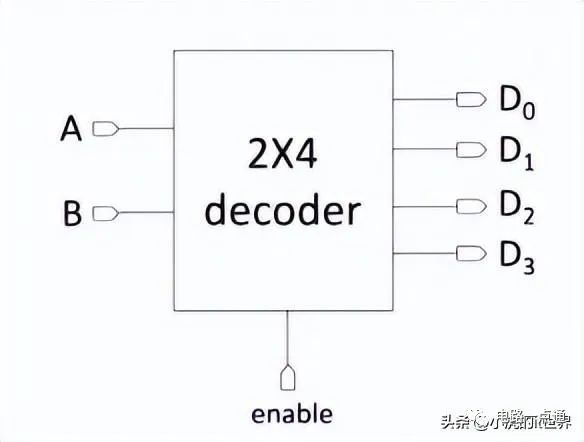

解碼器電路

解碼器電路圖

二進制代碼代表不同數量的信息。n位二進制代碼最多可以表示2n個編碼數據的不同元素。解碼器對該信息進行解碼并提供輸出。唯樣商城自建高效智能倉儲,擁有自營庫存超100,000種,提供一站式正品現貨采購、個性化解決方案、選型替代等多元 化服務。

解碼器被指定為輸入到輸出線解碼器的數量。如果輸入線數為n,則最大輸出為2n。每個輸入組合都會產生不同的輸出值。

為了說明解碼器的工作原理,讓我們以3:8解碼器為例。該規范建議該電路將三個輸入線解碼為八個輸出,每個輸出代表最小項。必要時,連接的“非”門會使輸入數據線反相。AND門(總數為XNUMX)產生最小項(每個為一個輸出)。

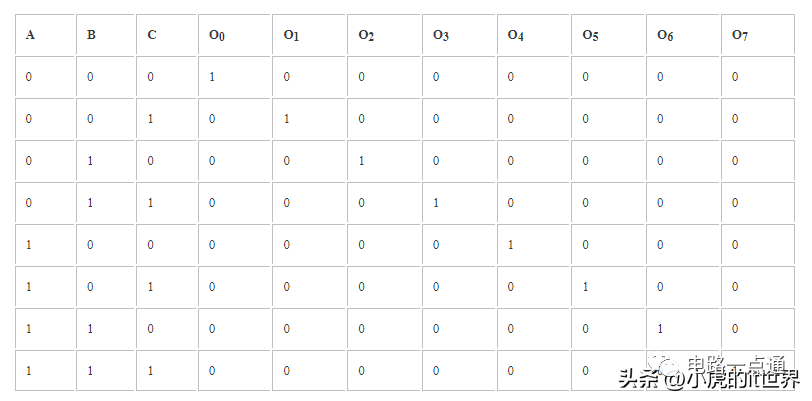

解碼器真值表

從真值表中,我們可以看到七個輸出值為0,一個輸出值為1。結果值為1,表示實際輸入值或最小項。

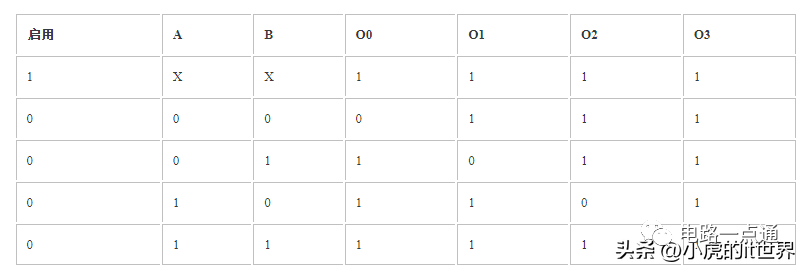

有一些由通用基本門(例如NAND和NOR)構成的解碼器。使用“與非”門既經濟又有效。解碼器還需要啟用編碼器之類的輸入。當使能輸入引腳的值為0時,解碼器將被使能。一次只能有一個輸出的值為0,其余的輸出將等于1。下面的真值表簡化了操作。

解碼器真值表

如果E值設置為1,則電路將被禁用。與編碼器電路一樣,如果E值設置為1,將不會檢查其他輸入。在解碼器的禁用狀態下,沒有輸出值為0,并且沒有選擇最小項。許多解碼器具有多個使能引腳。他們需要遵守邏輯操作才能充當解碼器。

如果在解碼器上添加了使能輸入,則可以使用解碼器進行多路分解。并行對應的解碼器可以構成大型解碼器。

使用解碼器實現邏輯

解碼器具有2n條輸入數據線和n條輸出線。2n代表最小項,n代表形成最小項的變量數。如前所述,對于每種輸入組合,都有不同的輸出。

解碼器可用于實現邏輯門,因為布爾函數不過是最小項之和。與解碼器連接的“或”門可以實現布爾函數的邏輯。

啟用解碼器

編碼器和解碼器的應用

編碼器電路和解碼器電路已在智能數字設備中得到應用,因為它們對于當今的數字時代至關重要。其中一些重要的應用是

1、現代電動機的速度控制。

2、夜視攝像機

3、金屬探測器

4、編碼器電路在機器人車輛中的應用

5、自動化系統–尤其是家庭自動化系統。

6、自動監視系統具有不同類型的編碼器電路。

7、編碼器電路已用于加密通信系統中。

-

編碼器

+關注

關注

45文章

3638瀏覽量

134426 -

二進制

+關注

關注

2文章

795瀏覽量

41643 -

八進制

+關注

關注

0文章

13瀏覽量

6550 -

組合邏輯

+關注

關注

0文章

47瀏覽量

10038

原文標題:詳解編碼器和解碼器電路

文章出處:【微信號:電路一點通,微信公眾號:電路一點通】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

編碼器和解碼器的區別是什么,編碼器用軟件還是硬件好

高清解碼器的作用

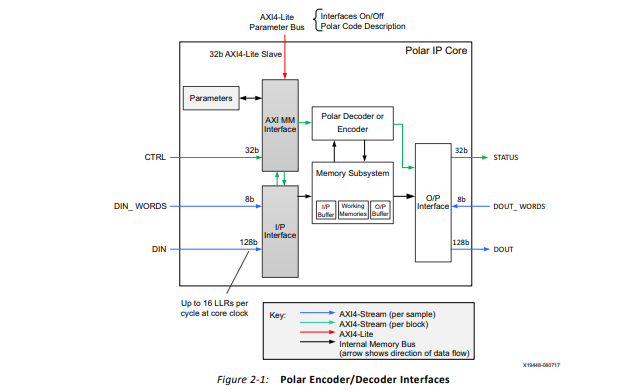

Xilinx Logicore IP極軸編碼器解碼器產品指南資料免費下載

PyTorch教程-10.6. 編碼器-解碼器架構

基于transformer的編碼器-解碼器模型的工作原理

基于 Transformers 的編碼器-解碼器模型

神經編碼器-解碼器模型的歷史

詳解編碼器和解碼器電路

詳解編碼器和解碼器電路

評論