大俠好,歡迎來到FPGA技術江湖。本次帶來FPGA系統性學習系列,今天開始正式更新,之前更新過類似的郝旭帥FPGA零基礎學習系列,由于時間久遠,之前的系列所用開發操作軟件、硬件設備及所涉及知識維度都有待更新及完善。

本系列將帶來FPGA的系統性學習,從最基本的數字電路基礎開始,最詳細操作步驟,最直白的言語描述,手把手的“傻瓜式”講解,讓電子、信息、通信類專業學生、初入職場小白及打算進階提升的職業開發者都可以有系統性學習的機會。

系統性的掌握技術開發以及相關要求,對個人就業以及職業發展都有著潛在的幫助,希望對大家有所幫助。后續會陸續更新 Xilinx 的 Vivado、ISE 及相關操作軟件的開發的相關內容,學習FPGA設計方法及設計思想的同時,實操結合各類操作軟件,會讓你在技術學習道路上無比的順暢,告別技術學習小BUG卡破腦殼,告別目前忽悠性的培訓誘導,真正的去學習去實戰應用,這種快樂試試你就會懂的。話不多說,上貨。

Intel FPGA開發流程

作者:郝旭帥校對:陸輝

本篇目錄

1. 設計前準備

2. 建立工程

3. 輸入設計

4. 綜合和分析

5. RTL仿真

6. 鎖定管腳

7. 布局布線

8. 時序仿真

9. 生成配置文件并下載

正文

本篇將設計一個簡單的二輸入與門,來講解整個設計流程。至于設計語言就不在單獨列出一個章節去做特殊說明,語法、操作、實驗將同時講解,這樣更具有帶入性,便于讀者閱讀和學習。

1 設計前準備

在設計之前我們需要在兩個方面進行準備:硬件方面和軟件方面。

硬件方面

開發FPGA設計,最終的產品是要落在使用FPGA芯片完成某種功能。所以我們首先需要一個帶有Intel FPGA芯片的開發板。

本文中設計將采用CYCLONE系列FPGA進行講解,如果讀者有其他系列(必須是Intel FPGA,否則無法在Quartus上開發),也可以進行學習,不同系列的開發流程基本相同。

軟件方面

我們需要綜合工具-quartus 軟件和仿真工具-modelsim軟件。正確安裝這兩個軟件是開發Intel FPGA的必要條件。

圖1 :Quartus 軟件圖標

按照《quaruts prime 18.0標準版安裝與破解-郝旭帥團隊V1》的方式安裝,Modelsim軟件的圖標將不會出現在桌面上。并不是沒有安裝上,而是此時Quartus軟件認為Modelsim軟件只是它的一個小程序包而已,所以就沒有體現單獨的軟件圖標。

當準備好軟件后,筆者向大家推薦一個工程管理的方式,也是本文中做工程管理的方式,這樣會比較清楚。

做設計的話,會編寫很多設計文件、仿真文件以及綜合器會給我輸出很多的過程文件等等,那么這些文件最好都能有自己的一個“歸宿”,不要亂放。

路徑和命名中不允許出現非法字符(合法字符包括:數字、字母、下劃線。特別說明:空格是非法的),筆者建議以字母開頭。

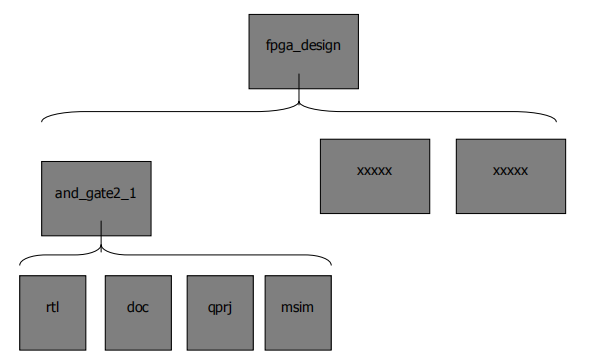

我們是做FPGA開發設計的,首先我們將建立一個文件夾,專門用來放FPGA開發設計。例如:E:/fpga_design。

在后續的開發設計中,我們會做各種各樣的設計。每個設計都有自己的名字,在上述文件內,用實驗的名字命名一個文件夾。名字的話一定要帶有某種含義,不建議隨便給個字母序列當做名字。例如:第一個要做的二輸入與門的設計,命名為and_gate2_1。

在建立完某項設計的文件后,依次在其里面新建四個文件夾,分別為:rtl、qprj、msim、doc。

圖 2 :工程管理文件脈絡示意圖

rtl文件夾用于存放設計的源文件。

doc文件夾用于存放設計的一些文檔性的資料。

qprj文件夾用于存放quaruts 工程以及quartus生成的一些過程性文件。

msim文件夾用于存放仿真文件。

在 FPGA 設計時,主要是這四個文件的使用。某些時候我們也會新加一些文件,例如:FPGA板卡需要我們設計自己時,就會多一個文件夾PCB,用于存放PCB相關的工程或者源文件等。

2 建立工程

做好設計前準備后,就可以開始建立quartus 工程了。

在做設計時,都是以工程為主體的設計。在沒有工程的情況下,利用quartus軟件打開設計源文件等,也是不支持編譯和綜合的。

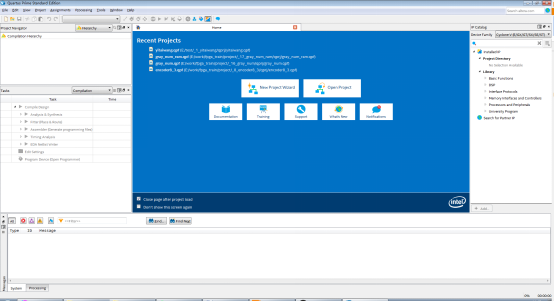

雙擊quartus 軟件的圖標(圖4-1),打開quartus軟件。在有的電腦上,軟件啟動的速度不是很快(在確保自己已經雙擊打開的前提下,可以等待1分鐘),不要多次去雙擊圖標,容易造成PC卡死或者啟動了很多個quartus軟件。

圖3 :quartus 18.0界面

筆者這里不對每個界面進行單獨介紹,后續用到那個功能或者界面時,會單獨介紹說明。

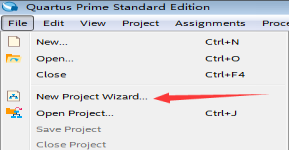

點擊左上角File,選擇New Project Wizard…。

圖4 :打開新工程創建向導

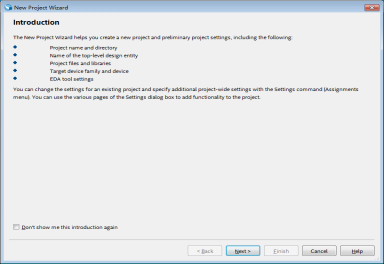

打開新工程向導,首先出現一個工程向導介紹說明。

圖5 :工程向導的介紹界面

在工程向導中,我們會指定工程名稱和位置,頂層實體的名稱,工程文件和庫文件,目標器件,EDA工具。

在復雜設計時,會將電路分成各個小模塊去做設計,最終還需要一個大模塊將這些小模塊包括進來,對外呈現都是大模塊的接口。此時,這個大模塊就是頂層實體(TOP level entity)。如果設計中只有一個模塊,那么這個模塊就是頂層實體。

點擊Next。

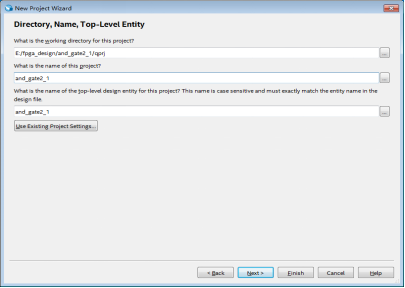

圖6 :指定工程位置、工程名稱和頂層實體的界面

將工程的位置指定到之前我們準備好的文件夾(qprj)中。點擊編輯框后面的三個小點,進行文件搜索指定。

工程的名稱就是采用之前我們做的設計文件夾的名字,這個名字可以是任意的,筆者建議和文件夾保持一致,因為當初建立文件夾時,就是選擇用工程的名字。直接輸入工程名稱and_gate2_1即可。

頂層實體的名字會自動出現,與工程的名字保持一致。我們也可以重新指定一個新名字,筆者建議與工程名字保持一致。

點擊Next。

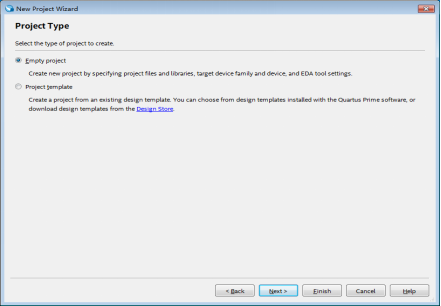

圖7 :選擇建立的工程的類型

選擇空白工程(默認空白工程),點擊Next。

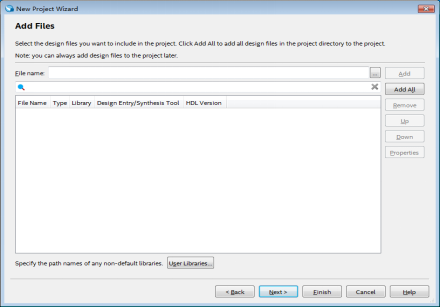

圖8 :添加文件

建立工程時,我們可以直接向工程中添加已有的文件。一般我們選擇什么都不添加,后續設計中,如果有提前做好的文件,也是選擇什么都不添加。建立完工程后,依然可以向工程添加文件。

點擊Next。

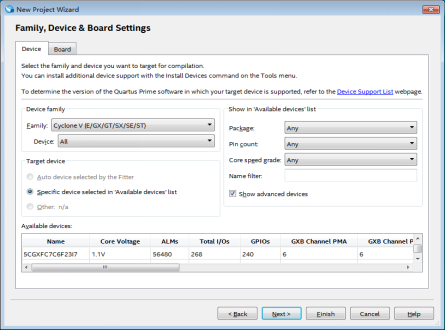

圖9 :選擇目標器件

FPGA設計最終是要落實到芯片內部,在這里要選擇對應的芯片(自己手里開發板的FPGA芯片)。芯片的型號在FPAG的芯片上有描述,如果芯片上看不清楚,或者芯片在被其他東西擋住,可以查看開發板的資料,一般都有介紹。筆者手中開發板的FPGA的型號為EP4CE10F17C8N。后續所有的選擇將按照筆者手中的型號進行設計和選擇,讀者不相同的,請自行改動。如果暫時還沒有開發板的讀者,可以跟著筆者選擇繼續下面的步驟(沒有開發板的話,后面有一些步驟是做不了的)。

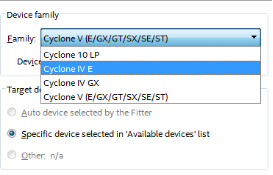

選擇時,首先選擇對應的系列。

圖10 :選擇芯片所對應的系列

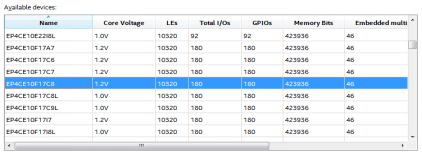

選擇對應的系列后,可以看到下面的器件列表(此列表的窗口是可以拉大的,可以直接擴大整個界面)中,就出現很多的器件。呈現的器件都是按照一定的規律進行排列的,可以很快的找到自己的芯片,然后單擊選擇芯片(先不考慮為什么沒有EP4CE10F17C8N,而選擇EP4CE10F17C8)。

圖11 :器件列表

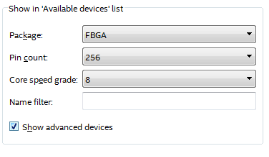

如果每次新建工程都是這樣去尋找芯片的話,是有一定的累人。好在這個軟件給我們提供了篩選面板,我們可以把篩選條件輸入進去。

圖12 :器件篩選

設置好篩選條件后,器件列表中就只有四個器件了,很容易就可以找到我們這款芯片。

篩選條件中有封裝類型、管腳數目和速度等級。那么我們怎么知道自己手中的芯片的這些信息呢?

答案都隱藏在芯片的名字中。筆者手中的是CYCLONE IV系列的片子,下面就介紹一下這個系列的命名方式。

圖13 :CYCLONE IV E系列命名規則

如果是其他系列,請自行參考所對應的芯片手冊。

通過觀察圖4-13,EP4CE10F17C8N中末位N,只是表示無鉛封裝,和具體內部機構沒有任何關系。故而選擇不帶N的,也是可以的。

注意無論是哪種方法,最后找到自己想要的芯片后,一定要點擊它,選中它。

點擊Next。

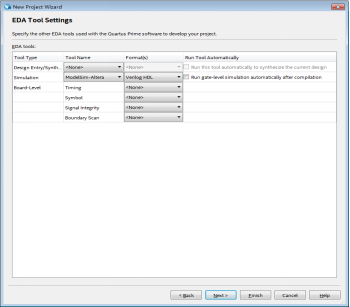

圖14 :選擇EDA工具

Quartus軟件是一個綜合工具,他可以關聯一些其他的工具協助設計FPGA。在這里我們在simulation一欄,工具選擇modelsim-altera,格式選擇verilog HDL。其他保持默認。

點擊Next。

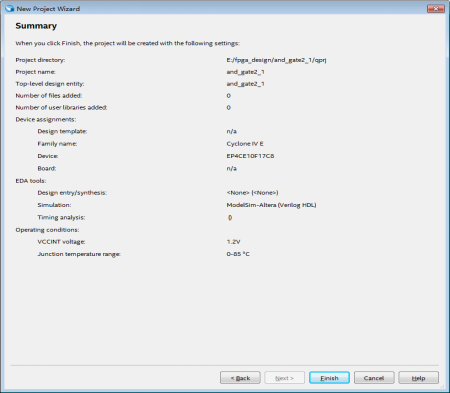

圖15 :工程向導配置總結

這個總結顯示出在新工程向導中,我們所做的所有的設置。大家可以檢查一下,如果發現那一項和自己的要求不一致,就需要點擊back,修改后,在回到此步驟。

點擊Finsh,完成工程創建。

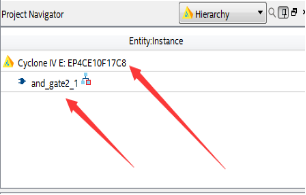

圖16 :工程建立完成后,工程向導界面

工程建立完成后,工程向導界面顯示出選擇的器件和指定的頂層實體。

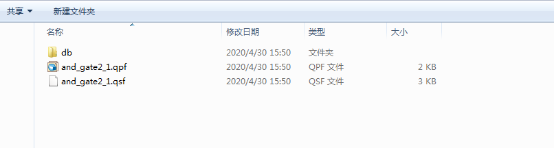

打開qprj文件夾。

圖17 :建立完工程后的qprj文件夾

db文件夾為基礎數據文件夾。

.qpf為quartus project file,quartus 工程文件。如果此時將quatus關閉了,雙擊此文件就可以打開工程。

.qsf為quartus settings file,quartus 設置文件。在quaruts里面做的大部分操作都會記錄到此文件中。

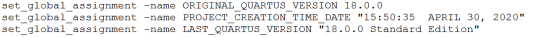

Quarus 的版本很多,如果用一個版本建立的工程,用另外一個版本打開可能會出一些bug,所以建議采用使用已建好工程的版本打開。可以使用記事本的方式打開.qsf。

圖18 :qsf文件的一部分

通過查看.qsf文件,可以了解到工程的最初用什么版本建立,最后用什么版本打開(打開時,建議采用最后的版本打開)。

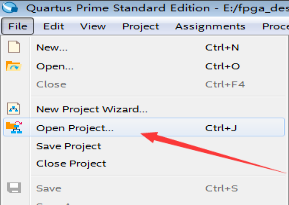

打開工程的方式,不建議采用雙擊.qpf文件。有時間一個PC上面,會有多個quaruts軟件的情況,如果直接雙擊,就會采用某一個版本打開,這不一定是我們想要的。

建議打開工程的方式,首先查看應該選擇的版本,啟動對應的版本quartus軟件,點擊File,選擇Open project(不要點擊Open),找到工程,啟動。

圖19 :打開工程的途徑

3 輸入設計

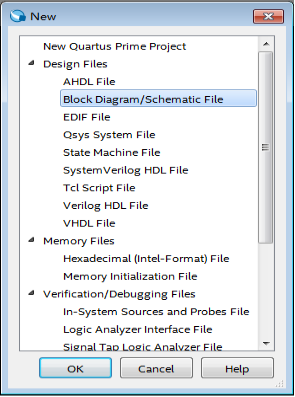

當建立完工程后,就可以輸入設計。輸入設計的方法有三種:原理圖輸入、HDL代碼輸入、原理圖和HDL代碼混入輸入。

原理圖輸入

原理圖輸入就是以現有模塊級聯的方式實現功能。

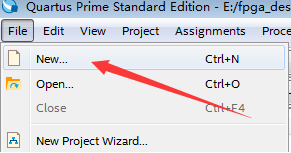

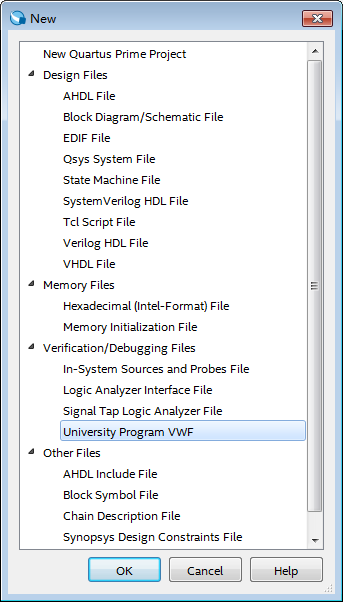

點擊File,選擇New。

圖20 :新建模塊

選擇design file中的Block Diagram/Schematic File。點擊ok。

圖21 :新建文件列表

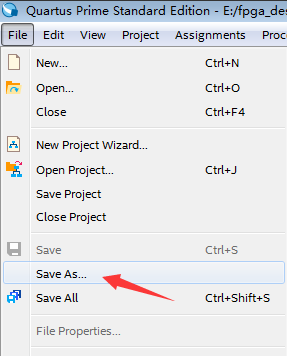

對于新建的bdf文件立刻進行另存為。

圖22 :另存為

另存為到qprj文件夾。Bdf文件是只有quartus軟件才能認可,不具有移植性,把它放到工程文件夾中。

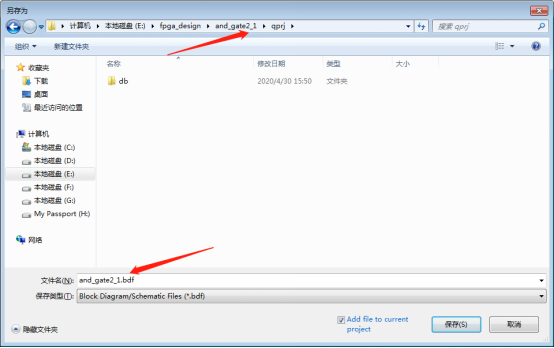

圖23 :保存路徑和名稱

點擊保存。特別注意保存路徑和保存名稱。不要盲目直接點擊保存,一定要再三確認。

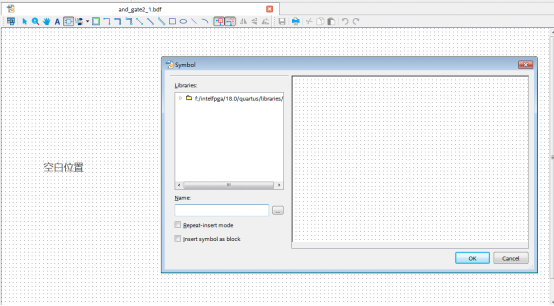

在BDF文件的空白位置,雙擊,打開添加原件的窗口。

圖24 :打開添加原件的窗口

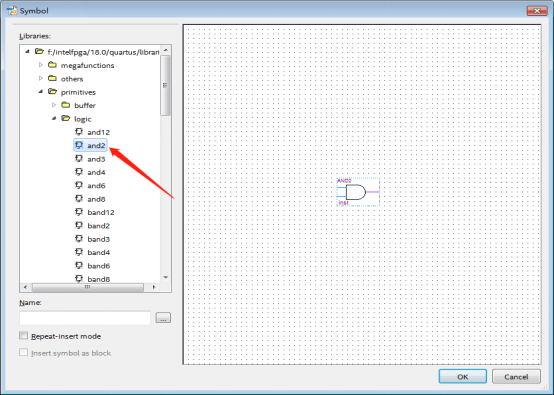

在libraries中,選擇and2,點擊ok。

圖25 :添加二輸入與門

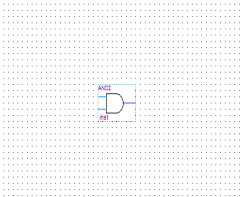

鼠標會拖動一個二輸入與門的符號,此時點擊鼠標左鍵,一個二輸入的與門就放置在文件中了。

圖26 :放置的二輸入與門

當添加完二輸入與門后,也就意味著芯片內部的設計完成。現在需要將內部設計與外部相連接。芯片與外界相連接靠的是IO。

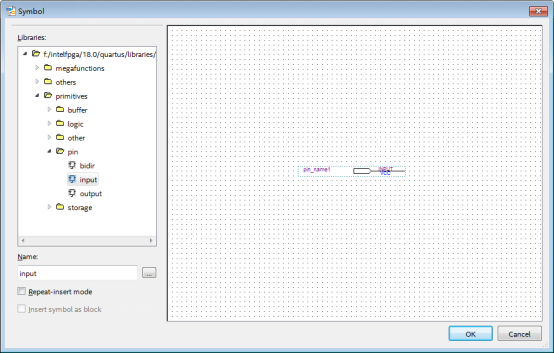

雙擊空白處,選擇input(輸入),點擊ok。添加輸入IO。

圖27 :添加input管腳

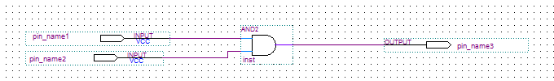

二輸入與門,要有兩個輸入。同樣的方法,再次添加一個。同時也要有一個輸出,選擇output(輸出)(在input下面),添加一個輸出。

圖28 :添加兩個輸入和一個輸出

將管腳和二輸入與門進行相連接。

把鼠標移至需要連接線的地方時,鼠標會自動變為十字狀(不是十字狀箭頭),并且右下帶有一個“7”形的導管。然后按住鼠標左鍵進行導線的引出。當連接到另外一個接口時,

就會出現一個小方框,證明已經連接上,此時釋放鼠標左鍵即可。

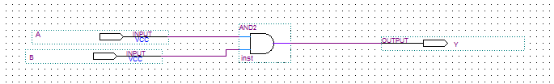

圖29 :連接完成圖樣

此時默認兩個輸入的管腳的名字為pin_name1和pin_name2。在設計時,二輸入與門我們將其輸入命名為一個為A,一個為B,輸出為Y。

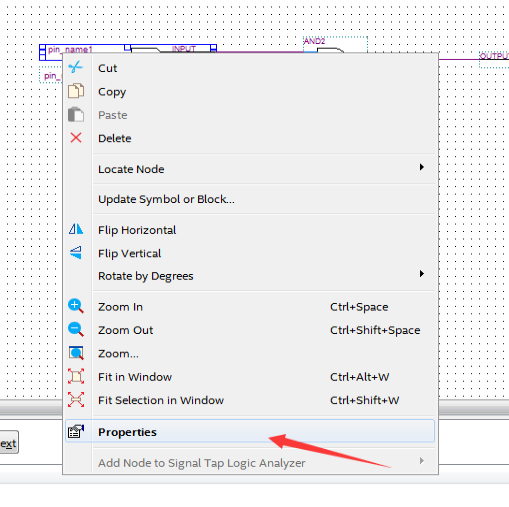

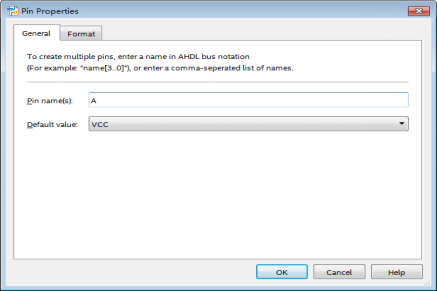

右擊pin_name1,選擇properties。

圖30 :選擇屬性

將pin name改為A。點擊ok。

圖31 :修改管腳名稱

將其他兩個管腳也做對應修改。

圖32 :修改完管腳名稱的圖樣

此時點擊保存(ctrl + s),使用原理圖的輸入方式就完成了。

HDL代碼輸入

用計算機語言設計一個數字電路系統,其實質就是用一種語言描述一個硬件模型,因此這樣的語言又稱為硬件描述語言(Hardware Description Language),或使用縮寫HDL。雖然現在HDL已經有多種語言版本,而且還在發展中。但是在本書討論的HDL僅包括現在最常使用的Verilog HDL和VHDL兩種語言系統。

目前在國內做FPGA設計的公司中,使用Verilog HDL占據大多數,故而本書以Verilog HDL為主,在后續的章節中,專門設置一章來講解VHDL。

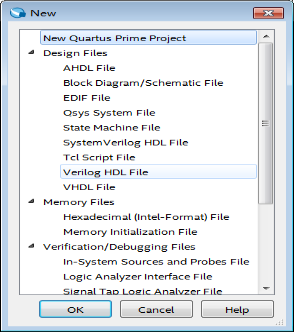

選擇File,New,選擇design file中的verilog HDL file。點擊ok。

圖33 :新建verilog HDL file

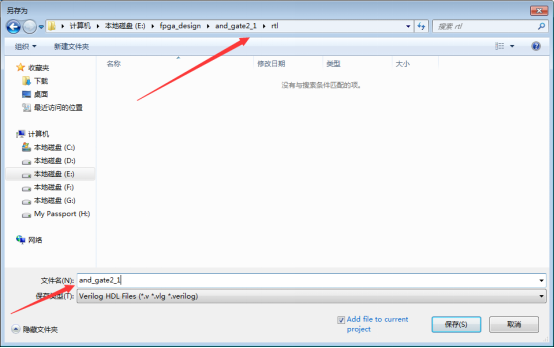

新建完成后,立刻另存為,保存到rtl中。hdl文件的移植性比較高,無論在哪個平臺都是通用的。

圖34 :保存verilog HDL文件

保存時,注意名字和保存路徑。Verilog文件的后綴為.v。

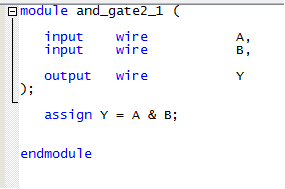

建立完,verilog HDL文件后,就需要輸入二輸入與門所對應的verilog代碼了。

Verilog 語法和C很相似,學習起來比較容易。下面我們按照做電路的方式講解verilog語言。

做電路的話,首先需要拿出一塊打的面包板,剪出合適大小的一塊。相當于圈了一個地方,做設計只能在這塊區域內。

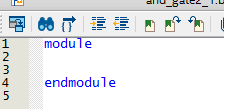

對于verilog語言來說,需要用module和endmodule圈出一個區域,設計代碼只能在這塊區域中。Verilog語言區分大小寫,我們一律采用小寫。module和endmodule是verilog的關鍵字,在綜合器中會變藍。如果endmodule沒有變藍,請多打一個回車或者空格。

圖35 :verilog第一步

當剪出合適大小的面包板后,需要其上面寫一個名字。后面應用也好,說起來也好,好歹有個名字。

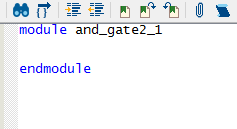

在verilog中,也需要有一個module name。

在verilog中命名的話,需要遵從一定的規則。由字母、數字、下劃線構成;建議字母開頭;不能夠與verilog的關鍵字相同;命名是要有一定的意義。

對于module name來說,一般還有一個要求,與文件名稱保持一致。那么此時我們要做二輸入與門,文件名稱是and_gate2_1。要求module name也寫成and_gate2_1。

圖36 :verilog第二步

當對面包板命名后,需要給它添加輸入和輸出的端口(合理的布局接口)。

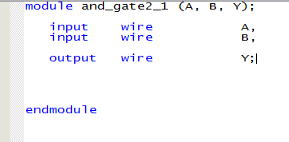

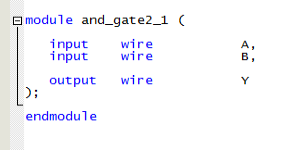

二輸入與門有兩個輸入,一個為A,另外一個為B;一個輸出為Y。在verilog中,布置接口的方式有兩種。

圖37 :布置接口的第一種方式

圖38 :布置接口的第二種方式

在verilog中,module name(and_gate2_1)之后的那個括號中的內容成為端口列表。

Verilog布置接口的第一種方式為1995標準,第二種方式為2003標準。目前大多數平臺都可以支持這兩種方式。筆者建議用2003標準。

端口列表中,描述端口時,用逗號隔開,最后一個端口后面不加逗號。在端口列表的括號后面有一個分號。

對于描述端口來說,有最基本的四項:方向、類型、位寬、名稱。

input表示輸入,output表示輸出,inout表示輸入輸出。

類型中比較常用的有兩種:一種是wire,另外一種reg。wire類型時,wire可以省略不寫。另外input必須是wire類型。筆者建議wire不省略,都寫上。

在做電路時,位寬表示有幾根線。有時候為了方便,會將同一種類的線進行同時命名,此時就需要用到位寬。例如:5位的地址線。可以單獨命名5次,但是比較麻煩。位寬用中括號括起來,例:[3:0],[3:1],[2:5]。如果位寬為1的話,省略不寫。筆者建議位寬的右側為0,左側為位寬減一。

名稱就是為這個輸入命名了一個名字。命名時要遵從verilog命名規則。

在做完端口后,需要在面包板上做出符合功能的設計,然后用連接線將設計和輸入輸出管腳相連接。

二輸入與門的設計是需要在中間放一個組合邏輯電路二輸入與門。

Verilog中,描述組合邏輯的第一種方式是利用assign語句進行描述。

圖39 :assign語句描述二輸入與門

assign語句要求被賦值變量(Y)為wire類型,中間采用阻塞賦值(=)的方式,最后面是賦值表達式,在verilog中,算術與用&來表示(后續介紹算術運算和邏輯運算的區別)。

至此,二輸入與門的HDL輸入就完成了。

原理圖和HDL代碼混入輸入

在復雜設計時,我們可以用HDL代碼生成底層模塊,用原理圖的方式,將底層模塊進行連接。此方式在后續的章節中介紹。

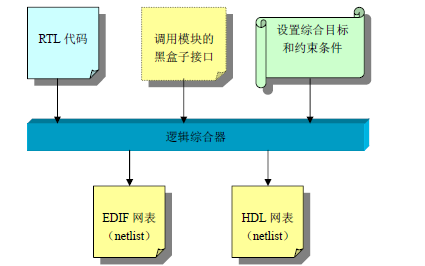

4 綜合和分析

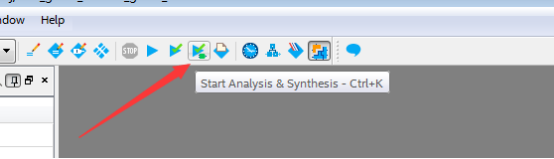

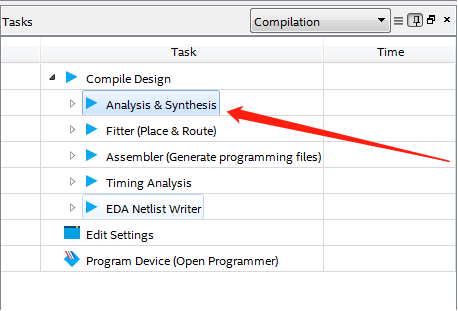

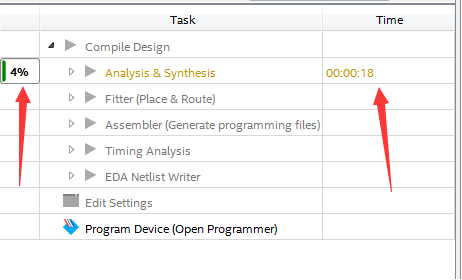

當設計輸入完成后,需要對設計進行綜合分析,同時也檢查一下其中是否存在錯誤。可以單擊綜合分析按鈕,可以雙擊綜合分析選項,也可以利用快捷鍵(Ctrl + K)。

圖40 :綜合分析按鈕

圖41 :綜合分析選項

進行綜合分析時,有時會提出一個提示:

圖42 :某文件被改變,是否要保存

出現上述提示,就證明我們在設計時,修改了某些文件后,沒有點擊保存。此時點擊Yes即可。但是這是一個非常不好的習慣,建議大家修改完任何設計都要及時保存。

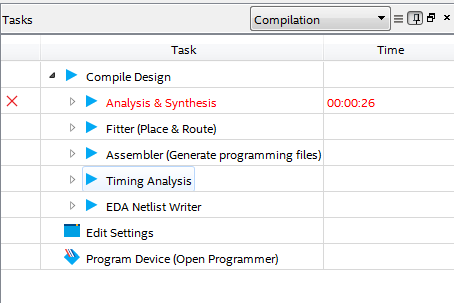

圖43 :Task的綜合分析前面的進度條和后面的已用時間

經過一段時間后,會出現錯誤。

圖44 :出現錯誤

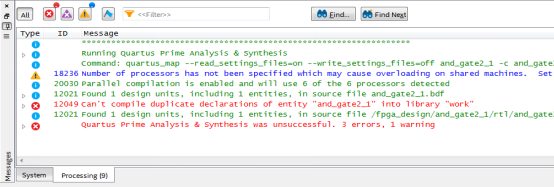

出現錯誤后,可以觀察quartus 的下部massage窗口。

圖45 :massages窗口報錯信息

報錯信息為:錯誤(12049):無法將實體“and_gate2_1”的重復聲明編譯到庫“work”中。報錯的原因是我們在本工程中聲明了多個and_gate2_1,在電路中是不允許出現多個電路模塊是同樣的名字。

在設計時,為了演示原理圖輸入和HDL代碼輸入,工程中存在原理圖輸入的and_gate2_1和HDL代碼輸入的and_gate2_1。

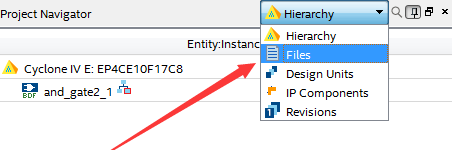

在工程向導界面,選擇Hierarchy,選擇Files。Hierarchy為結構,顯示工程的電路模塊的結構;Files為文件,顯示工程中存放的所有文件。可以利用此方式查看,工程中是否存在多個and_gate2_1。

圖46 :選擇Files界面

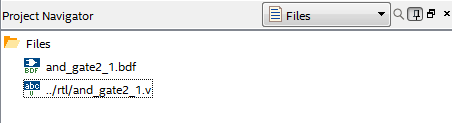

在Files界面中,可以發現工程中確實存在兩個and_gate2_1。

圖47 :Files界面

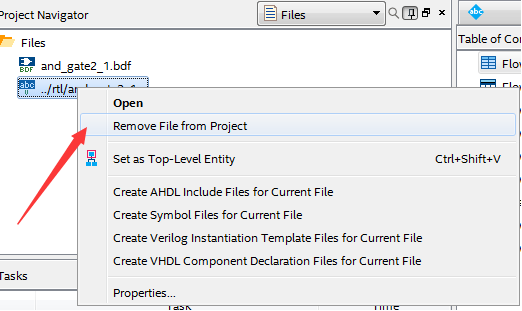

此時右鍵選擇第and_gate2_1.v,選擇Remove file from project。

圖48 :選擇移除

隨后在確定界面點擊Yes。

圖49 :確認移除

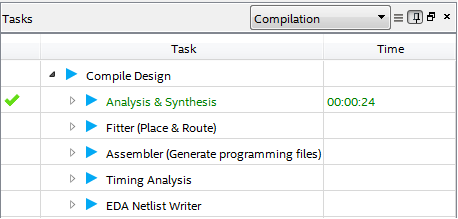

將其移除工程后,就會只剩下一個原理圖輸入的and_gate2_1。然后進行綜合分析,等待結果完成。

圖50 :綜合分析成功

如果中間有錯誤的話,請參考輸入設計中的原理圖輸入,查看自己的步驟是否正確。

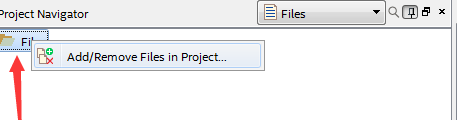

再一次選擇到Files界面,將and_gate2_1.bdf移除。將HDL代碼輸入的and_gate2_1.v

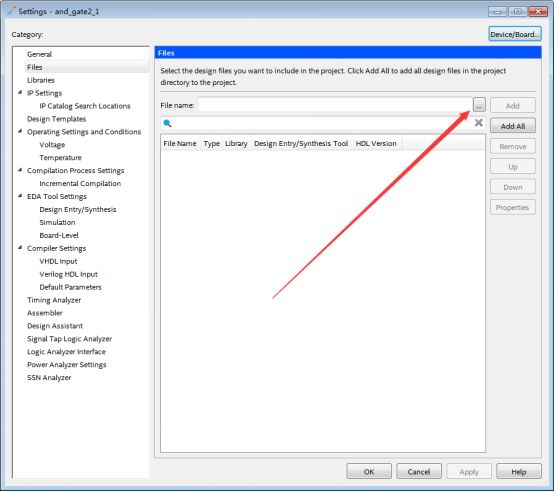

重新添加回來。在Files上右鍵,選擇Add/Remove Files in project(添加或移除文件)。

圖51 :從工程中添加或移除文件

選擇編輯框后面三個點。

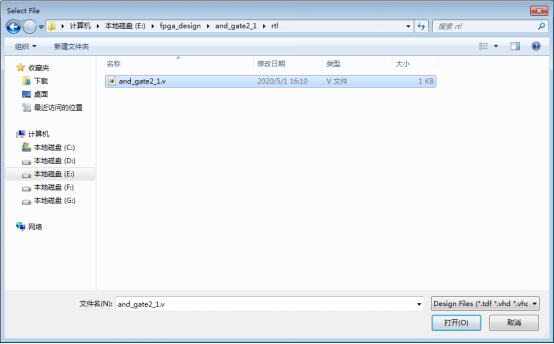

圖52 :尋找添加文件

找到and_gate2_1.v,選中,點擊打開。

圖53 :添加選中文件

注意添加文件的路徑,and_gate2_1.v是存放在rtl文件夾中。

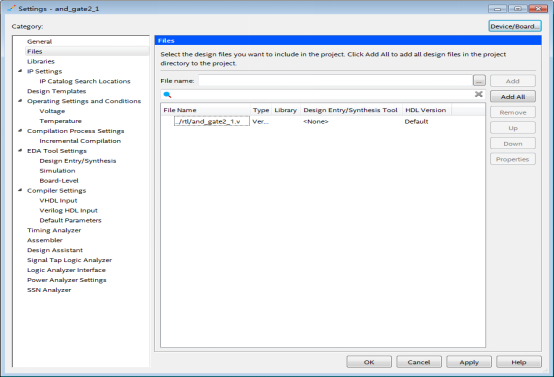

然后點擊apply,OK。就添加成功。

圖54 :確認添加文件

點擊綜合分析,確認綜合分析成功。如果綜合分析失敗,請參考輸入設計中的HDL輸入,查找錯誤的地方。

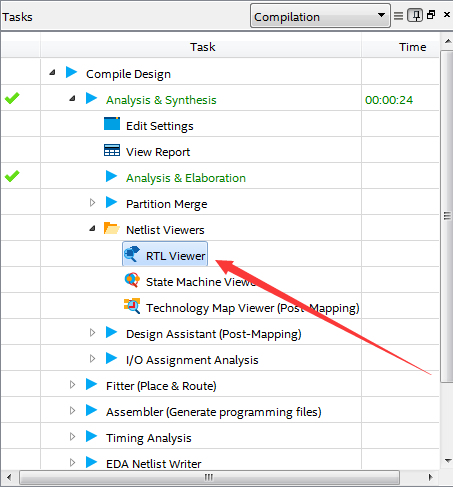

無論是哪一種輸入方式,綜合分析成功。雙擊RTL視圖選項,打開RTL視圖,查看quartus綜合出的電路模型。

圖55 :RTL視圖的選項

在RTL視圖中,綜合出來的電路圖,只是電路模型而已。在FPGA中是沒有與門的,有的只是LUT等效的二輸入與門電路。

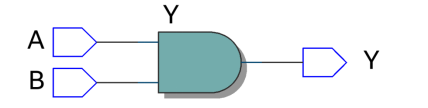

圖56 :RTL視圖的二輸入與門

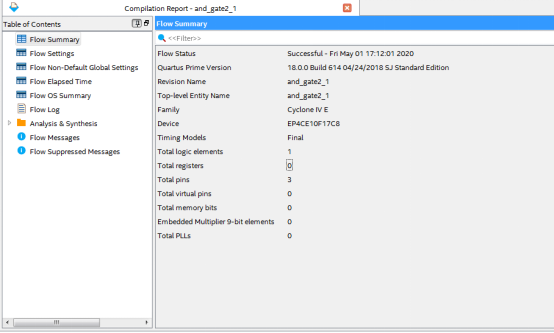

綜合分析成功后,會產生一個報告。

圖57 :綜合分析報告

在報告中,可以看出綜合狀態、軟件信息、工程版本信息、頂層實體、器件系列、目標器件、時序模型、邏輯單元數量、寄存器數量、管腳數量、虛擬管腳數量、存儲器大小、嵌入式乘法器的使用個數、鎖相環使用個數。

只是設計了一個二輸入的與門,所以使用一個邏輯單元,3個管腳,其他都沒有涉及到。

5 RTL仿真

在綜合分析完成后,對于簡單的設計,通過查看RTL視圖中綜合出來的電路模型,就能夠知道所做設計是否正確。但是對于復雜的設計,電路模型比較復雜,無法直接判斷是否設計正確。

如果直接將不知道正確與否的設計加載到板卡中,很多時候無法通過結果直接看出來是否設計比較嚴謹。所以要求設計者在軟件環境下對所做設計進行一定的測試。

仿真是利用模型復現實際系統中發生的本質過程,并通過對系統模型的實驗來研究存在的或設計中的系統。

當所研究的系統造價昂貴、實驗的危害性大或需要很長的時間才能了解系統參數變化所引起的后果時,仿真是一種特別有效的研究手段。

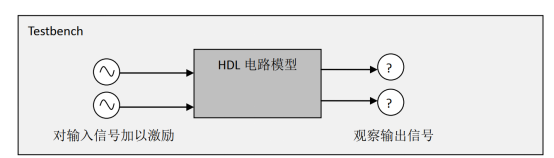

仿真其實就是模擬實際情況。對于電路來說,就是給予合適的輸入,觀測輸出是否和設計時所預想的相同。

圖58 :仿真的示意圖

電路的輸入、中間過程和輸出,都是數字信號,用波形來表示比較直觀。

在真正的電路中,是存在電路延遲的。在仿真時,如果加載的綜合出來的電路模型,那么此時驗證的內容主要是測試模型的邏輯功能是否正確,不考慮延時信息。這種仿真被稱為功能仿真、RTL仿真、前仿真、前仿。

仿真的途徑有兩個,一個是quaruts 自帶的仿真環境,一個是modelsim的仿真環境。

Quartus 自帶的仿真環境

點擊File,New,選擇Uiversity Program VWF。

圖59 :新建VWF文件

點擊OK。

圖60 :VWF初始化界面

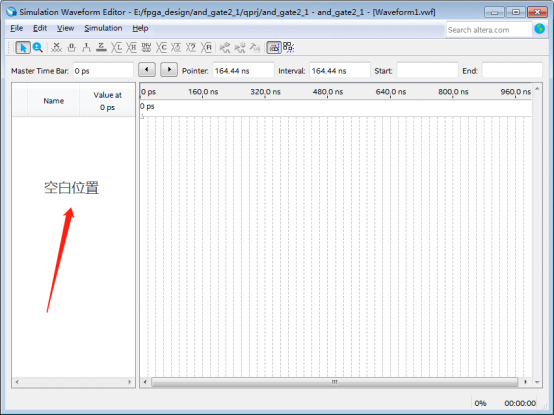

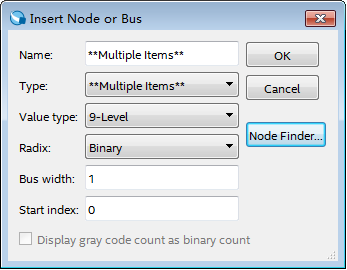

在“空白位置”雙擊。

圖61 :插入節點或者總線

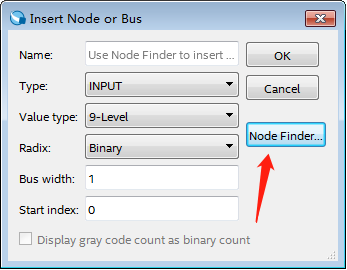

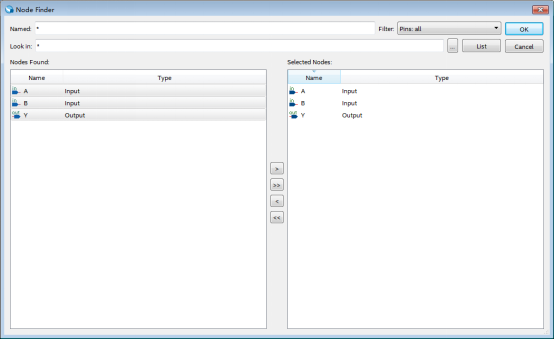

點擊“節點查找”。

圖62 :節點查找

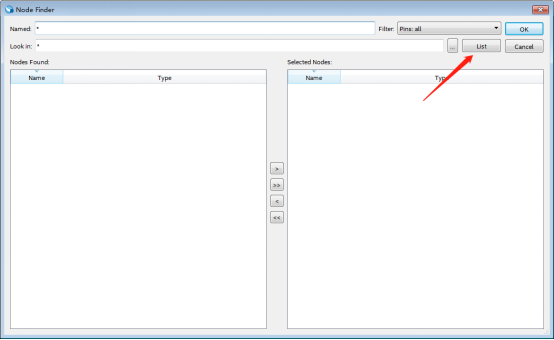

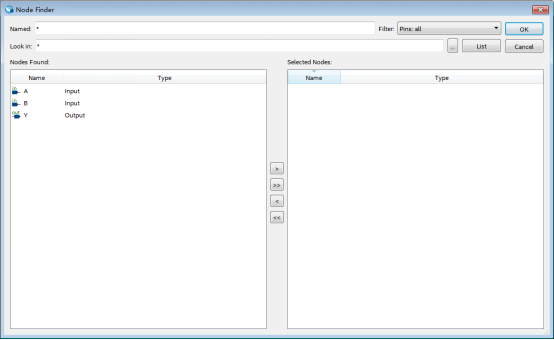

點擊“list”。在“filter”中,默認選擇的是“Pins:all”,當點擊“List”后,“Nodes Found”的界面中會出現所有的端口。

圖63 :查找需要激勵和觀測的信號

選中所有的端口,點擊“>>”,全部添加到“Selected Nodes”中。

圖64 :選擇觀測和激勵信號

點擊“OK”。

圖65 :確定選擇的信號

點擊“OK”。

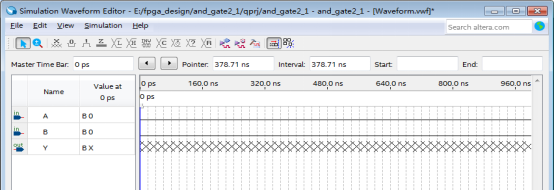

圖66 :選擇信號完成

A端口和B端口是二輸入與門的兩個輸入,只要給A、B兩個端口加載上合適的信號,觀測Y端口的輸出是否正確即可。

A端口和B端口一共只有四種情況“00”、“01”、“10”和“11”,只要將四種情況全部加載一遍即可。

利用鼠標左鍵,選中A端口信號一段或者B端口信號一段,利用上方的置1或者置0按鈕,將輸入信號做成下圖所示:

圖67 :設置輸入信號

設置好輸入信號后,點擊保存,將其保存到qprj文件中。雖然其為仿真文件,但是此文件依然只是quartus軟件能識別,可移植性太差。

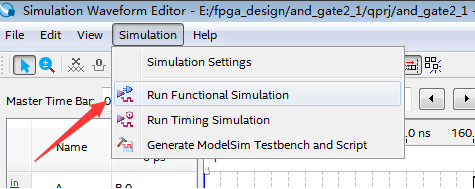

點擊Simulation -> Run Functional Simulation(運行功能仿真)。

圖68 :選擇運行功能仿真

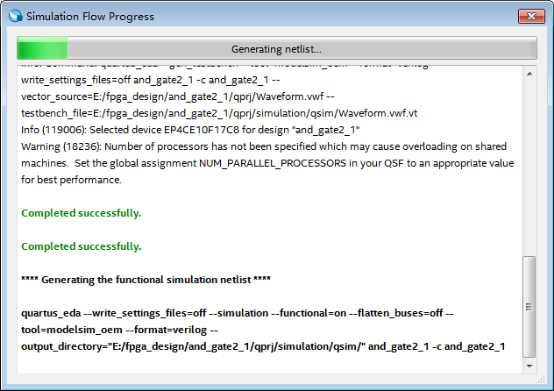

經過一段時間的運行。

圖69 :運行功能仿真的過程

在運行中,如果有報錯,請認真回顧上述步驟。

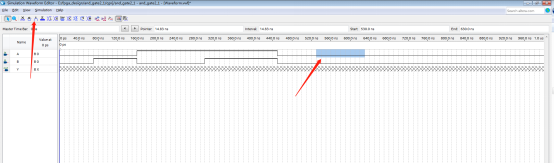

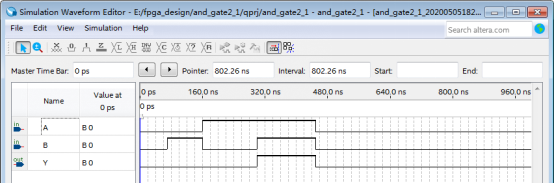

圖70 :功能仿真結果圖

通過分析上述結果圖,容易得出結論:AB“00” –> Y“0”, AB“01” –> Y“0”, AB“10” –> Y“0”, AB“11” –> Y“1”。通過波形的圖的分析,二輸入與門的功能仿真是沒有任何問題的。

利用quartus 自帶的仿真器,可以支持原理圖輸入和HDL代碼輸入;可移植性不強;對于一些復雜的輸入信號,利用這種驅動方式較為復雜;在企業設計研發中,很少有人會用這個工具。

利用modelsim仿真

Mentor公司的ModelSim是業界最優秀的HDL語言仿真軟件,它能提供友好的仿真環境,是業界唯一的單內核支持VHDL和Verilog混合仿真的仿真器。

利用quaruts 自帶的仿真器仿真時,是利用繪制波形的方式進行輸入信號的驅動。但是這種方法移植性不好,無法在modelsim中充當激勵。

在開發中用的比較多的方式是利用HDL的方式進行充當激勵,modelsim軟件會自動抓取HDL代碼中的信號進行繪制波形,用于設計者的觀測。

Modelsim的軟件無法為原理圖的輸入方式進行仿真,所以要將HDL代碼輸入的方式添加到工程,將原理圖輸入的方式移除工程。在企業工程開發時,不建議使用原理圖的方式輸入,移植性太低。所以在后續的章節中,將全部采用代碼的輸入方式進行設計。

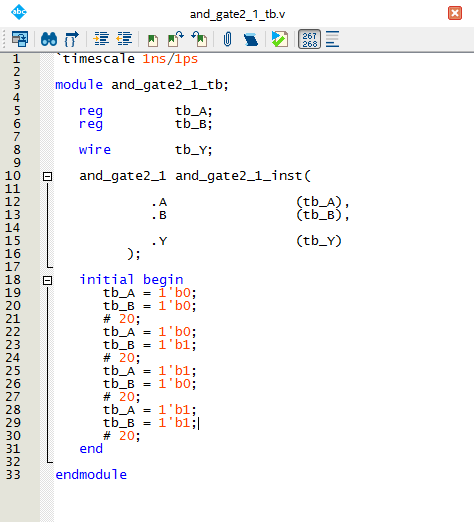

新建一個verilog文件,命名為and_gate2_1_tb,保存到msim中。這個verilog文件是當做測試文件的,命名時,建議名字設置成為被測試模塊的名字,然后后面加上“_tb”。tb為testbench的簡寫。

圖71 :and_gate2_1_tb代碼

`timescale是verilog中定義時間標度的關鍵字。1ns/1ps中的1ns表示時間的單位,在veirlog中不支持直接寫出單位,例:5 ns,ns等時間單位是不被識別的。當定義了1ns為時間單位后,表示時間時,可以直接寫出,例:表示10ns時,可以直接寫10即可。1ns/1ps中的1ps表示時間的精度,由于精度的存在我們可以寫小數。例:表示5.5ns時,可以直接寫5.5。但是也正是由于精度的存在,小數不能無限制向下描述。例:表示5.523ns時,可以成5.523,如果表示5.258963ns,那目前的精度是到不了這么精確的。精度是1ps,因此小數的位數最多能有三位。在設計中,很少用到比ps還要精確的單位,所以一般的時間標度都是1ns/1ps。

Testbench文件也是verilog文件,所以也必須遵從verilog的標準。

在tb文件中,是沒有端口的。在測試時,輸入的信號都由內部產生,輸出信號只要引出到內部即可,仿真器會自動捕獲。所以tb的模塊是沒有端口的。

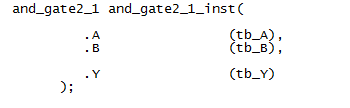

在測試文件中,需要將被測試元件例化進來。例化的方式如下:

圖72 :例化方式

在例化時,首先是模塊名稱(and_gate2_1),后面是例化名稱,這個名字可以任意名字,筆者建議例化名稱要和模塊名稱有一定的關系,筆者采用模塊名稱后加上_inst,表示例化的意思。后面的括號是端口列表,每一個端口的前面加上一個“.”,后面加上一個“()”,此時表示這個端口可以連接線了,連接線放到“()”里面就是連接上了。

對于連接線來說,命名也是任意的,筆者建議連接線的名字和要連接的端口的名字要有一定的關系,筆者采用端口名字前面加tb_,表示tb中的連接線。

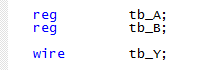

所有的連接線都需要提前定義。在定義時,都可以采用“wire”類型(后續會有更改)。

當例化完成,連接線定義和連接完成后,就需要開始測試了。而測試就是給模塊的輸入賦值,觀測輸出是否正確。

在測試時,我們需要順序性的給出激勵,verilog提供了一種比較簡單的方式“initial”語句。在這個語句中,我們只需要順序性的給出激勵就可以了。“#”表示延時,延時在verilog中是不可綜合的,但是在仿真中,是存在的。

“1’b0”中的1表示位寬為1,’b表示后面的數碼為2進制,0表示數碼為0。

在賦值時,建議采用位寬+進制+數碼的方式進行賦值。

Verilog中,begin end表示中間的語句是一個整體,verilog和C類似,每一個函數或者語句下只能包含一個語句塊。C語言中采用大括號,verilog中采用begin end。

上述的initial語句塊中,描述了tb_A和tb_B被先賦值00,延遲20ns,被賦值為01,延遲20ns,被賦值為10,延遲20ns,被賦值為11。

Verilog語法規定,在initial語句中被賦值的變量,應該定義為reg類型。

圖73 :定義變量(連接線)

在寫完testbench后,可以綜合分析一下。保證沒有任何的語法錯誤。

在仿真之前,需要指定仿真文件。

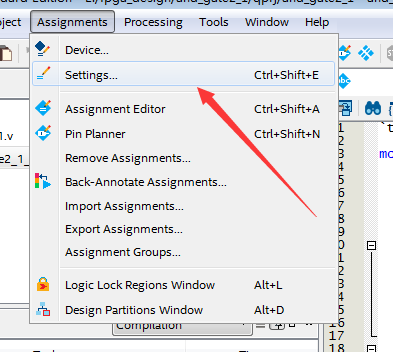

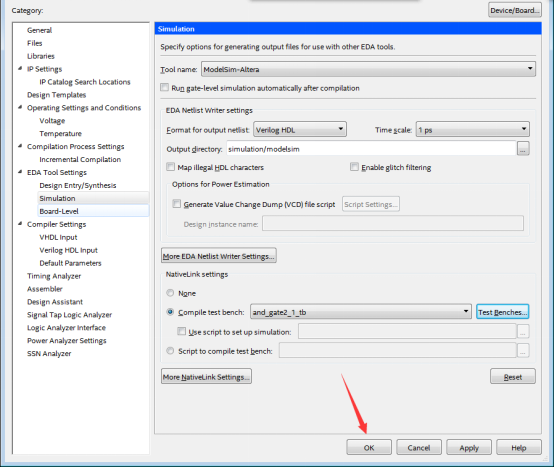

選擇assignments -> settings。

圖74 :選擇settings

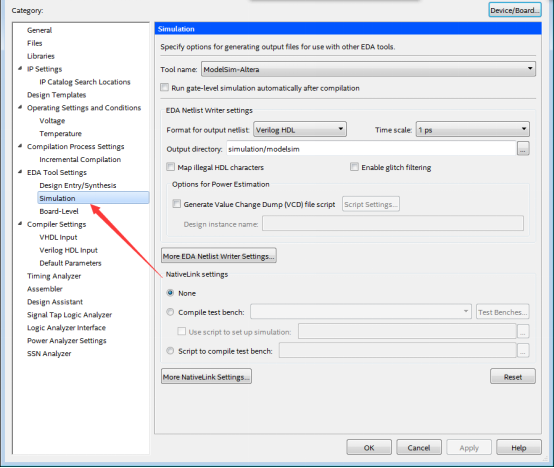

選擇simulation。

圖75 :選擇simulation

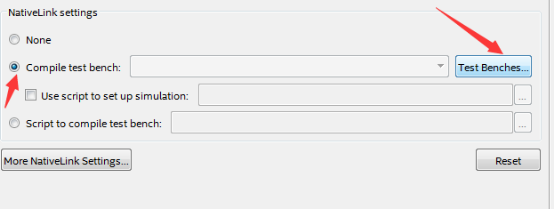

選擇compile test bench 后,選擇后面的test benches…。

圖76 :選擇test benches

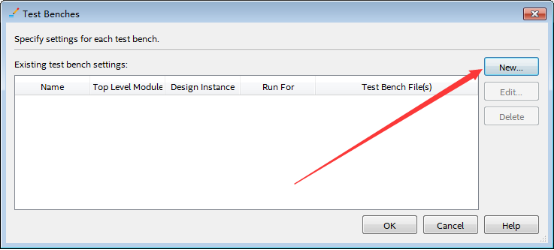

選擇New,新建一個test bench。

圖77 :新建test bench

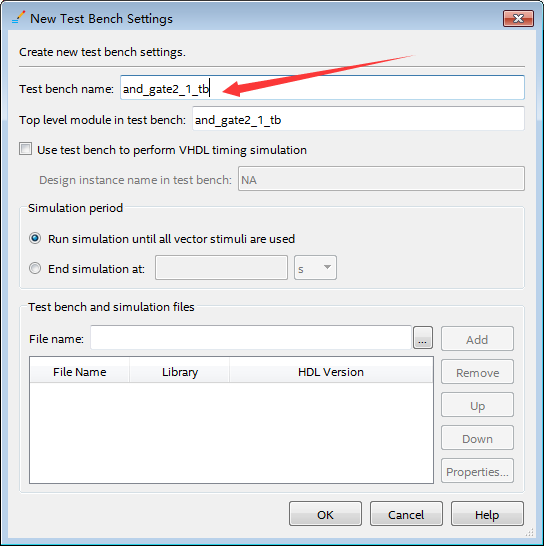

在test bench name的對話框中輸入:and_gate2_1_tb。默認模塊中的頂層實體也是相同的。

圖78 :輸入testbench名字

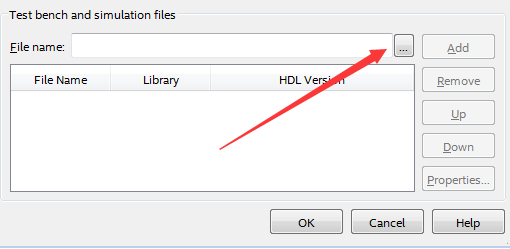

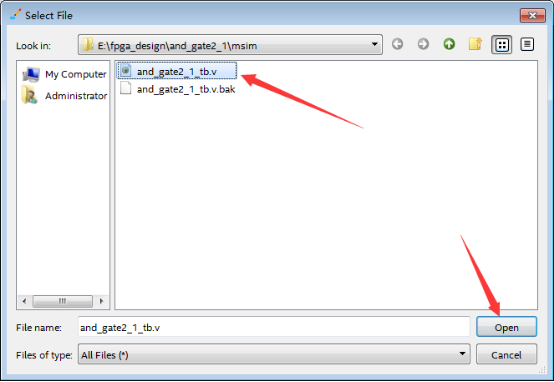

點擊file name后面的三個點,尋找and_gate2_1_tb文件。

圖79 :查找testbench文件

找到msim文件夾中的and_gate2_1_tb,選中后,點擊open。

圖80 :確定testbench文件

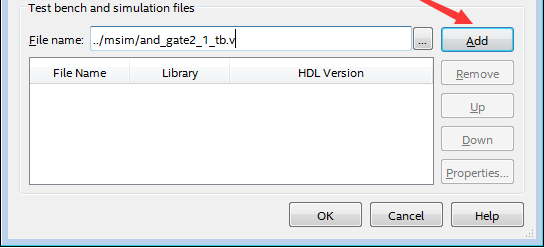

點擊ADD。

圖81 :添加testbench

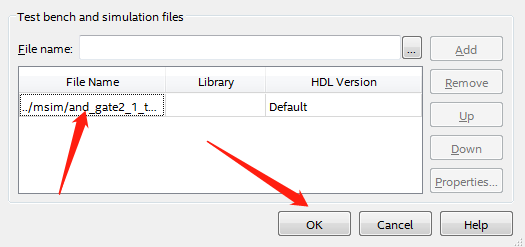

添加成功后,點擊ok。

圖82 :添加成功

點擊ok。

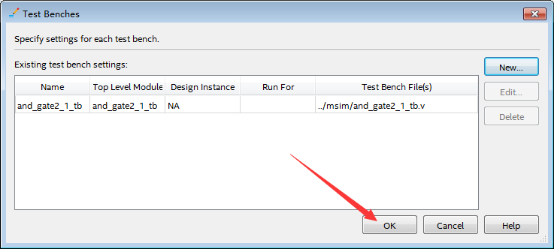

圖83 :新建成功一個testbench

點擊OK。

圖84 :設置完成

在設置完成后,進行綜合和分析。

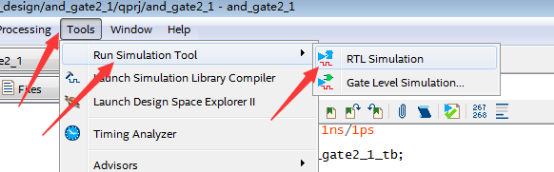

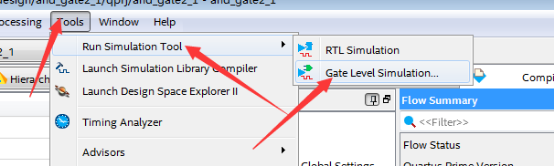

綜合和分析完成后,點擊tools -> Run Simulation -> RTL Simulation。

圖85 :進行RTL 仿真

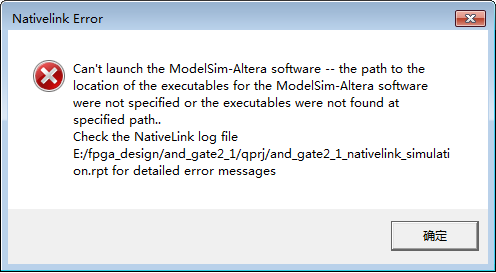

稍微等一段時間,modelsim軟件會自動啟動。如果沒有啟動的話,并且報錯的話,請查看modelsim的關聯位置。

圖86 :無法連接到modelsim軟件

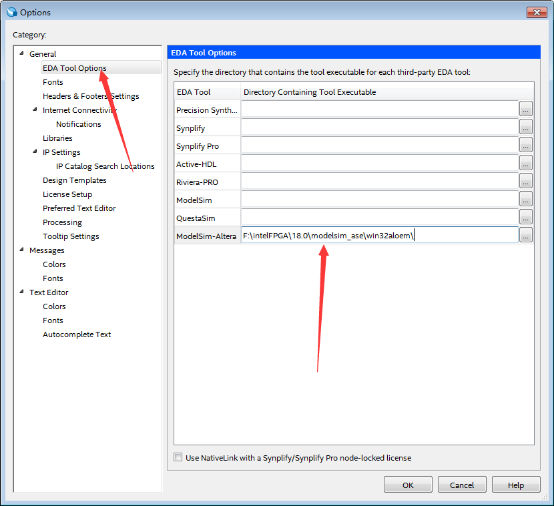

點擊tools 中的options。選擇EDA Toos options。

圖87 :配置關聯路徑

在modelsim-Altera中,看看路徑是否正確(這是筆者的安裝路徑,請自行查看自己的安裝路徑),注意最后那個“”,很多的系統中,沒有它也是不對的。

配置完成后,點擊ok。

重新點擊RTL 仿真。

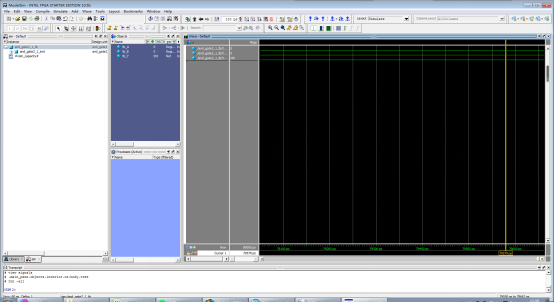

圖88 :modelsim的基本界面

在wave界面中,點擊一下鼠標左鍵,就會出現一個黃色的光標。

點擊“全局縮放”。

圖89 :放大縮小的圖標

在全局縮放前面一個為縮小,后面一個為放大。兩頭的兩個圖標,暫時不考慮。

全局縮放后,所有的波形都顯示到wave窗口中,經過分析,設計正確。

此時就可以關閉modelsim軟件。

圖90 :是否確定關閉modelsim

點擊“是”即可關閉。

6 鎖定管腳

輸入設計后,經過綜合和分析以及RTL仿真后,證明設計的邏輯功能是沒有任何錯誤的。但是設計是在芯片內部進行實現的,如果想要發揮功能,勢必要與外部的邏輯電路進行相連接。

在上述例子中,設計了二輸入與門。我們可以將兩個輸入綁定到任意的兩個管腳上,將輸出綁定到任意一個管腳上。經過下載后,可以在輸入的管腳上加載電平,測量輸出管腳的電平,驗證設計是否正確。

在FPGA學習開發板上,大部分都會有一些按鍵和LED,這些按鍵就可以為輸入提供高低電平,LED就可以檢測輸出的電平值。

所以最好的驗證方法是,將輸入的管腳分配到連接有按鍵的管腳上,將輸出分配到帶有LED的管腳上。

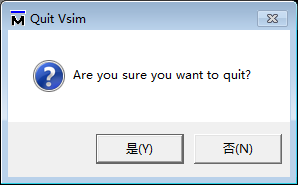

自己制作或者購買的開發板,都會有原理圖。

圖91 :四位按鍵的電路原理圖

經過分析,key1的網絡是直接連接到FPGA芯片上的;按鍵釋放時,key1網絡為高電平,按下時,key1網絡為低電平。其他按鍵原理相同。

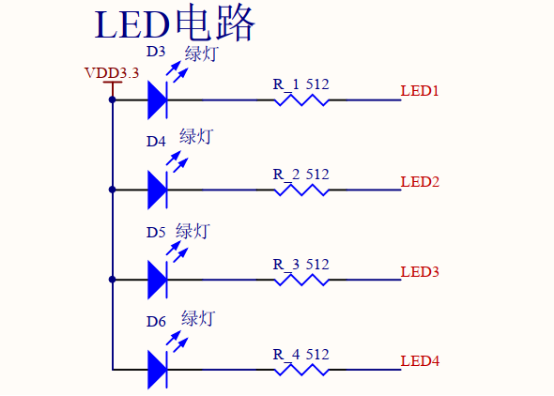

圖92 :LED電路

經過分析,LED1的網絡是直接連接到FPGA芯片上的;當FPGA將LED1網絡置成高電平時,LED是熄滅的;當FPGA將LED1網絡置成低電平時,LED是點亮的。其他的LED原理類似。

不同的電路原理,后續會得出不同的結果。請認真分析原理。

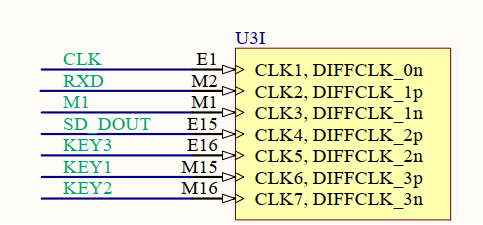

通過查看各個網絡與FPGA的芯片連接關系,就可以得出按鍵、LED電路與FPGA的線連接的IO。

圖93 :外部網絡與FPGA連接示意圖

經過查看,兩個按鍵分別選擇M15和M16。LED選擇G15。

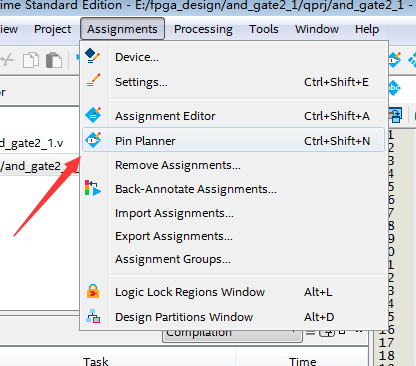

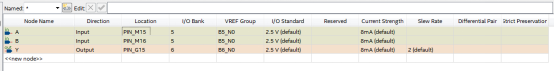

點擊assignments -> pin planner。打開管腳規劃器。

圖94 :打開管腳規劃器

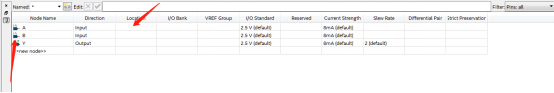

在對應端口的Location標簽下的空白窗位置雙擊。

圖95 :準備輸入管腳號

輸入對應的管腳號。

圖96 :輸入對應的管腳號

輸入完成后,點擊關閉即可。

點擊綜合和分析,等待綜合分析完成。

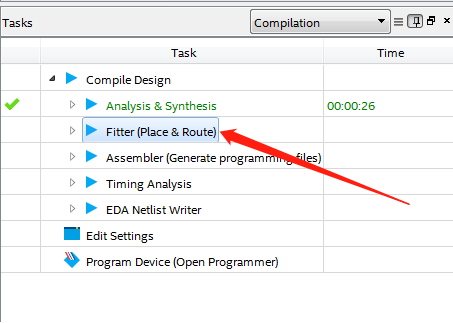

7 布局布線

綜合分析只是將外部的輸入轉換成為對應的電路模型或者對應FPGA的電路模型,我們可以對電路模型進行RTL仿真,來排除邏輯功能的錯誤。

在FPGA片內實現的話,就需要對模型進行“實地”布置,利用FPGA片內的資源來實現模型,并且要固定好位置和連接線。這部分操作稱為適配,也被稱為布局布線。

圖97 :布局布線選項

雙擊Fitter即可進行布局布線。

布局布線后形成的報告有可能和之前綜合分析形成的報告中的資源利用有所出入,最終我們以布局布線后的資源為準。

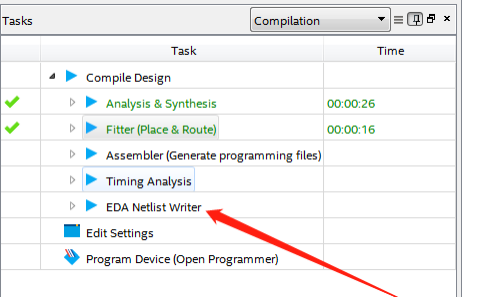

8 時序仿真

在真正的電路中,是存在電路延遲的。在仿真時,如果加載的綜合出來的電路模型,那么此時驗證的內容主要是測試模型的邏輯功能是否正確,不考慮延時信息。這種仿真被稱為功能仿真、RTL仿真、前仿真、前仿。

在仿真時,也可以加載布局布線后的電路模型,那么此時驗證的內容主要是測試模型的延時是否能夠達到我們的要求。這種仿真被稱為時序仿真、后仿真、后仿、門級仿真。

雙擊EDA Netlist writer,產生后仿真所需要的模型。

圖98 :EDA Netlist Writer選項

啟動后仿真。

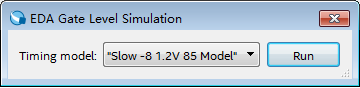

圖4-89 :啟動后仿真

直接默認選擇,點擊RUN。

圖99 :選擇時序模型

綜合器給出了外部不同條件下的時序模型,這里先不敘述他們各自的作用,后續時序分析中,會專門提到各個模型的作用。

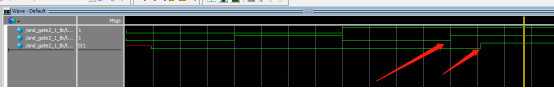

圖100 :二輸入與門后仿真波形圖

在輸入信號都變為高后,輸出信號沒有立刻變化為高,而是延遲了一段時間后,才變為高電平。

在二輸入與門中,電路的延遲對于我們來說是可以接受的,沒有任何的要求。在后續的一些復雜的電路中,就要求電路的延遲不能太大,否則就會影響電路的功能。

時序仿真在企業設計中用的不太多,對于時序的很多問題,采用靜態時序分析來查看。所以在后續的設計中,時序仿真將不在重點敘述。

9 生成配置文件并下載

在布局布線后,需要將對應的結果下載到FPGA片內。對于模型來說是無法下載的,只有通過編譯,形成某種文件才可以下載。

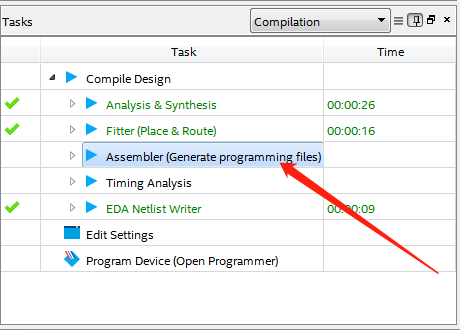

雙擊Assembler(Generate programming files),產生配置文件。

圖101 :產生配置文件選項

利用下載電纜連接FPGA開發板和PC。Intel FPGA的下載器為usb blaster ,當連接到PC后,需要安裝驅動。

將FPGA開發板通電。

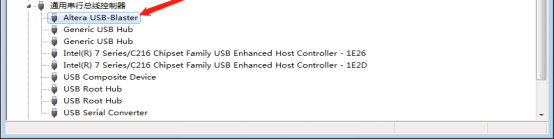

打開設備管理器。在通用串行總線控制器的下面,觀看有沒有Altera USB blaster。如果有的話,證明已經有了驅動,不需要再次安裝。如果沒有Altera USB blaster,在其他設備中,觀測有沒有“其他設備”。如果沒有“其他設備”的話,就需要認真的檢查開發板的各個連接線的連接情況。

圖102 :Altera USB blaster驅動

圖103 :其他設備

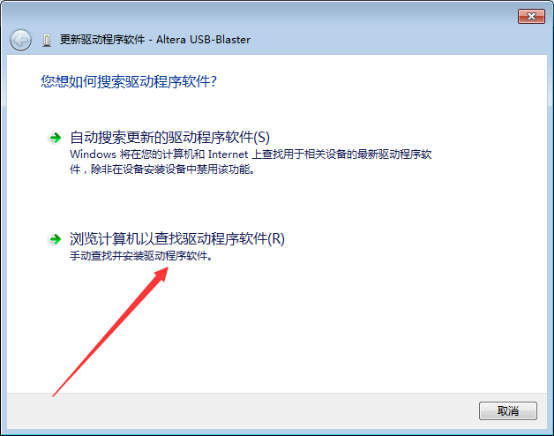

選中USB-Blaster,右擊,選擇更新驅動程序。

圖104 :如何搜索驅動程序軟件

選擇“瀏覽計算機以查找驅動程序軟件”。

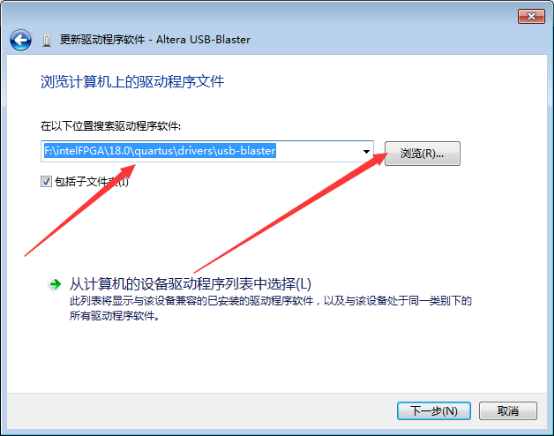

圖105 :瀏覽計算機上的驅動程序文件

點擊“瀏覽”,按照圖4-96中所示路徑(quartus 的安裝路徑,讀者請尋找自己的路徑,后面的路徑是相同的)選擇文件夾,然后點擊確定。

點擊下一步,開始安裝驅動。安裝過程中,PC會詢問是否安裝,點擊安裝即可。

安裝完成后,可以將下載線從PC上重新插拔一下。在通用串行總線控制器中就有Altera USB Blaster的驅動。

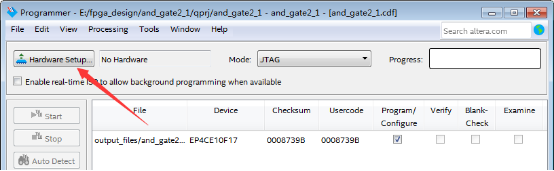

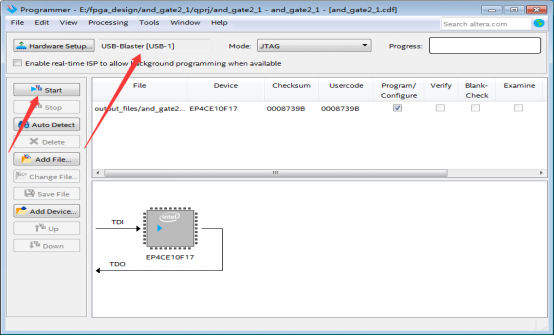

安裝好驅動后,點擊quartus 界面中tools的programmer。點擊Hardware setup。

圖106 :下載界面

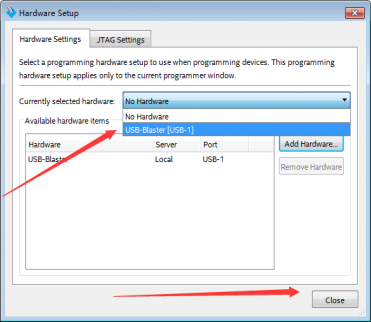

選擇USB Blaster后,點擊close。

圖107 :選擇USB Blaster

選擇USB Blaster后,下載界面中顯示出,USB Blaster。此時直接Start即可開始下載。右上角會有下載進度條。

圖108:下載界面

如果下載界面沒有可下載的文件,可以點擊add files,在qprj中的output files文件夾中,有一個后綴為.sof文件。選擇后,下載即可。

下載完成后,此界面就可以關閉。詢問是否保存時,選擇否即可。

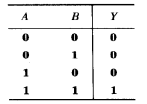

當配置完成后,我們就可以進行驗證。按下按鍵,分析LED的燈的狀態。我們做的是二輸入與門,它的真值表如下:

圖109 :二輸入與門真值表

通過記錄按鍵和LED的狀態,也會得到一組真值表。

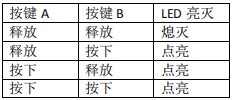

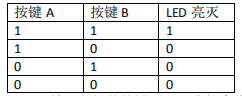

圖110 :二輸入與門的按鍵和LED功能真值表

通過分析按鍵和LED的工作原理,可以化簡真值表。

圖111 :二輸入與門的按鍵和LED化簡真值表

通過分析兩個真值表,確認功能正確。

不同的按鍵和LED原理,可以對應去分析。

大多數FPGA的內部實現是用SRAM等效出來的電路,SRAM是一種掉電丟失的器件。所以FPGA下載成功后可以正常運行,但是掉電后,FPGA會丟失之前配置的所有信息。

這種情況非常不利于產品的研發,設備斷電時常有的事情,而斷電后再上電,還是希望FPGA能夠正常工作的。

正是由于FPGA掉電丟失所有信息,所以在FPGA的周邊會配置一塊掉電不丟失的存儲器(flash),可以將配置信息存儲到存儲器中,FPGA每次上電后讀取存儲器的內容即可。

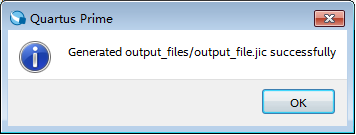

向flash中存儲信息,需要將上述.sof文件轉換為.jic文件。

在quartus 界面中,點擊file -> Convert Programming file。

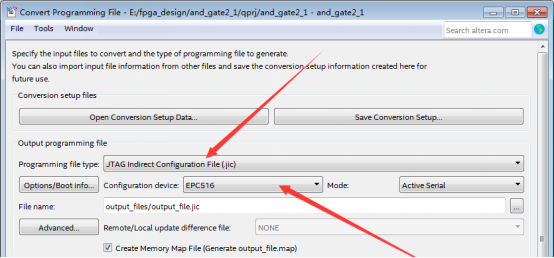

圖112 :轉換配置文件

在programming file type中選擇jic文件,在configuration device中選擇EPCS16。EPCS16是altera 公司推出的一款flash的型號,國內大多數開發板上不是altera公司推出的芯片,但是能夠兼容。EPCS16是一個16Mbit的flash。讀者需要觀察自己手中開發板的flash型號,找到與之對應的altera公司的兼容產品,選擇即可。

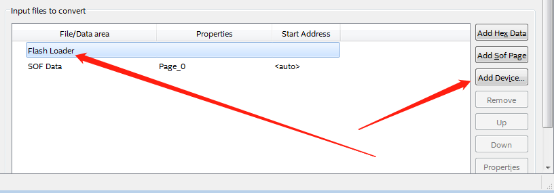

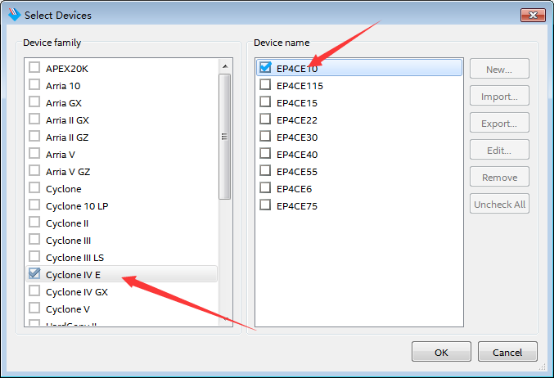

圖113 :添加flash loader

選擇flash loader,點擊add device,選擇ep4ce10,單擊OK。

圖114 :選擇FPGA系列

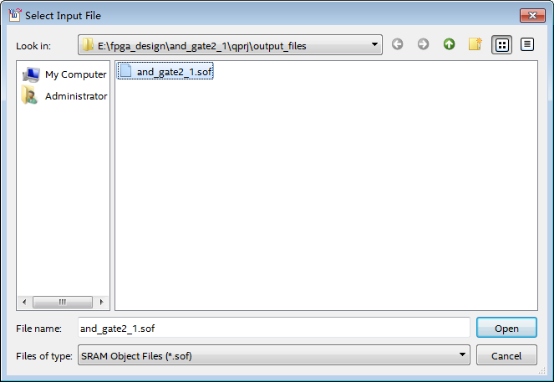

選擇SOF data,點擊add file,找到之前的配置文件.sof,點擊open。

圖115 :選擇配置文件

點擊generate,開始生成.jic文件。

圖116 :生成文件成功

點擊OK后,關閉界面即可。

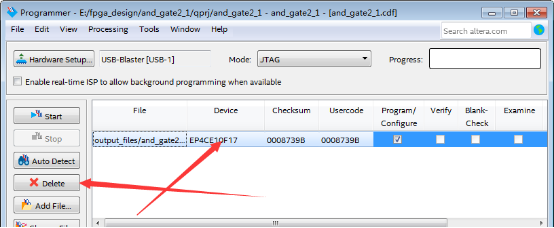

重新打開下載界面。選擇下載文件,點擊delete。

圖117:移除默認下載文件

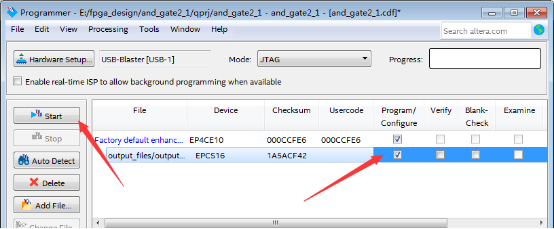

點擊add files,將生成的.jic文件(在qprj中的outputfiles文件中)添加進來,勾選program/configure,然后點擊start。

圖118:下載.jic文件

下載此文件速度比較慢,請耐心等待。

下載后,FPGA不能夠正常工作,需要斷電后上電,FPGA就可以正常工作了。

以后每次斷電再上電,都可以正常工作。

本文的1到9小節就是正常的開發流程。在此過程之外,還有可能會加入一些其他的流程,例:功耗分析、時序約束等等。

-

FPGA

+關注

關注

1636文章

21841瀏覽量

608514 -

芯片

+關注

關注

459文章

51603瀏覽量

429935 -

intel

+關注

關注

19文章

3487瀏覽量

186874 -

數字電路

+關注

關注

193文章

1633瀏覽量

81084 -

開發板

+關注

關注

25文章

5221瀏覽量

99194

原文標題:FPGA零基礎學習系列精選:Intel FPGA 開發流程(超詳細)

文章出處:【微信號:數字芯片設計工程師,微信公眾號:數字芯片設計工程師】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

【下載】《FPGA設計指南:器件、工具和流程》

華為FPGA設計流程指南

FPGA的設計流程是怎么樣的?FPGA設計流程指南詳細資料免費下載

Intel FPGA開發流程指南

Intel FPGA開發流程指南

評論