現(xiàn)在的深亞納米工藝的設(shè)計(jì)中,低功耗已經(jīng)是一個(gè)日漸總要的主題了,尤其是移動市場蓬勃發(fā)展起來之后,功耗的要求越來越嚴(yán)格,據(jù)傳,在高級的手機(jī)系統(tǒng)開發(fā)的過程中,系統(tǒng)架構(gòu)的設(shè)計(jì),已經(jīng)精確到每一個(gè)服務(wù)模塊的毫安時(shí)(mAH)的級別,所以如果你的芯片功耗控制不下來,很有可能會被手機(jī)生產(chǎn)廠家踢出局。

在低功耗的世界里,我們有很多方法可做,譬如提高設(shè)計(jì)工藝(工藝節(jié)點(diǎn)越高,功耗就越小)UPF策略,代碼優(yōu)化等等。其中的clock gating方法就是一個(gè)解決內(nèi)部功耗的有效辦法

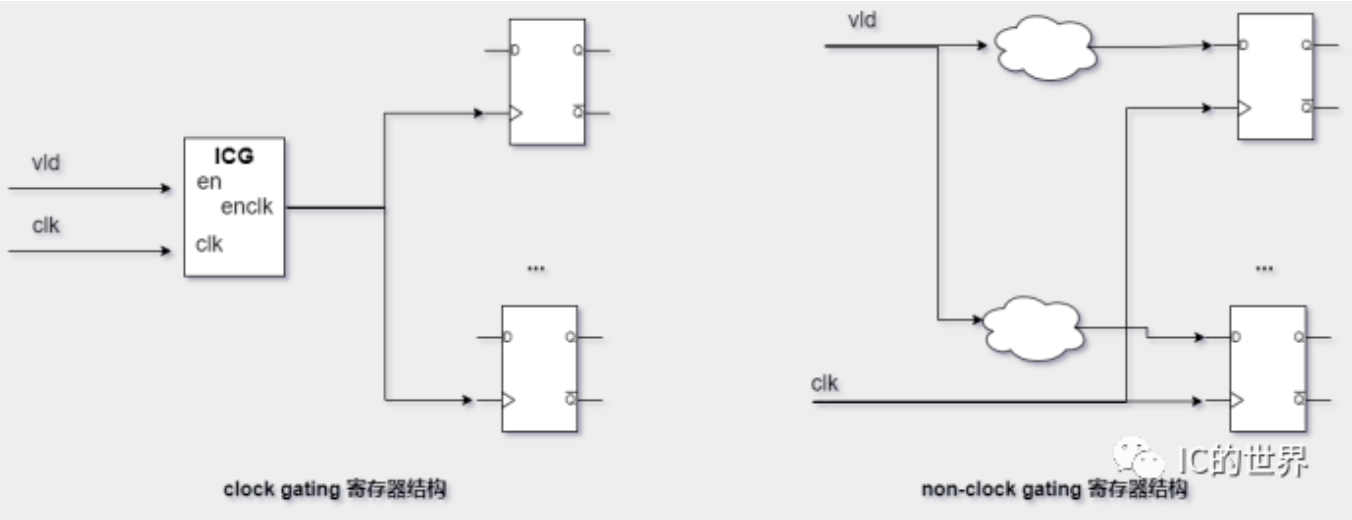

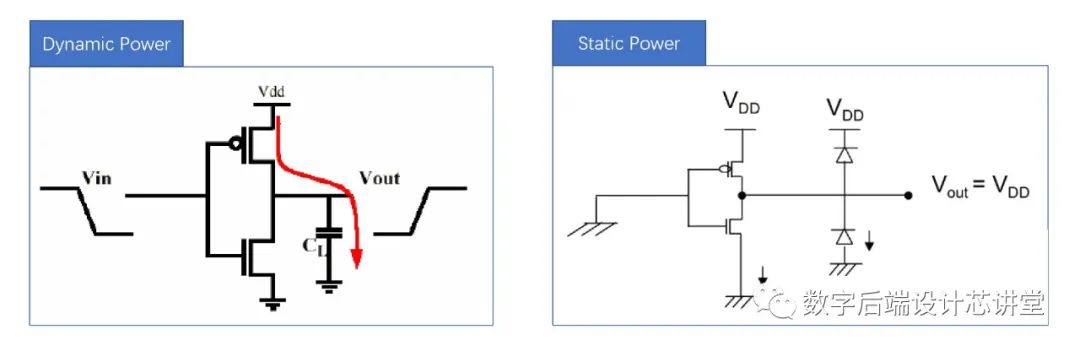

Clock gating從原理上講,就是在FF的clock 的輸入通路上,加入額外的邏輯,來使得FF在不發(fā)生變化的情況下,clock端沒有反轉(zhuǎn),如果不采取這個(gè)策略,那么FF的clock pin是長時(shí)間翻轉(zhuǎn)的,在D/Q都不翻生變化的時(shí)候,帶來了額外功耗消耗,采用clock gating就可以有效境地這種損耗

從用途上講,一般將Clock gating分為如下兩類:

1:RTL實(shí)例化的clock gating cell

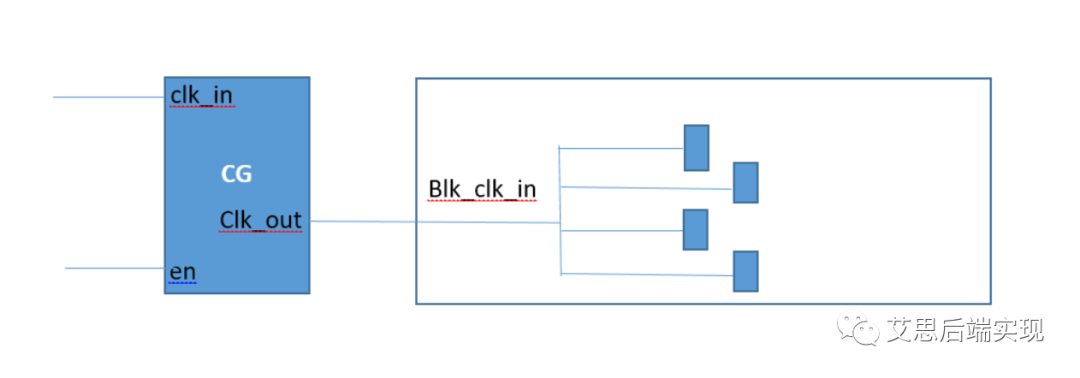

在很多的前端設(shè)計(jì)中,我們都會認(rèn)為的實(shí)例化primitive clock gating cell,這里是按照前端的設(shè)計(jì)要求來的,一般這樣的GC都是接近于clock 的源頭,譬如一個(gè)模塊的輸入clock,我們使用一個(gè)實(shí)例化的GC來作為這個(gè)clock 的控制端,在不需要的時(shí)候,可以直接使用寄存器把他關(guān)斷,從而達(dá)到節(jié)省模塊級power的目的

這種GC結(jié)構(gòu),在結(jié)構(gòu)上后端是不用干預(yù)的,但是由于這種GC的fanout 都很大,在某種情況下可能會引起比較悲觀的setup violation。這個(gè)我們會在后邊仔細(xì)描述

2:綜合工具推斷出(inferred )clock gating cell

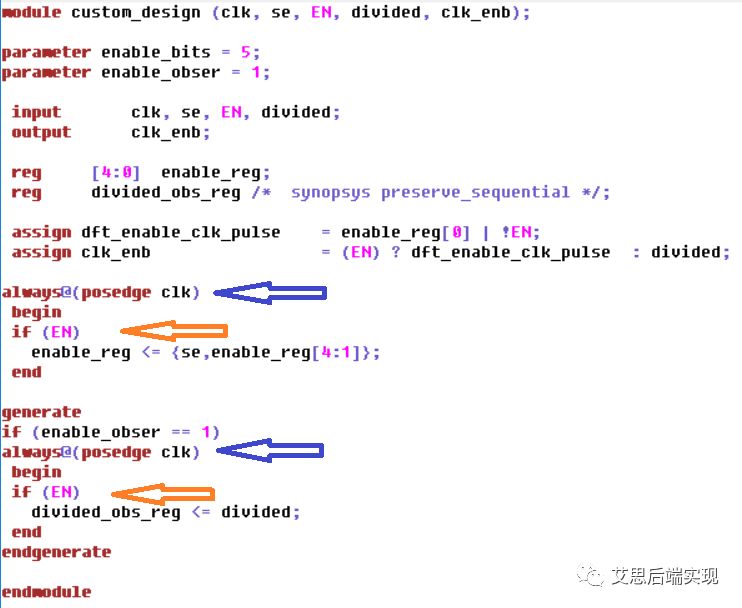

這種推斷出的CG是基于綜合器對RTL的理解,首先,我們的設(shè)計(jì)需要遵循一定得大媽風(fēng)格(coding style),這是工具分析的基礎(chǔ),我們來看下面這段代碼

藍(lán)色箭頭所指是clock的edge檢測,這里是一個(gè)if 語句的開始,而后如橙色箭頭所指,在clock edge的這個(gè)function里邊,使用EN來做判別,如果EN為1的時(shí)候,產(chǎn)生賦值操作,這是一個(gè)標(biāo)準(zhǔn)的帶同步enable的寄存器語法。

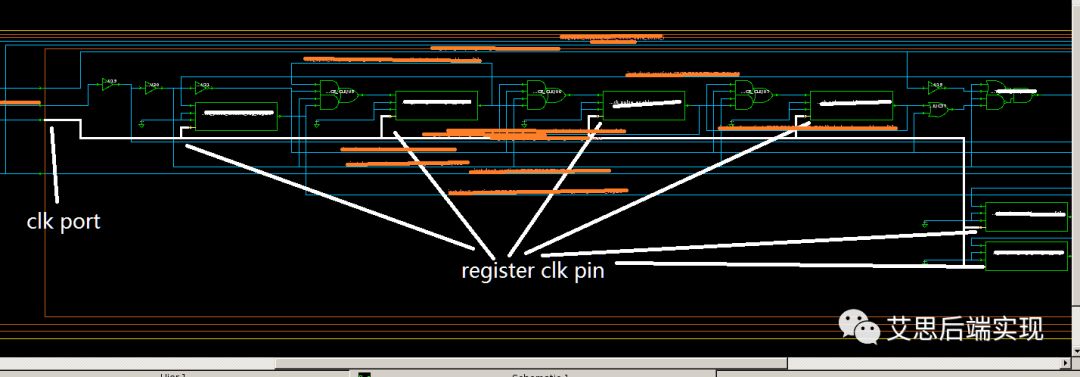

綜合器會按照約定的規(guī)則來解析rtl code,然后產(chǎn)生對應(yīng)的網(wǎng)表。按照通常的綜合結(jié)果(compile_ultra),會得到下面這個(gè)結(jié)果

模塊輸入端的clock port會直接連接到所有的FF clock pin 上邊,通常的器件庫里邊,沒有帶EN端的DFF,這是一種簡化設(shè)計(jì),因?yàn)樗械腇F EN pin,都可以和D pin做組合邏輯,從而達(dá)到控制輸出的結(jié)果。從土里可以看到,這里的EN也是被拉到了FF’D pin前級的組合邏輯的輸入端,從而達(dá)到控制FF輸出的結(jié)果。

這個(gè)時(shí)候,是沒有clock gating的設(shè)計(jì)的,工具嚴(yán)格遵守RTL的設(shè)計(jì)產(chǎn)生了這段網(wǎng)表結(jié)構(gòu)。

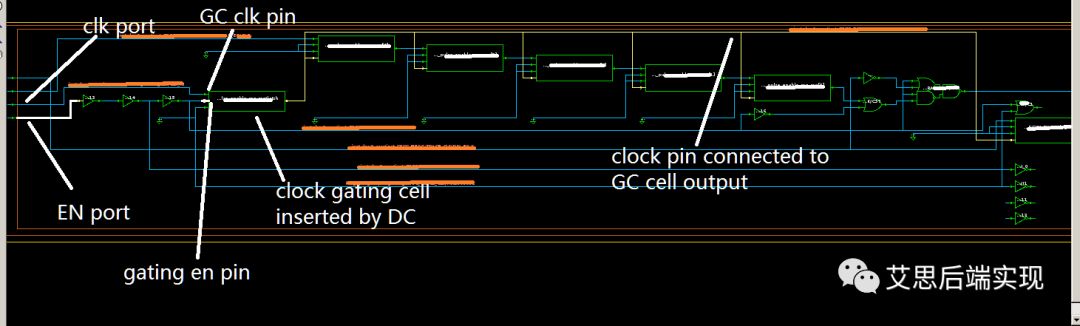

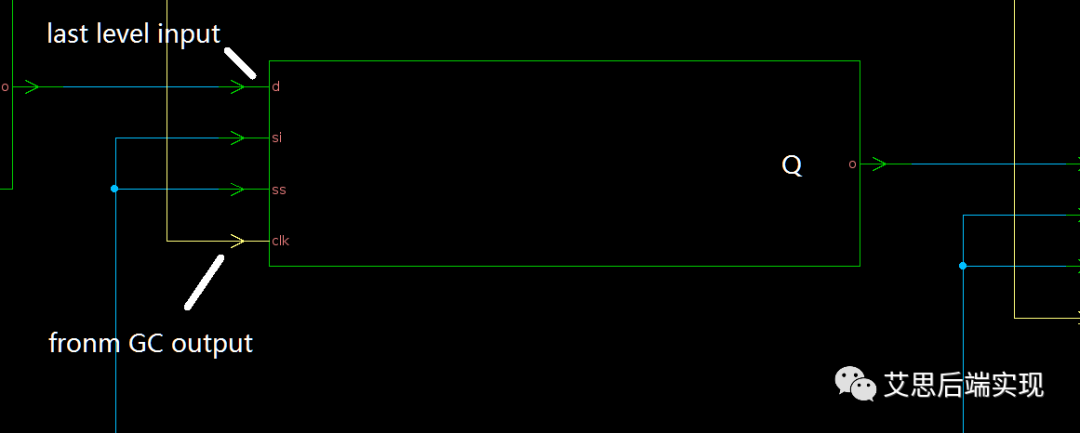

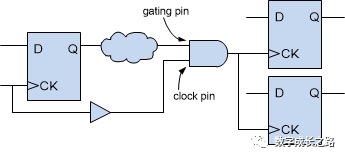

如果在綜合的時(shí)候,打開inferred clock gating 選項(xiàng)(compile_ultra –gate_clock),這個(gè)時(shí)候會得到下面的這個(gè)結(jié)構(gòu)。

這個(gè)時(shí)候的網(wǎng)編結(jié)構(gòu)發(fā)生了變化,在緊跟clock port的后面,多了一個(gè)CG,EN的port 從之前的鏈接到各個(gè)FF 的D pin,到現(xiàn)在只連接到了clock gating cell的en pin上,通過控制FF的clk pin,來達(dá)到僅在EN使能的時(shí)候翻轉(zhuǎn)clock來刷新FF的輸出,從而達(dá)到省電。

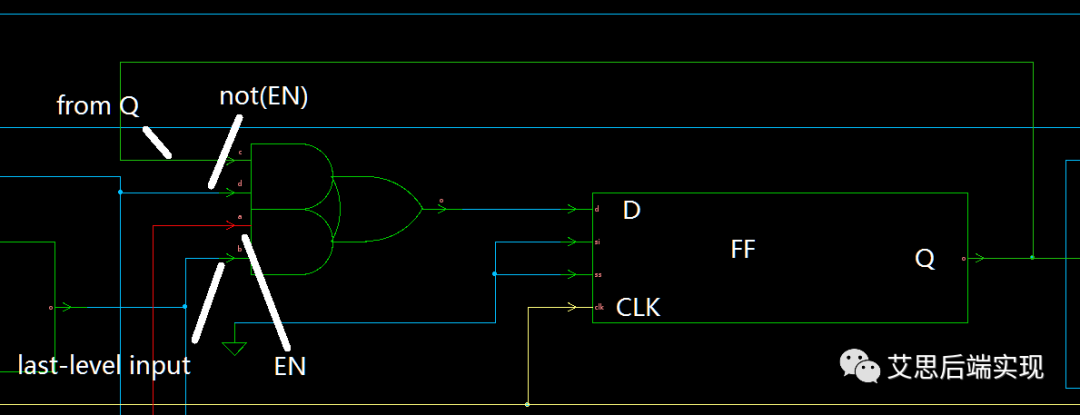

由于在沒有使用CG之前,由于FF需要不停地刷新,DC為了保障FF的輸出在EN端非使能的時(shí)候保持當(dāng)前狀態(tài),所以一定有一條從Q到D的回路來保證FF的輸出保持不變,類似下圖

FF’D pin 前面的是一個(gè)四輸入與或門,在EN為0的時(shí)候,F(xiàn)F會把Q的值反復(fù)刷新,盡管輸出Q不改變,但是短路功耗是少不了的。

在使用了gate clock 以后,F(xiàn)F的結(jié)構(gòu)變成了

可以看到,這里的FF的D輸入端,變得更為簡單了,以為所有前后級都被掛載到了同樣的CG下面,只有當(dāng)CG有輸出clock的時(shí)候,這些FF才進(jìn)行工作,工具就不用創(chuàng)建那些組合邏輯來考慮EN不使能的情況了。

就相同設(shè)計(jì)的面積比較,采用inferred CG策略的結(jié)果還可以節(jié)省面積

Area with CG: 8.0997

Area without CG: 8.3790

在一個(gè)3M gate-count的完整設(shè)計(jì)里邊,可以看到,當(dāng)打開gate_clock選項(xiàng)的時(shí)候,會增加大約7k的CG cell,時(shí)序邏輯大概增加了6%的面積,但是整個(gè)設(shè)計(jì)的std-cell的面積(組合加時(shí)序)反而降低了4%,從這方面看,綜合器的這個(gè)功能對絕對面積和功耗都是有貢獻(xiàn)的

討論完CG的好處后,我們再來看一下Clock gating 的類別:

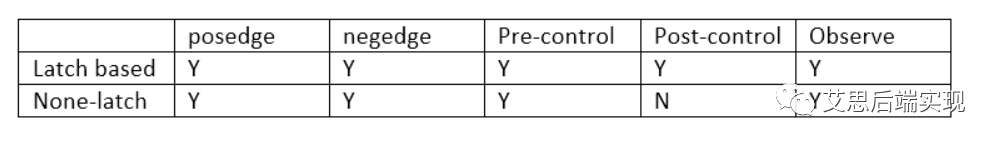

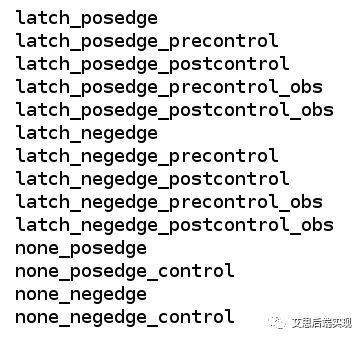

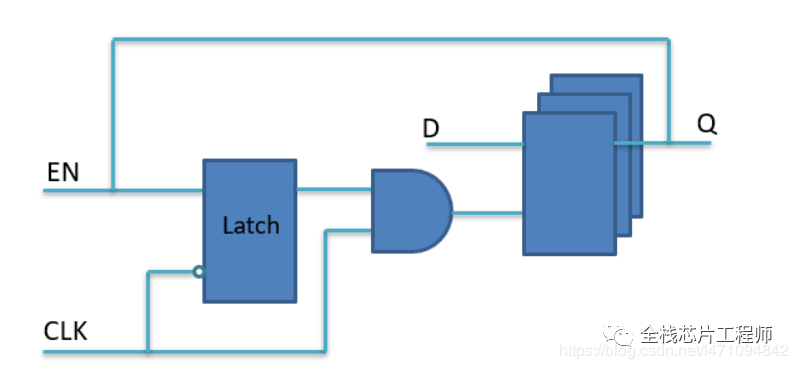

先看一下這個(gè)表格。通常上來講,CG分為兩類,一種是帶latch的,另外一種是不帶

latch的,由組合邏輯構(gòu)成。

這里的模型規(guī)則如下

Posedge:

o Latch based:clk負(fù)沿敏感的latch

o None-latch:非或門結(jié)構(gòu)的CG

Negedge:

o Latch based:clk正沿敏感的latch CG

o None-latch:與門結(jié)構(gòu)CG

Pre-control:

o Latch based :latch的EN輸入前插入一個(gè)或門,從而帶入TE的管控

o None-latch: 在組合邏輯的EN輸入側(cè)插入一個(gè)或門,從而帶入TE的管控

Post-control:

o Latch based :latch的output輸出后插入一個(gè)或門,從而帶入TE的管控

o None-latch: 不支持

Observe:

o再有pre/post control的設(shè)計(jì)中監(jiān)控與門中非TS管控測的信號

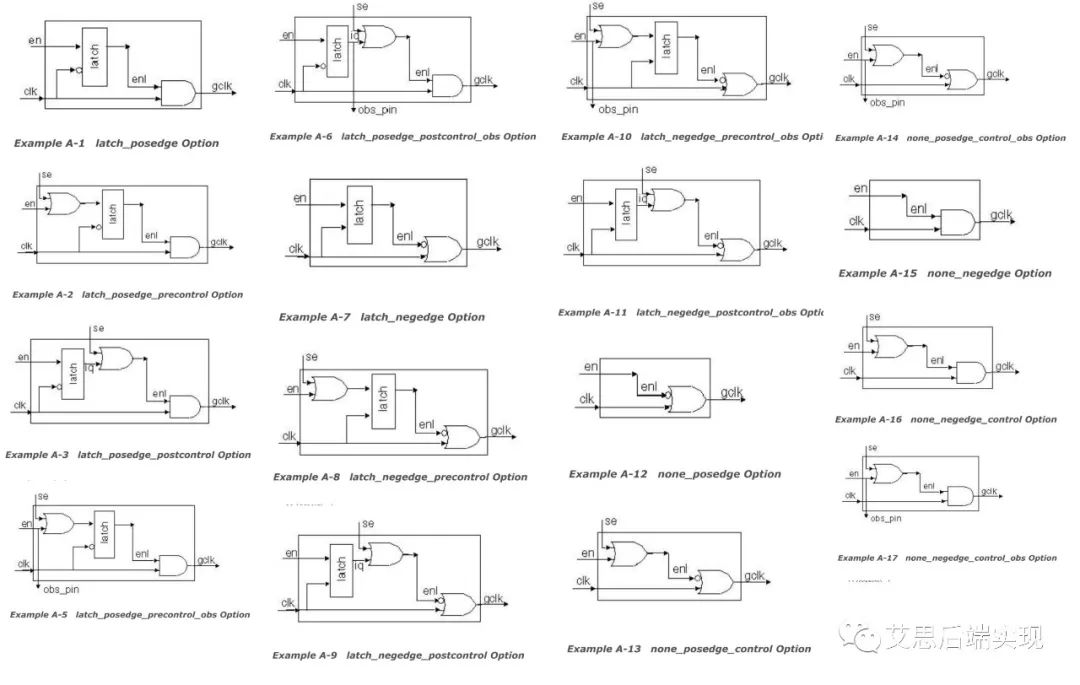

借用新思的電路圖來給大家詳細(xì)的示例(侵刪)

由于clock是敏感信號 ,一般推薦使用latch-based gating CG,這要可以有效地過濾EN上的毛刺。

有了上邊的知識,那么工具是如何識別和插入CG的的呢?

在綜合的時(shí)候,需要在你的綜合環(huán)境里邊定義工具自動插入時(shí)可已使用的CG cell類型,然后喚起compile_ultra命令即可完成CG插入:

set_clock_gating_style -pos {integrated:CG_CELL_NAME} -control_point before -num_stages 4

compile_ultra –gate_clock

用戶可以在compile結(jié)束后,使用report_clock_gating命令來查看數(shù)據(jù)庫里邊的CG情況。

這個(gè)報(bào)告很有意思,他可以打印出數(shù)據(jù)庫里所有被CG控制的FF的情況,同時(shí)也會列出來沒有被CG控制的FF的情況,并且會生成一些比率報(bào)告,有興趣的同學(xué)可以仔細(xì)了解一下。

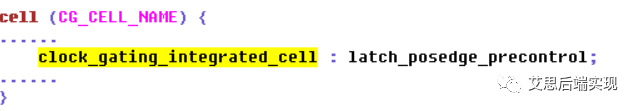

此外,這里邊的CG_CELL_NAME,這個(gè)cell是一個(gè)真實(shí)存在在你的std-cell庫里的實(shí)際CG,并且這個(gè)lib_cell必須要有一個(gè)特殊的屬性:

DC只有看到這個(gè)屬性的時(shí)候,才會認(rèn)為這是一個(gè)真實(shí)可信的CG。而后按照他后邊屬性說明來進(jìn)行inferred CG insertion,后面的屬性無外乎我們前面表格里邊羅列的那些屬性,具體名詞如下:

當(dāng)然,DC也支持一些組合邏輯的CG的創(chuàng)建,如果你使用如下命令,DC會插入相應(yīng)的none-lath結(jié)構(gòu)的CG

set_clock_gating_style -pos {buf nand inv}

在同步設(shè)計(jì)的架構(gòu)下,不推薦使用這樣的gating 結(jié)構(gòu),由于這是拿兩三個(gè)蘇合邏輯器件搭乘的,后期的timing closure是很難做的,推薦使用library里邊latch-based的CG。

上邊用了一定的篇幅講述了一下CG的特點(diǎn)、原理和初步實(shí)現(xiàn)。但是這還沒有結(jié)束,應(yīng)為還有l(wèi)ayout的實(shí)現(xiàn)要考慮

Clock_gating作為clock tree的一部分,在做layout的時(shí)候,有更多的因素需要考量

首先,所有的latch based CG都有一組setup/hold timing arc,就是clk –> EN的timing check

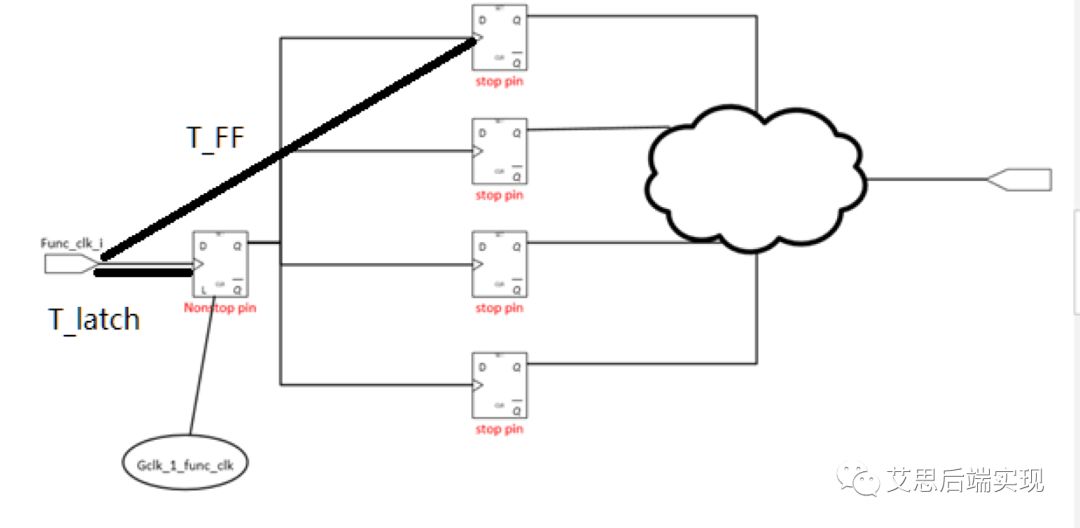

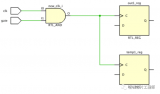

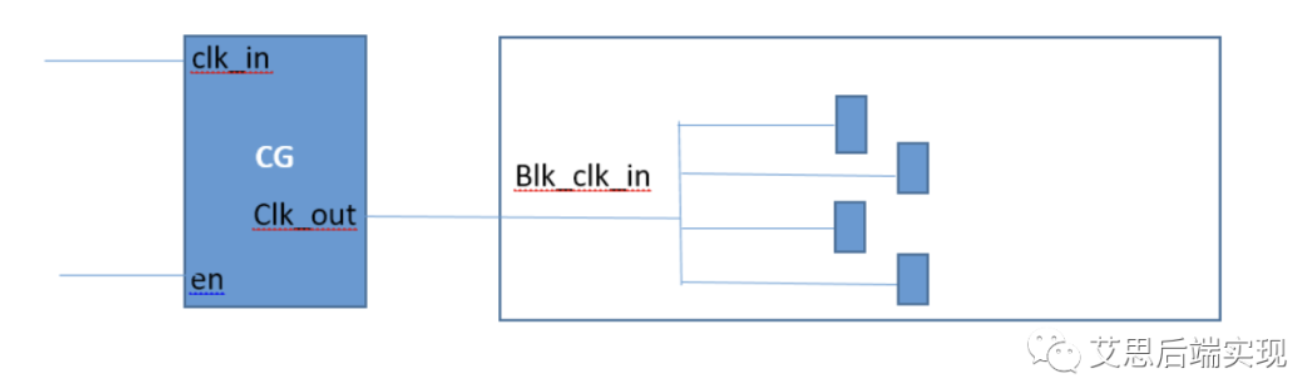

其次,在CTS的時(shí)候,clock-gating被當(dāng)作了一個(gè)none-stop pin而非一個(gè)stop pin如下圖示例:

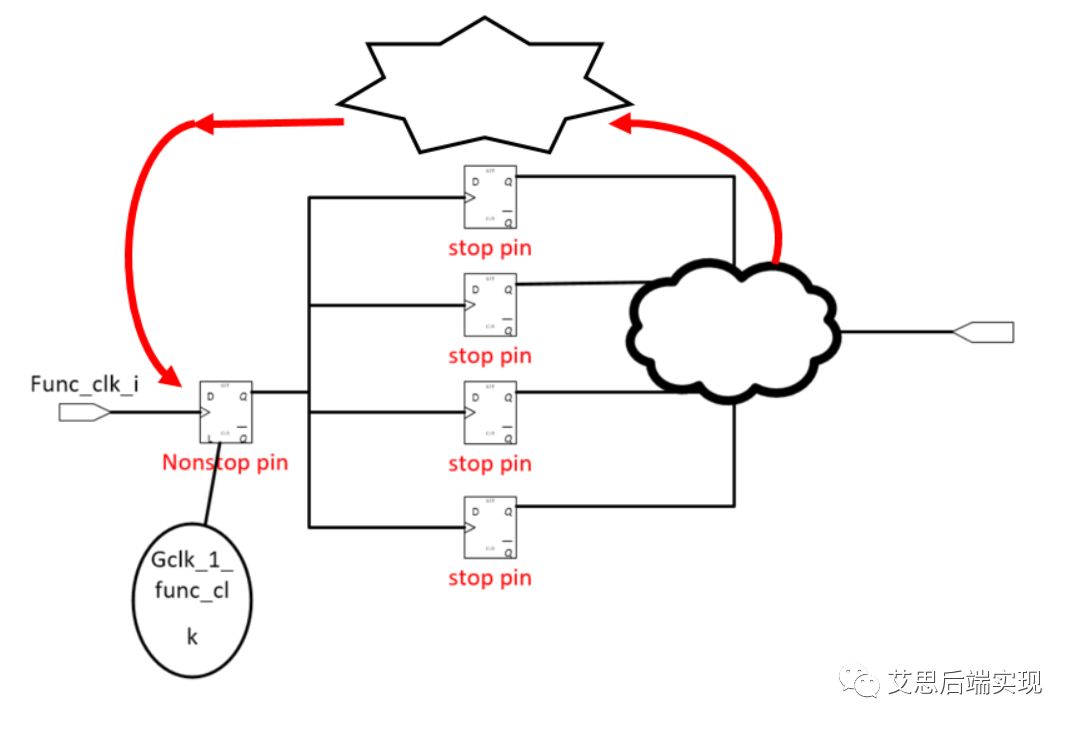

工具會balance 后面四個(gè)被gating 驅(qū)動的FF(stop pin)之間的skew,但是CG是它們的clock 的driver,不難想象,CG EN的latency(T_latch)一定小于CG fanout FF的clock latency(T_FF),這是一個(gè)永遠(yuǎn)不能改變的事實(shí)。在某些情況下會帶來CG setup violaoiton,如下圖:

如果有一條正面這樣的data path存在,那么launch clk (FF) 一定是晚于capture clk (CG),在高頻和復(fù)雜datapath的情況下,這樣的timing是很難修復(fù)的

所以要在CTS之前解決或者簡化這個(gè)問題,

解決這個(gè)問題的關(guān)鍵就是,讓CG clock latency(T_latch)和fanout FF clk latency(T_FF) 盡可能的足夠小。

要讓前后兩級的clock latency的差值足夠小,其中有一個(gè)方法就是讓他們的擺放足夠近,在綜合結(jié)束后,通過report_clock_gating的report可以看到所有CG和他的fanout的列表,這個(gè)時(shí)候,我們通過第一版的CTS結(jié)果,可以評估出那些FF-CG的timing是有困難的,這些FF以及他們的CG使用relative placement的方法,讓工具在place 的階段就把他們擺放的足夠近,從而在物理距離上來解決這個(gè)CG 的setup 問題。

審核編輯:劉清

-

控制器

+關(guān)注

關(guān)注

112文章

16382瀏覽量

178322 -

寄存器

+關(guān)注

關(guān)注

31文章

5355瀏覽量

120517 -

RTL

+關(guān)注

關(guān)注

1文章

385瀏覽量

59831 -

UPF

+關(guān)注

關(guān)注

0文章

50瀏覽量

13529 -

dff

+關(guān)注

關(guān)注

0文章

26瀏覽量

3422

原文標(biāo)題:Clock Gating之淺見

文章出處:【微信號:處芯積律,微信公眾號:處芯積律】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

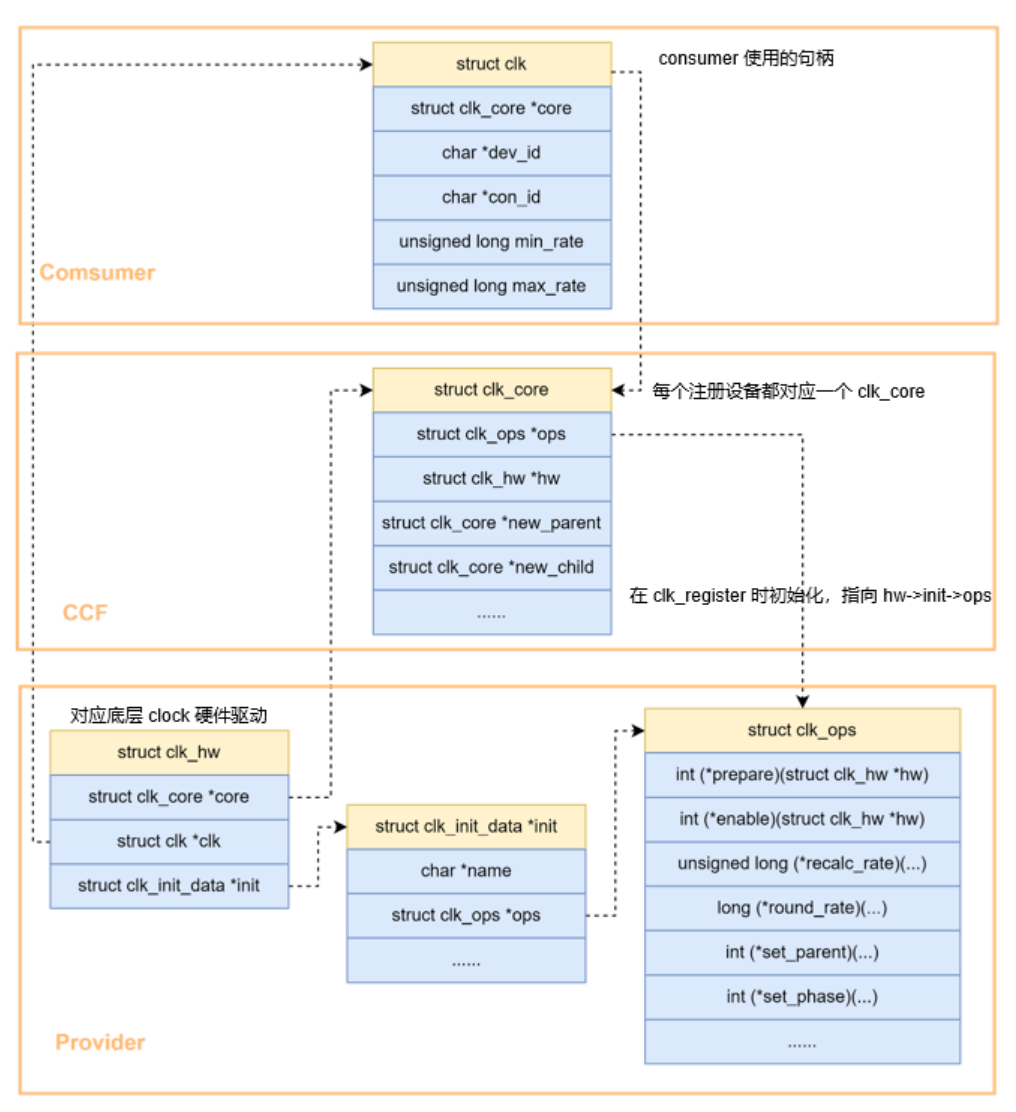

Linux clock子系統(tǒng)及驅(qū)動實(shí)例

clock-gating的綜合實(shí)現(xiàn)

淺析clock gating模塊電路結(jié)構(gòu)

什么是In-cell及On-cell

in-cell panel_In-Cell觸摸屏原理

分析clock tree的小工具——CCOPT Clock Tree Debugger(一)

低功耗設(shè)計(jì)之multi-bit cell技術(shù)簡介

ASIC的clock gating在FPGA里面實(shí)現(xiàn)是什么結(jié)果呢?

時(shí)鐘子系統(tǒng)中clock驅(qū)動實(shí)例

RTL實(shí)例化的clock gating cell淺見

RTL實(shí)例化的clock gating cell淺見

評論