在集成電路領域中,深寬比被定義為刻蝕深度與刻蝕圖形CD(Criticlal Dimension)的比值。CD是IC制造中的一個重要指標,通常與刻蝕的特征圖形的尺寸相關聯,包括有淺槽隔離的間隙、晶體管的溝道長度、金屬互聯線的寬度等。隨著高密度集成電路特征尺寸的不斷減小,對于高深寬比的間隙進行均勻、無空洞,填充淀積工藝顯得至關重要。

以3D NAND為例,其復雜結構需要高的深寬比鍍膜工藝,例如疊層沉積、高深寬比通道/通孔沉積和臺階沉積等等。這類非平面結構對沉積工藝的要求很高,常見的物理氣相沉積(PVD)/化學氣相沉積(CVD)的成核生長機制已經難以滿足。

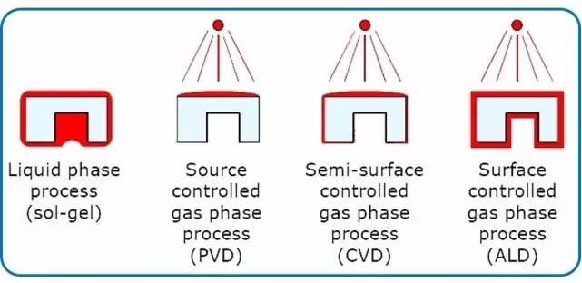

ALD與其他制膜技術對比(圖片來源網絡)

不同于傳統的沉積方式,原子層沉積(ALD)的反應機制是逐層飽和反應,這種表面反應具有自限性,通過累積重復這種自限性可以制備所需精確厚度的膜層,并且具有良好的臺階覆蓋率及厚度均勻性,連續生長可以獲得致密性高的納米薄膜。

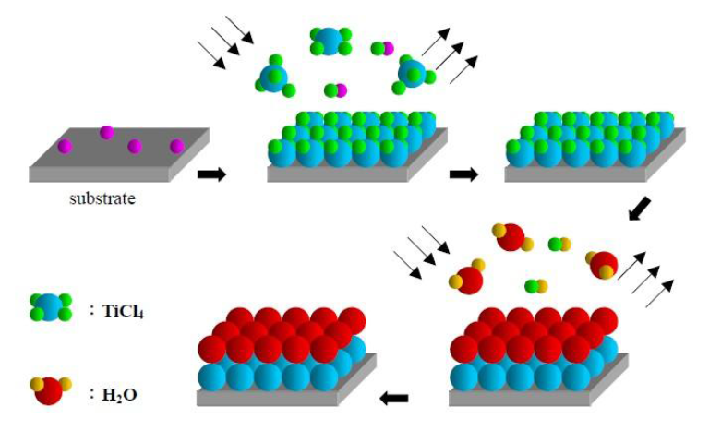

使用TiCl4和H2O制備的TiO2(圖片來源網絡)

基于表面飽和化學性吸附及自我限制的反應機制,原子層沉積(ALD)擁有下列優點:

通過對生長循環數的控制,可以精確控制目標膜厚

通過對前驅體流量的穩定性/均勻性控制,可獲得較高致密性的薄膜

對于具有高深寬比結構的器件/材料,ALD具備良好的側壁覆蓋能力和階梯覆蓋能力,沉積保形性較好

結合原磊技術團隊成員多年的經驗積累,并經過不斷的優化和實踐,原磊將ALD在深寬比器件制造的理論優勢,用自己的技術和產品充分展現出來。原磊第二代研發型ALD設備Elegant-Y/A系類產品,在不改變腔體的前提下滿足O3/Plasma/Thermal三種工藝的任意切換。針對高深寬比結構的材料/器件,設計了獨有的FV-ALD工藝,給反應前驅體提供一個更加穩定的腔內氣流環境,針對高深寬比的結構,有效擴大了階梯覆蓋能力以及樣品表面膜層的均勻性,可以實現深寬比1:1000的溝道內Al2O3、HfO2和TiN的均勻致密沉積。

ELEGANT II-Y300

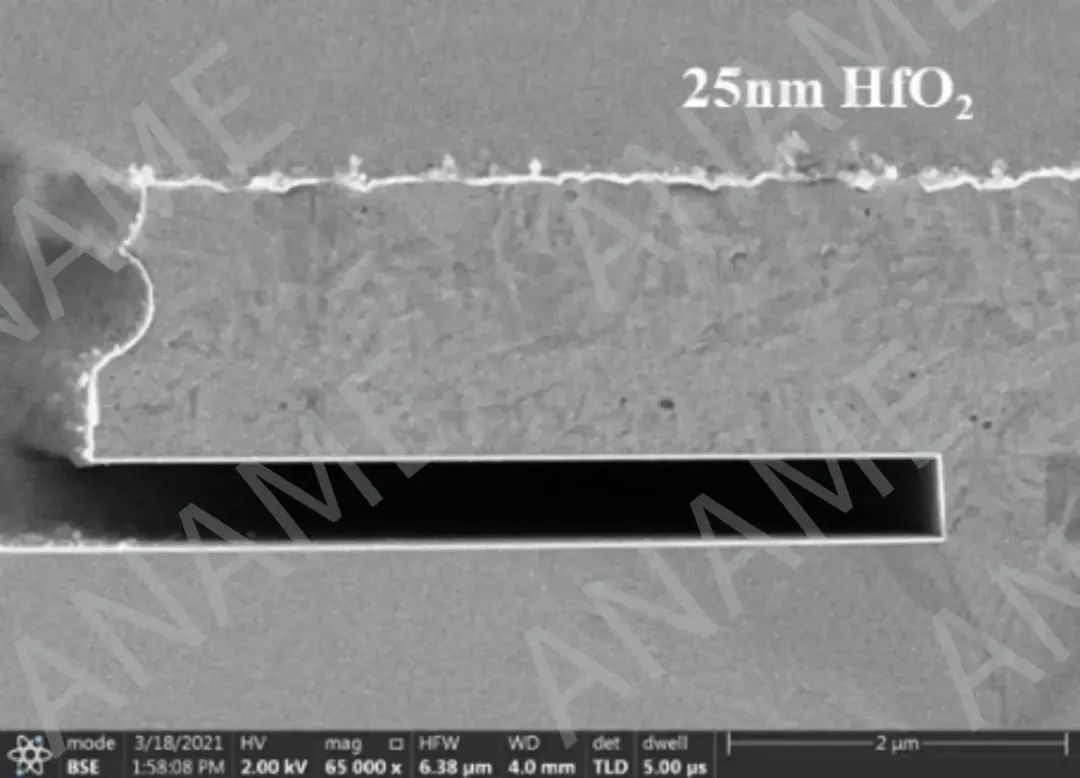

圖1展示了Elegant-Y300系列ALD產品在Floating型溝道結構內沉積25nm HfO2薄膜的SEM圖片。圖2中展示了放大倍數的HfO2薄膜,可清晰地看到其致密均勻的沉積效果。.

Figure 1:高深寬比為1:1000溝道結構25nm-HfO2薄膜的SEM結果

Figure 2:高深寬比為1:1000溝道結構25nm-HfO2薄膜厚度測試結果

經過前期大量的工藝驗證和研發,我司也摸索出一系列ALD制備氧化物、氮化物和金屬的成熟工藝,包括:

氧化物

Al2O3、TiO2、SiO2、HfO2、Ta2O5、ZrO2、ZnO、SnO2、La2O3

金屬

Fe、Ag、Co、Ni、Cu、Ru、Pt

氮化物

多元材料

TiN、TiC、GaN、AlN、HfON、LaAlO3、MnN、TaN、WN、Si3N4等

我司目前主要產品是研發和量產型原子層沉積(ALD)設備,其中GRACE MX系列和ELEGANT II-A系列機型均可成熟量產。

GRACE MX系列

原磊自主研發的第一代多層平板式原子層薄膜沉積(ALD)系統。支持全方位的工藝開發,且最大可容納樣品尺寸及層數可根據客戶需求量身定制。

成熟量產型機臺,可使用標準或自定義的 Cassette一次性裝載25片6/8寸英寸晶圓。在化合物半導體領域,我司利用ALD技術開發出獨特的處理工藝-即ISSET技術,能夠大幅提升功率器件的電學性能。

審核編輯:劉清

-

集成電路

+關注

關注

5388文章

11563瀏覽量

362091 -

晶體管

+關注

關注

77文章

9701瀏覽量

138383 -

PVD

+關注

關注

4文章

50瀏覽量

16998 -

CVD

+關注

關注

1文章

74瀏覽量

10745

原文標題:【求是緣技術沙龍】ALD在高深寬比器件制造上不可替代的應用

文章出處:【微信號:TruthSemiGroup,微信公眾號:求是緣半導體聯盟】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

【「大話芯片制造」閱讀體驗】+ 芯片制造過程和生產工藝

白皮書導讀 | 電機驅動系統中的寬禁帶開關器件

用平面錐制造100μm深10μm寬的高縱橫比硅通孔

拓荊科技:超高深寬比溝槽填充CVD產品首臺已通過客戶驗證

在Keystone II器件上使用Arm ROM引導加載程序

功率半導體器件測試解決方案

ALD在高深寬比器件制造上不可替代的應用

ALD在高深寬比器件制造上不可替代的應用

評論