DC-DC-25---DC-DC的Layout要點

引言:DC-DC的布局布線少不了要使用過孔和銅皮,過孔和銅皮的相關寄生參數對于功率布局走線需要格外注意,本節簡述過孔銅箔的相關參數估算以及使用注意點。

1.銅箔的阻抗

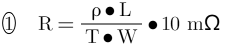

圖25-1表示單位面積銅箔的阻抗值。通常為厚35um、寬1mm、長1mm銅箔面積的阻抗值。通常可利用下列公式進行阻抗計算:

l ∶ 導線的長度 [mm]

w ∶ 導線的寬度 [mm]

t ∶ 銅箔的厚度 [um]

p ∶ 銅的電阻率 [uΩcm]

T ∶ 溫度

根據從圖25-1讀取到的每單位面積的阻抗值RP來計算,結果如下:

RP ∶ 從曲線中讀取的阻抗值 [mΩ]

l ∶ 導線的長度 [mm]

w ∶ 導線的寬度 [mm]

t ∶ 銅箔的厚度 [um]

比如25°C時,寬3mm、長50mm的銅箔的阻抗值,可以根據下列計算得出是8.17mΩ。

根據該阻抗值,流過3A電流時的壓降為24.5mV,當溫度上升至100℃時,阻抗值增加29%,壓降也增加至31.6mV。

圖25-1:單位面積銅箔的阻抗值

2.銅箔的感抗

銅箔的感抗可以用以下公式表示。從公式可以看出,PCB布線的感抗值幾乎不依賴于銅箔的厚度。

l ∶ 導線的長度 [mm]

w ∶ 導線的寬度 [mm]

t ∶ 銅箔的厚度 [um]

圖25-2表示的是銅箔感抗的計算值。從圖表可以看出,即使線寬增加2倍,電感值也不會降低到理想狀態。想要抑制寄生電感的影響,縮短布線長度是最好的解決辦法。假設電感值L[H]在電路板布線上的流過的電流在時間t[s]之內的變化量為i[A],則將在其電路板布線的兩端產生以下電壓。

例如在寄生電感值為6nH的電路板布線上,在10ns內流過了2A的電流時,將產生以下電壓:

圖25-2:銅箔的感抗

3.過孔的阻抗

過孔的阻抗值用以下公式表示。圖25-3表示的是板厚1.6mm、鍍層厚0.015mm (15um) 條件下過孔的阻抗值。

h ∶ 板厚 [mm]

d ∶ 過孔直徑 [mm]

tm∶通孔鍍層厚度[mm]

p ∶銅的電阻率[uΩcm]

T ∶ 溫度

圖25-3:過孔的阻抗

4.過孔的感抗

根據Howard W. Johnson的方法,過孔的感抗值按以下公式表示。圖25-4顯示了計算結果。

h∶ 板厚[mm]

d ∶ 過孔直徑[mm]

感抗值雖然很小,但布線呈直角時會導致EMI惡化。

圖25-4:過孔的感抗

5.過孔的容許電流

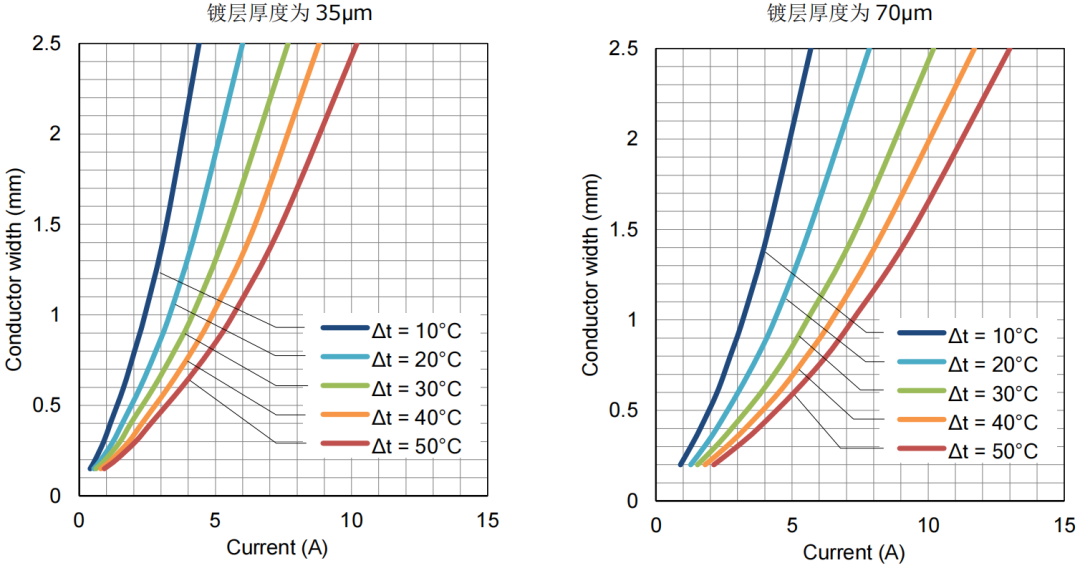

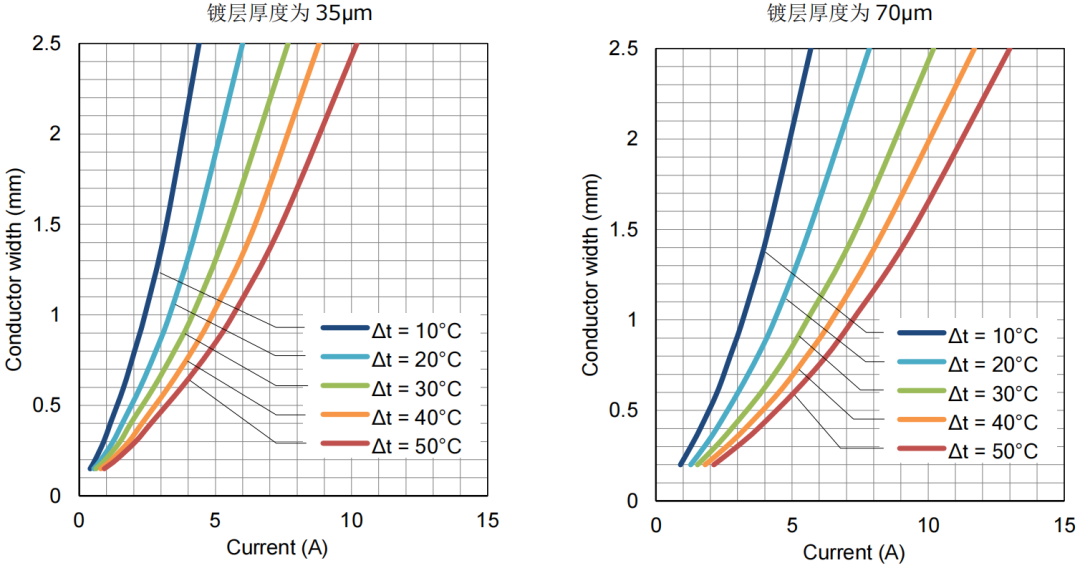

過孔的直徑乘以π后的值相當于線寬,可以根據圖25-5中導體的電流導致的溫度上升圖表推測出過孔的容許電流值,但是由于過孔的鍍層厚度只有18um,容許電流能力要低于圖表所示鍍層厚度為35um的導線。

圖25-5:鍍層厚度、導線寬度、電流導致的溫升

在前述布線項中,曾建議在鍍層厚度為35um時,按照1A電流使用1mm以上寬度的導體進行布線,但是因為過孔的鍍層厚度只有一半,所以建議按照1A電流使用2mm以上寬度的導體進行布線。圖25-6是容許電流的示例,請根據使用用途配置過孔的個數,確保容許電流、阻抗、感抗滿足規格要求。

圖25-6:容許電流

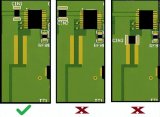

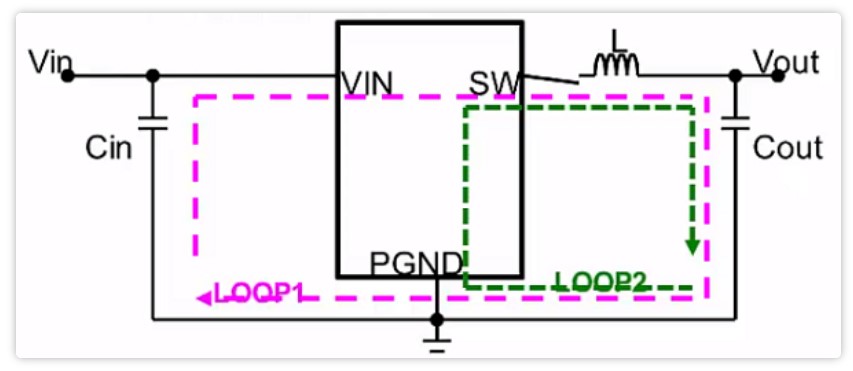

6. 拐角布線

如果將拐角布線折為直角,阻抗將在拐角處發生變化,這會導致電流波形紊亂,產生被稱為“反射”的波形畸變。開關節點等頻率較高的布線EMI可能會惡化。如圖25-7所示,盡量將拐角處做45°折線或者圓弧彎曲狀處理,彎曲的半徑越大,阻抗的變化越小。

圖25-7:拐角布線

-

DC-DC

+關注

關注

30文章

2192瀏覽量

83551 -

Layout

+關注

關注

15文章

413瀏覽量

63135 -

布局布線

+關注

關注

1文章

89瀏覽量

15354

發布評論請先 登錄

DC-DC的Layout要點(2)

DC-DC工作原理

DC-DC的layout有哪些原則

推薦一個DC-DC電路設計工具

DC-DC PCB layout 指導

DC-DC PCB layout指導說明

DC-DC的PCB設計

DC-DC轉換器PCB設計的一些要點

DC-DC電源PCB設計要點

如何設計好DC-DC電源,以下幾點值得注意

5條DC-DC PCB layout建議

DC-DC的PCB設計注意的點

評論