一引言

電磁干擾的主要方式是傳導(dǎo)干擾、輻射干擾、共阻抗耦合、感應(yīng)耦合。對這幾種途徑產(chǎn)生的干擾我們應(yīng)采用的相應(yīng)對策:傳導(dǎo)干擾采取濾波,輻射干擾采用屏蔽和接地等措施就能夠大大提高產(chǎn)品的抵抗電磁干擾的能力,也可以有效的降低對外界的電磁干擾。本文從濾波設(shè)計、接地設(shè)計、屏蔽設(shè)計三個角度,介紹EMC的設(shè)計技巧。

二濾波

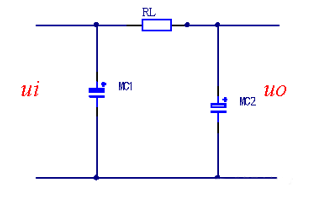

濾波是信號處理里面比較重要的一個環(huán)節(jié),通常減少直流當(dāng)中的交流成分并獲得比較平滑的直流電,在整流之后都要經(jīng)過濾波電路,濾波常用的元器件是電容、電阻以及電感,下面介紹濾波電路常用的五種電路形式。

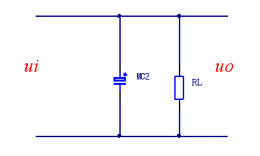

圖1: 電容濾波

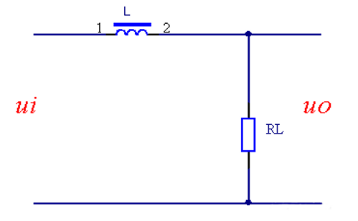

圖2:電感濾波

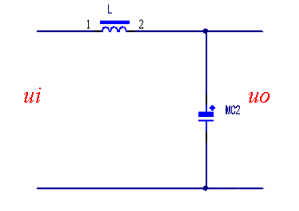

圖3:LC濾波

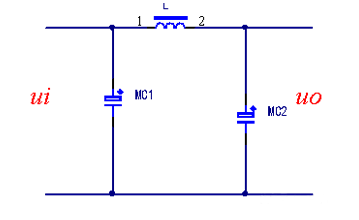

圖4:LC-π濾波

圖5:RC-π濾波

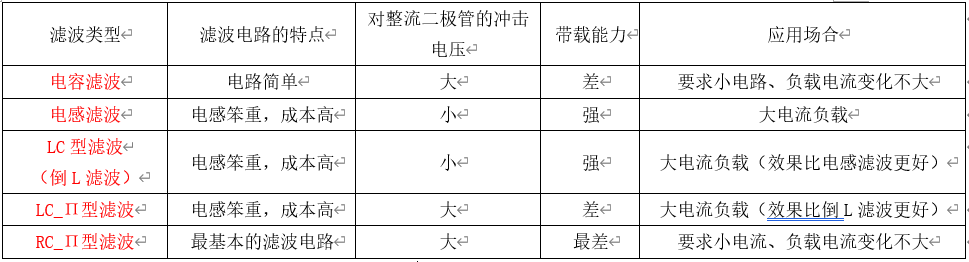

以上的五種濾波的特點如下:

圖6 濾波器的特點

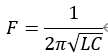

因為根據(jù)公式電容的諧振公式:

可知,當(dāng)我們的電容的ESL偏大時電容的諧振頻率會偏小,反之。我們通過使用同樣的封裝、同樣的容值。在1GHz的頻率下,普通的MLCC電容一般的ESL大于1nF,而我司的BDL濾波器的ESL為55pH,如圖6可以對比MLCC和我司的BDL的插入損耗曲線圖,由圖6可以看出我司的BDL濾波器比MLCC對于噪聲的衰減能力比較好。

圖 7插入損耗曲線圖

我司的BDL濾波器應(yīng)用:電機、DC-DC、功放、信號線的差分對。

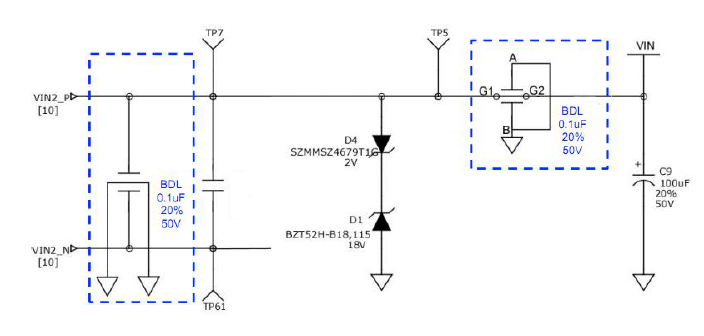

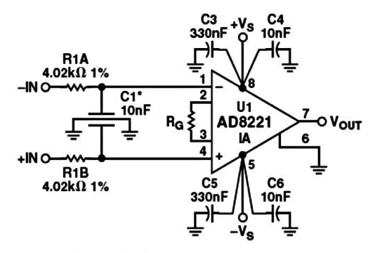

圖 8BDL電機應(yīng)用板

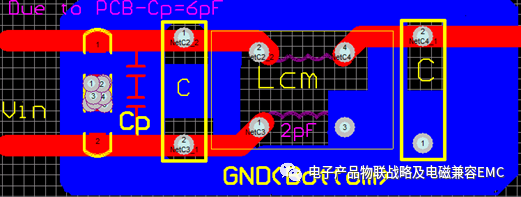

圖 9BDL應(yīng)用于DC-DC

圖 10BDL應(yīng)用于功放

三接地

接地是最有效的抑制騷擾源的方法,可解決50%的EMC問題。系統(tǒng)基準(zhǔn)地與大地相連,可抑制電磁騷擾。外殼金屬件直接接大地,還可以提供靜電電荷的泄漏通路,防止靜電積累。

在地線設(shè)計中應(yīng)注意以下幾點:

(1)正確選擇單點接地與多點接地

在低頻電路中,信號的工作頻率小于1MHz,它的布線和器件間的電感影響較小,而接地電路形成的環(huán)流對干擾影響較大,因而應(yīng)采用單點接地。當(dāng)信號工作頻率大于10MHz時,地線阻抗變得很大,此時應(yīng)盡量降低地線阻抗,應(yīng)采用就近多點接地。當(dāng)工作頻率在1~10MHz時,如果采用一點接地,其地線長度不應(yīng)超過波長的1/20,否則應(yīng)采用多點接地法。

電路板上既有高速邏輯電路,又有線性電路,應(yīng)使它們盡量分開,而兩者的地線不要相混,分別與電源端地線相連。要盡量加大線性電路的接地面積。

(3)盡量加粗接地線

若接地線很細,接地電位則隨電流的變化而變化,致使電子設(shè)備的定時信號電平不穩(wěn),抗噪聲性能變壞。因此應(yīng)將接地線盡量加粗,使它能通過三位于印制電路板的允許電流。如有可能,接地線的寬度應(yīng)大于3mm。

(4)將接地線構(gòu)成閉環(huán)路

設(shè)計只由數(shù)字電路組成的印制電路板的地線系統(tǒng)時,將接地線做成閉環(huán)路可以明顯的提高抗噪聲能力。其原因在于:印制電路板上有很多集成電路組件,尤其遇有耗電多的組件時,因受接地線粗細的限制,會在地結(jié)上產(chǎn)生較大的電位差,引起抗噪聲能力下降,若將接地結(jié)構(gòu)成環(huán)路,則會縮小電位差值,提高電子設(shè)備的抗噪聲能力。

四屏蔽

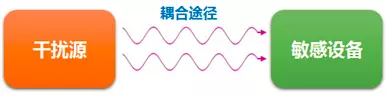

圖11 EMC三要素

根據(jù)我們的EMC三要素來講,我們的屏蔽分為兩類來說明,一類是針對干擾源進行屏蔽,另一類為在耦合路徑上進行屏蔽。而屏蔽干擾源是對一些輻射比較嚴重的IC進行屏蔽,防止干擾源通過空間輻射影響到一些敏感設(shè)備。在耦合路徑進行屏蔽處理是防止噪聲通過線束將噪聲放大,注意我們所做的一切屏蔽都要進行接地處理,盡量多點接地。下面給大家介紹一下屏蔽的類型:

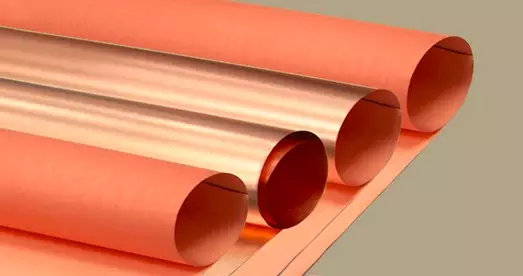

(1)改良電子設(shè)備中的電路設(shè)計,采用濾波器件、不同特性元器件分開布局(局部增加屏蔽罩、粘貼金屬箔、也有采用金屬編織網(wǎng)等方法);

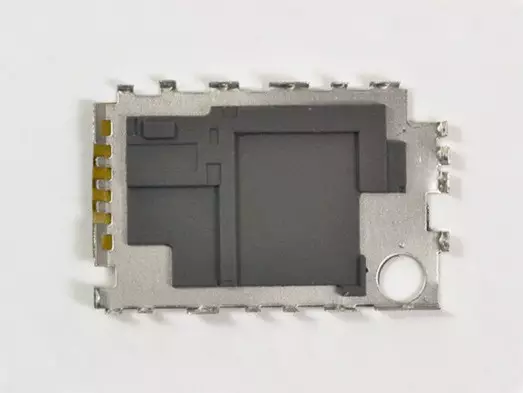

圖12 金屬屏蔽罩

圖13 銅箔屏蔽

圖14 金屬箔屏蔽帶

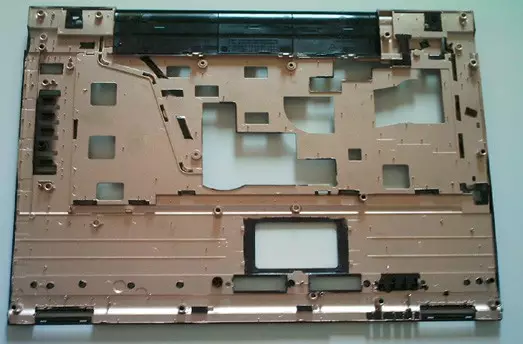

(2)在整個電子設(shè)備外殼就具有高電磁波發(fā)射能力的電路和器件周圍,添加電磁波屏蔽罩、粘貼金屬箔、噴涂導(dǎo)電涂料、鍍一層導(dǎo)電金屬層、增加電磁波吸收材料。

圖15電磁屏蔽氈(屏蔽芯片)_黑色部分

圖16電磁屏蔽氈

圖17電鍍導(dǎo)電屏蔽層

圖18噴涂電磁屏蔽涂料

五總結(jié)

本文總結(jié)了EMC整改中的一些常用的措施,屏蔽、濾波和接地是最基礎(chǔ)的措施,也是最常用的,希望能給大家?guī)韼椭?/p>

-

濾波電路

+關(guān)注

關(guān)注

47文章

651瀏覽量

70654 -

接地

+關(guān)注

關(guān)注

7文章

827瀏覽量

46744 -

emc

+關(guān)注

關(guān)注

172文章

4179瀏覽量

187157

原文標(biāo)題:濾波、接地、屏蔽、三個視角看EMC設(shè)計

文章出處:【微信號:EMC電磁兼容,微信公眾號:EMC電磁兼容】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

濾波、接地、屏蔽、三個視角看EMC設(shè)計

從濾波設(shè)計、接地設(shè)計、屏蔽設(shè)計和PCB布局布線介紹EMC的設(shè)計技巧

EMC三個重要規(guī)律

接地與EMC的分析設(shè)計

大神總結(jié):4個角度看EMC設(shè)計技巧!

EMC濾波 、接地、屏蔽和PCB布局設(shè)計技巧資料下載

EMC濾波設(shè)計技巧 EMC接地和屏蔽設(shè)計

EMC領(lǐng)域的三個重要規(guī)律 EMC問題的三個要素

四大視角看EMC設(shè)計:濾波、接地、屏蔽、PCB布局

直播預(yù)告 I 講EMC說接地

硬核干貨 - 講EMC說接地

評論