在過去幾年中,具有高清晰度視頻顯示器的一些產(chǎn)品大幅度增加。高清晰度視頻顯示器被集成在這些產(chǎn)品的內(nèi)部,或者放在產(chǎn)品的外面。原始設(shè)備制造商正在期望能夠利用標(biāo)準(zhǔn)的平板顯示器及接口技術(shù)來降低產(chǎn)品的成本,并提供長期的解決方案。設(shè)計(jì)界面對(duì)著這種挑戰(zhàn),并繼續(xù)實(shí)施低成本平板顯示器驅(qū)動(dòng)器,在接口的后端中提供專用化和增值的功能。

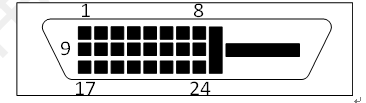

在消費(fèi)市場上,平板顯示技術(shù)的增長有助于統(tǒng)一接口選擇和降低成本。盡管高清晰度顯示器使用了模擬分量視頻接口(YCrCb),數(shù)字技術(shù),諸如數(shù)字視頻接口(DVI)和高清晰度多媒體接口(HDMI)已經(jīng)取代了大多數(shù)模擬接口。庭影院市場爆炸式的增長需要更新DVI標(biāo)準(zhǔn)。然而,需要一個(gè)龐大連接器的DVI接口限制了對(duì)數(shù)字版權(quán)管理(DRM)的支持,且缺少對(duì)單聲道或多聲道音頻的支持。為滿足演變的HDMI標(biāo)準(zhǔn)要求,它使用相同的如DVI這樣的基本信號(hào)傳輸,支持較小的連接器,以及更大帶寬(1080p分辨率)、DRM和8個(gè)通道的多格式音頻。

基于在平板領(lǐng)域中占主導(dǎo)地位的DVI和HDMI協(xié)議,原始設(shè)備制造商正在越來越多地追求他們自己的集成一種或兩種技術(shù)的產(chǎn)品開發(fā)。

DVI 和 HDMI標(biāo)準(zhǔn)

HDMI規(guī)范可以傳輸和接收未壓縮的數(shù)字流的音頻/視頻標(biāo)準(zhǔn)。它可以將視頻和多聲道音頻組合至單一的數(shù)字連接,節(jié)省了多條線路連接及相關(guān)成本。對(duì)于沒有音頻要求的1080i分辨率顯示,HDMI信號(hào)傳輸與DVI是向下兼容的。

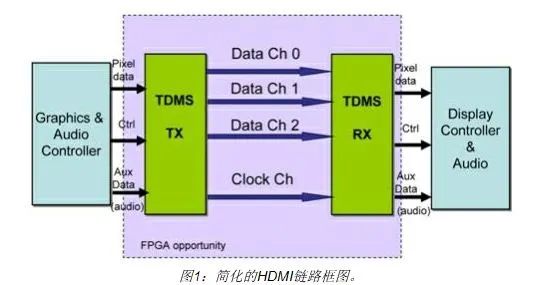

DVI和HDMI是基于稱為化傳輸差分信號(hào)(TMDS)的信號(hào)傳輸技術(shù) . TMDS也有類似CML的物理信號(hào)傳輸電平(電流模式邏輯)。圖1給出了簡化的HDMI鏈路框圖。

HDMI接口是一種帶有三個(gè)TMDS通道的屏蔽電纜。默認(rèn)配置是RGB ,每個(gè)通道傳送一種顏色。與DVI不同, HDMI支持亮度及色度的分量(YCbCr 44和42),并通過3個(gè)T M D S鏈路,支持多達(dá)8個(gè)音頻通道。分開的對(duì)線以1/10X TMDS比特率傳送一個(gè)同步時(shí)鐘,另外的線提供了一個(gè)低速的顯示特性,支持從顯示器到源端的通信(EDID)。另外,HDMI還集成了輔助控制功能,如熱插拔檢測和針對(duì)EDID接口的電源和地。HDMI共有29個(gè)連接。接收器恢復(fù)信號(hào)的功能限制了電纜的長度。

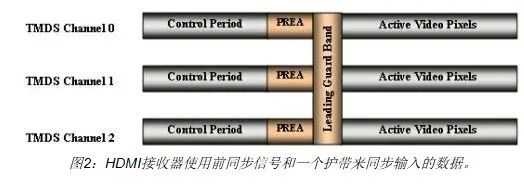

HDMI鏈路有三種工作周期:視頻數(shù)據(jù)周期、數(shù)據(jù)隔離周期和控制周期。它在視頻數(shù)據(jù)周期傳送有效的視頻,在數(shù)據(jù)隔離周期傳輸音頻和輔助數(shù)據(jù),傳輸時(shí)使用了一系列的數(shù)據(jù)包。在任何視頻或數(shù)據(jù)周期之間,需要有控制周期。每個(gè)視頻數(shù)據(jù)周期開始時(shí),有一個(gè)緊隨護(hù)帶的前同步信號(hào),針對(duì)從控制周期到視頻周期的過渡,提供了非常穩(wěn)定的指示。前同步是8個(gè)連續(xù)的預(yù)定義字符(10'b1101010100 , 10'b0010101011 , 10'b0101010100 ,和10'b1010101011),護(hù)帶是針對(duì)每個(gè)通道的2個(gè)連續(xù)的獨(dú)特字符(通道1 : 10b1011001100 ;通道2 : 10b0100110011 ;通道3 : 10b1011001100)。

使用DVI/HDMI實(shí)現(xiàn)系統(tǒng)

DVI和HDMI的發(fā)送和接收接口通常用ASSP來實(shí)現(xiàn)。本文提出了一種采用FPGA的替代解決方案。采用FPGA實(shí)現(xiàn)DVI/HDMI接口具有以下優(yōu)點(diǎn):

(1)FPGA技術(shù)使得設(shè)計(jì)人員可以將ASSP串行/解串器(SERDES)與后端定制的特殊設(shè)計(jì)功能集成在一起,以節(jié)省電路板面積。

(2)通過盡可能少地使用元器件、降低成本和功耗來增加設(shè)計(jì)的可靠性。

(3)讓設(shè)計(jì)者利用的技術(shù),受益于先進(jìn)的工藝技術(shù)。該標(biāo)準(zhǔn)在1999年批準(zhǔn)后不久,開發(fā)了大量的離散DVI接口器件。由于這種制造技術(shù)是成熟的(主要是0.18微米),因此更加昂貴。

(4) FPGA擁有寬的溫度選擇范圍,具有針對(duì)工業(yè)和汽車的產(chǎn)品,而大多數(shù)離散的DVI和HDMI接口器件是專為消費(fèi)市場而設(shè)計(jì),往往只能在商業(yè)溫度范圍內(nèi)工作。因此,對(duì)于在工業(yè)和汽車應(yīng)用方面的嵌入式設(shè)計(jì),這可能會(huì)是一個(gè)問題。

(5)FPGA設(shè)計(jì)是可移植的,使人們關(guān)注的產(chǎn)品使用壽命得到限度延長。大多數(shù)DVI器件是針對(duì)基于PC的應(yīng)用,通常這些接口適合進(jìn)一步集成至其他的ASSP.這種情況發(fā)生時(shí),這些分立器件或許不再可用,因?yàn)橹圃焐炭赡苤辉敢鉃閭€(gè)人電腦市場提供服務(wù)。

所有這些因素使得FPGA解決方案更具有吸引力,而且這也是前沿的技術(shù)。FPGA已被證明是一種有效的解決方案,它能夠集成多種功能、縮短產(chǎn)品的上市時(shí)間并降低總的成本。此外,F(xiàn)PGA通常有很寬的溫度范圍,并有很長的產(chǎn)品生命周期。

針對(duì)ECP2M和ECP3器件系列,萊迪思(Lattice)半導(dǎo)體公司近推出了DVI/HDMI接口的參考設(shè)計(jì)。萊迪思半導(dǎo)體公司的ECP2M和ECP3系列是集成了SERDES的低功耗、低成本FPGA,擁有很寬的溫度范圍。這些器件具有高達(dá)16個(gè)通道的SERDES,可處理250Mbps~3.125Gbs的數(shù)據(jù)速率,且無過采樣情況。DVI/HDMI是ECP2M和ECP3系列支持的模式之一,能夠?qū)崿F(xiàn)這個(gè)設(shè)計(jì)是因?yàn)槿R迪思已對(duì)T M D S信號(hào)傳輸構(gòu)建了一個(gè)獨(dú)特的接口。在DVI/HDMI電纜中, T M D S信號(hào)是有一個(gè)外部時(shí)鐘的源同步信號(hào)。萊迪思已開發(fā)出一種技術(shù),利用ECP2M或ECP3中內(nèi)置的SERDES恢復(fù)并產(chǎn)生針對(duì)T M D S的合適的數(shù)據(jù)和格式。這種實(shí)現(xiàn)是可能的,因?yàn)閮?nèi)置的SERDES有250Mb/s到3.2Gbp/s的寬動(dòng)態(tài)范圍。

萊迪思的DVI/HDMI參考設(shè)計(jì)集成了發(fā)送和接收功能,使得用單芯片解決方案能夠?qū)崿F(xiàn)一些有趣的應(yīng)用程序。例如,可以針對(duì)設(shè)計(jì)使用傳輸方向,從原來的7:1 LVDS顯示驅(qū)動(dòng)器轉(zhuǎn)換至DVI.在接收端,用接收到的HDMI數(shù)據(jù)實(shí)現(xiàn)一個(gè)HDMI擴(kuò)展器,然后將它格式化并通過另一種接口(如光纖或CAT5)送出。另一種應(yīng)用是HD-SDI到DVI的轉(zhuǎn)換,或反之亦然。針對(duì)圖形疊加、畫中畫和分屏應(yīng)用,HDCP協(xié)議的許可證可以進(jìn)一步處理和管理音頻和視頻數(shù)據(jù)流。

基于ECP2M的接收功能實(shí)現(xiàn)

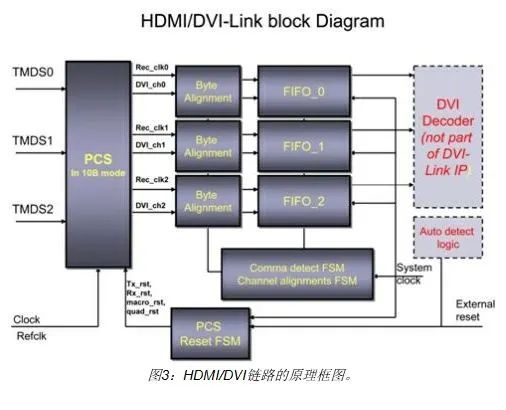

DVI/HDMI參考設(shè)計(jì)有發(fā)送和接收功能。在接收端,ECP2M利用內(nèi)置模塊SERDES恢復(fù)T M D S信號(hào),通過SERDES內(nèi)的時(shí)鐘和數(shù)據(jù)恢復(fù)(CDR)電路完成這個(gè)處理。CDR電路將每個(gè)串行的T M D S通道轉(zhuǎn)換至10位,并將具有同步時(shí)鐘的數(shù)據(jù)傳送至FPGA接口,然后在FPGA中進(jìn)行數(shù)據(jù)處理達(dá)到同步。這要求有三個(gè)級(jí)別的同步,分別是在本文中稱為“字節(jié)對(duì)齊”的10位同步、通道調(diào)整、多通道對(duì)齊。文章的后面討論這些步驟。接下來是自動(dòng)檢測正在運(yùn)行的數(shù)據(jù)流的分辨率(480p、720p、1080p或1080i),并調(diào)整物理編碼子層(PCS)參數(shù)。當(dāng)在這些分辨率之間動(dòng)態(tài)切換時(shí),應(yīng)保證優(yōu)化運(yùn)行。針對(duì)發(fā)送端,沒有必要進(jìn)行字節(jié)和通道對(duì)齊。10位模式的PCS是用來使數(shù)據(jù)串行化,并與液晶顯示屏通信。

ECP2M/ECP3的CML SERDES輸入(見圖3的接收信號(hào)流)收到T M D S三個(gè)通道的信號(hào)(0、1,和2)數(shù)據(jù)。由于DVI/HDMI的信號(hào)不采用標(biāo)準(zhǔn)的8B/10B編碼,SERDES后面的PCS設(shè)置成10位模式(旁路)。T M D S信號(hào)傳輸使用對(duì)本協(xié)議的四個(gè)對(duì)齊的字符(不同于8B/10B方式)。串行器與SERDES的CDR傳遞10位的原始數(shù)據(jù),F(xiàn)PGA進(jìn)行字節(jié)對(duì)齊。DVI/HDMI鏈路連接能以多個(gè)不同的頻率發(fā)送數(shù)據(jù),自動(dòng)檢測邏輯被用來檢測正在傳送的是哪種分辨率,并配置PCS以便在SERDES鎖相環(huán)中實(shí)現(xiàn)鎖定。

接收同步

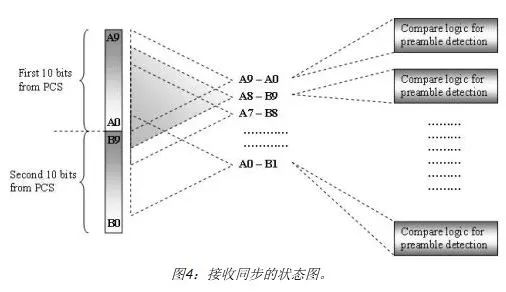

一旦10位數(shù)據(jù)在FGPA中,執(zhí)行上述定義的三個(gè)步驟(字節(jié)對(duì)齊、通道對(duì)齊、多通道對(duì)齊)是必須的 .字節(jié)對(duì)齊:設(shè)計(jì)確定在數(shù)據(jù)流的哪里是10位數(shù)據(jù)字節(jié)的開始和結(jié)束。在FPGA結(jié)構(gòu)中使用有限狀態(tài)機(jī)(FSM)來完成這一任務(wù)。把數(shù)據(jù)流的個(gè)和第二個(gè)10位組合在一起,形成一個(gè)20位的總線;然后分解至9位、10位總線。在這一階段,數(shù)據(jù)與對(duì)齊的字符進(jìn)行比較,當(dāng)字符順序發(fā)生了8次(稱為單通道對(duì)齊),同步信號(hào)有效。狀態(tài)圖如圖4所示。

同步檢測之后,對(duì)齊數(shù)據(jù)的字節(jié)寫入FIFO.當(dāng)所有三個(gè)通道都完成了“通道對(duì)齊”,就可以寫入FIFO,至此通道對(duì)齊的任務(wù)就結(jié)束了。在這一階段, FPGA將等待直到FIFO處于半滿狀態(tài),并在同一時(shí)間(多通道對(duì)齊)對(duì)三個(gè)FIFO進(jìn)行讀操作 .這將保證三個(gè)通道對(duì)齊,并同步。

基于ECP2M的發(fā)送功能實(shí)現(xiàn)

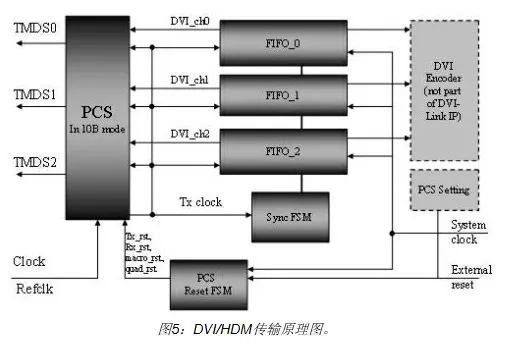

ECP2M傳送鎖相環(huán)有的操作范圍,預(yù)定義的范圍為:Low、MedLow、 Med、MedHigh 和 High.通過SCI總線,所有這些范圍在ECP2M中都是動(dòng)態(tài)配置的。因?yàn)橛懈鞣N各樣的顯示分辨率,針對(duì)理想的輸出率,DVI/HDMI參考設(shè)計(jì)必須有SERDES組。例如,如果要求一個(gè)720p的HDMI顯示,即742.5Mbps,SERDES PCS必須設(shè)置在適當(dāng)?shù)姆秶∕edLow)。顯示的數(shù)據(jù)是放置在一個(gè)由DVI/HDMI參考設(shè)計(jì)定義的FIFO中。同步從三個(gè)T M D S的每個(gè)通道中讀取數(shù)據(jù),然后將FIFO的數(shù)據(jù)移至PCS,再用SERDES進(jìn)行傳輸。PCS設(shè)置成10位模式,串行輸出FIFO的數(shù)據(jù)。在這一階段,采用合適的時(shí)鐘,數(shù)據(jù)將被轉(zhuǎn)換為新的T M D S 流,使接收器恢復(fù)信號(hào),如果配上顯示器,就會(huì)出現(xiàn)圖像。具體原理見圖5.

系統(tǒng)演示和驗(yàn)證

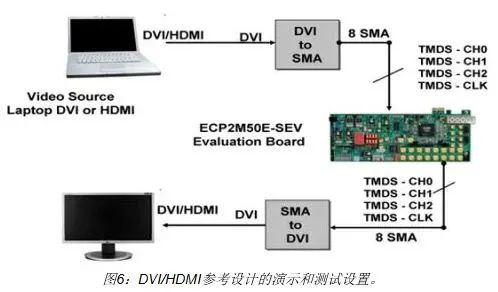

這個(gè)DVI/HDMI參考設(shè)計(jì)是經(jīng)過檢驗(yàn)和驗(yàn)證的,并遵守相關(guān)規(guī)范。萊迪思已經(jīng)實(shí)現(xiàn)了DVI環(huán)回演示,展示了設(shè)計(jì)的功能。可用ECP2M50E-SEV SERDES評(píng)估板和其它硬件來進(jìn)行演示,萊迪思半導(dǎo)體公司提供評(píng)估板和其他硬件。除了電路板之外,系統(tǒng)演示還需要DVI至SMA的接口卡、各種DVI和SMA電纜、一個(gè)DVI源和監(jiān)視器。整個(gè)演示和測試設(shè)置如圖6所示。

通過DVI至DVI或HDMI到DVI電纜,從筆記本電腦的接口得到DVI/HDMI數(shù)據(jù)流。DVI至SMA接口卡將轉(zhuǎn)換為DVI連接器至SMA,可通過SMA電纜與評(píng)估板相連接。一旦信號(hào)到達(dá)FPGA,將進(jìn)行處理并環(huán)回至TX SERDES通道。然后,通過SMA電纜傳輸數(shù)據(jù)送回到電路板上的SMA至DVI適配器,并終在顯示器上進(jìn)行比較。ECP2M集成了用來接收和發(fā)送三個(gè)DVI T M D S數(shù)據(jù)流的代碼。在FPGA內(nèi)完成字節(jié)對(duì)齊和同步邏輯,并將數(shù)據(jù)存入FIFO.在傳輸方向,ECP2M從FIFO中取得數(shù)據(jù),以10位的模式直接傳送至SERDES.該設(shè)計(jì)確保可在FIFO中三個(gè)DVI/HDMI通道完全對(duì)齊。

利用內(nèi)置的SERDES和可以從萊迪思半導(dǎo)體公司得到的參考設(shè)計(jì),ECP2M可以成功地實(shí)現(xiàn)接收和/或傳送DVI/HDMI接口功能。通過使用FPGA技術(shù)和參考設(shè)計(jì),設(shè)計(jì)人員能夠很快地實(shí)現(xiàn)設(shè)計(jì)的其余部分,并無縫地連接到一個(gè)DVI/ HDMI接口,以滿足他們自己的特殊要求。

有你想看的精彩 至芯科技-FPGA就業(yè)培訓(xùn)來襲!你的選擇開啟你的高薪之路!7月12號(hào)北京中心開課、歡迎咨詢! 解析高速ADC和DAC與FPGA的配合使用 FPGA芯片在編程器燒錄器里的應(yīng)用

掃碼加微信邀請(qǐng)您加入FPGA學(xué)習(xí)交流群

歡迎加入至芯科技FPGA微信學(xué)習(xí)交流群,這里有一群優(yōu)秀的FPGA工程師、學(xué)生、老師、這里FPGA技術(shù)交流學(xué)習(xí)氛圍濃厚、相互分享、相互幫助、叫上小伙伴一起加入吧!

點(diǎn)個(gè)在看你最好看

原文標(biāo)題:基于FPGA的DVI/HDMI接口實(shí)現(xiàn)方案

文章出處:【微信公眾號(hào):FPGA設(shè)計(jì)論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

-

FPGA

+關(guān)注

關(guān)注

1644文章

22009瀏覽量

616583

發(fā)布評(píng)論請(qǐng)先 登錄

方案拆解展示 | 納祥科技DP/mini dp/HDMI /DVI/TYPE-C 誘騙器方案

電腦顯示器接口哪個(gè)好?VGA、DVI、HDMI、DP接口對(duì)比PK

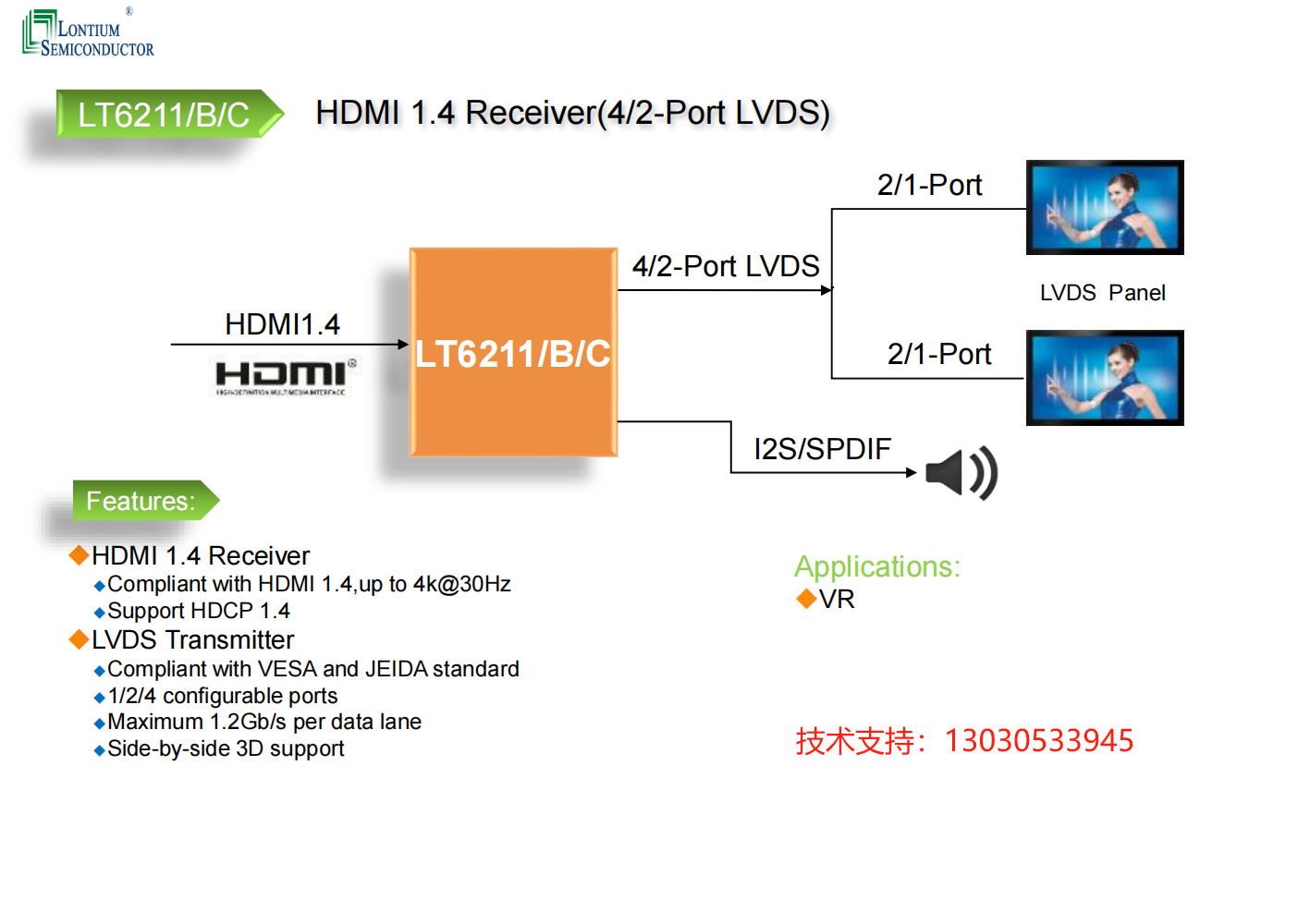

龍迅HDMI1.4轉(zhuǎn)LVDS方案

DVI在高清視頻傳輸中的優(yōu)勢 DVI接口的常見問題解決

DVI輸入和輸出設(shè)備比較 什么是DVI-D和DVI-I的區(qū)別

DVI接口的使用說明 DVI與HDMI的區(qū)別解析

HDMI接口轉(zhuǎn)換器的使用技巧

HDMI接口及規(guī)范介紹

DVI接口和HDMI接口有什么區(qū)別

DVI接口靜電保護(hù)方案

如何將LVDS/OLDI橋接到HDMI/DVI

FPGA無芯片HDMI接入方案及源碼

TMDS442 DVI/HDMI開關(guān)數(shù)據(jù)表

TMDS461 4合1 HDMI/DVI開關(guān)數(shù)據(jù)表

評(píng)論