“采樣保持電路是模數(shù)轉(zhuǎn)換器(ADC)中最重要的電路之一。其電路中存在的寄生電容會引入時鐘饋通、溝道電荷注入等非理想因素嚴重影響ADC的整體性能。鑒于此,本文將介紹這些非理想因素產(chǎn)生的原因及常見的解決方法”

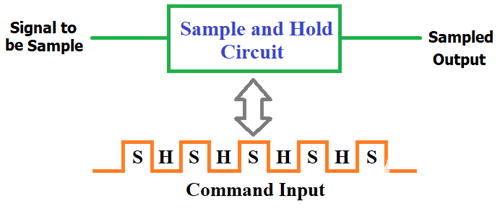

01采樣保持電路

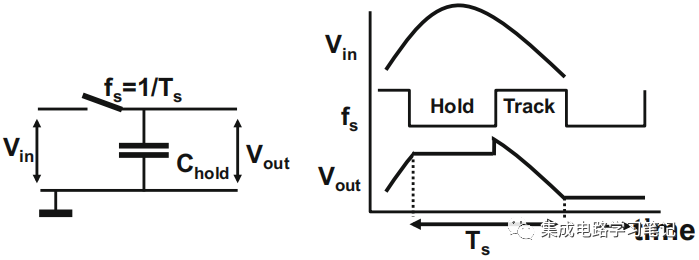

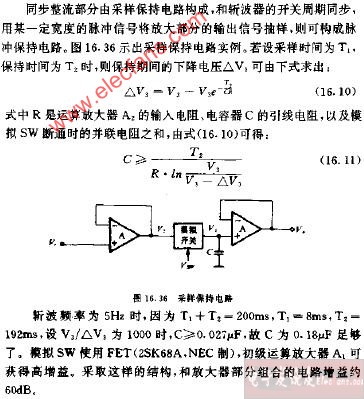

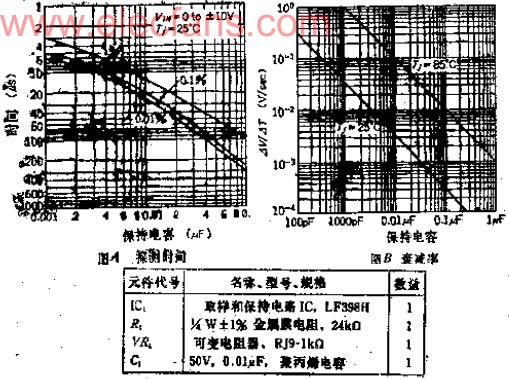

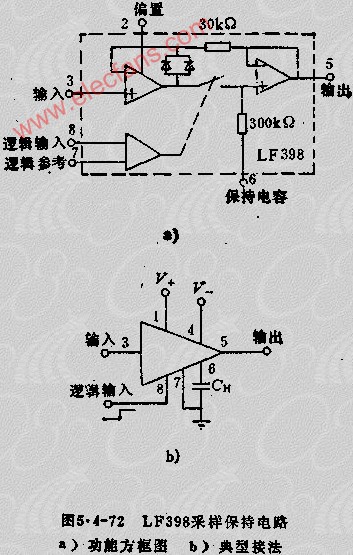

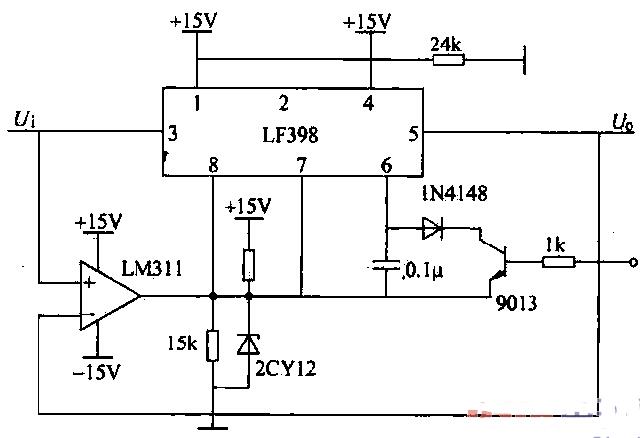

采樣保持電路通常被用在模數(shù)轉(zhuǎn)換器設(shè)計中,起到信號采集的作用。圖1是一個由開關(guān)和電容組成的采樣保持電路。在采樣階段,開關(guān)閉合且電容Chold采集輸入信號的信息。在保持階段,開關(guān)斷開Chold保存采樣時刻輸入信號的信息,從而實現(xiàn)信號的采樣和保持的功能。

圖1 采樣保持電路[1]

02開關(guān)寄生對采樣精度的影響

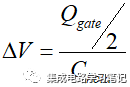

圖1所示的采樣保持電路中的開關(guān)可由一個簡單的MOS管實現(xiàn)。當開關(guān)導(dǎo)通時,溝道內(nèi)存在電荷會積累電荷Qgate。開關(guān)斷開后,這些電荷會流出到采樣電容上從而引起采樣誤差。這就是 “電荷注入” 。由電荷注入產(chǎn)生的誤差可表示為

其中,1/2是假設(shè)溝道中的一半電荷流入到采樣電容上。

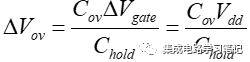

此外,時鐘饋通效應(yīng)也是引起采樣誤差的一個重要來源。MOS管的柵漏或柵源之間存在交疊電容Cov。采樣結(jié)束時鐘跳變時,會通過交疊電容饋通到采樣電容上,從而引起采樣誤差。由時鐘饋通而導(dǎo)致的誤差可表示為

可見時鐘饋通引入的是一個與輸入信號無關(guān)的失調(diào)電壓。

03解決時鐘饋通和電荷注入的幾種方法

1. 增加虛擬開關(guān)

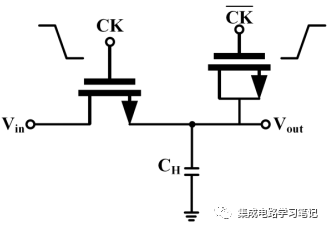

如圖2所示,相比于圖1增加了一個額外的虛擬開關(guān)。虛擬開關(guān)的狀態(tài)與采樣開關(guān)的狀態(tài)相反,且大小為采樣開關(guān)的二分之一。當采樣開關(guān)關(guān)斷時,溝道電荷Qgate的一半流向輸出端一側(cè),此時虛擬開關(guān)開啟并吸收采樣開關(guān)釋放的多余電荷。從而達到采樣電容上的輸入信號不被影響的目的。

該方法雖然簡單但也存在一定的問題。采樣開關(guān)不可能剛好向輸出一側(cè)注入一半的電荷。因此不能完全抑制電荷注入所引起的誤差。

圖2 增加虛擬開關(guān)

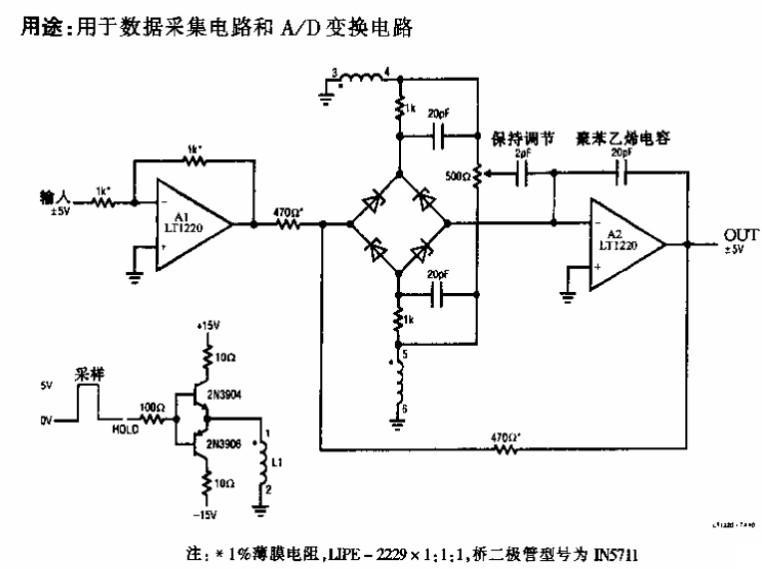

2. 底板采樣

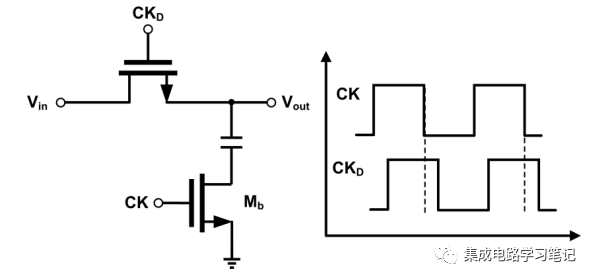

圖3為底板采樣技術(shù)的示意圖。當采樣結(jié)束時,晶體管Mb首先斷開,此時采樣電容下極板浮空,隨后另一個晶體管再關(guān)斷。因為采樣電容下極板浮空處于高阻狀態(tài),晶體管內(nèi)電荷不會流入采樣電容上,從而避免電荷注入而引起的采樣誤差。值得一提的是,該結(jié)構(gòu)無法解決時鐘饋通的問題。

圖3 底板采樣方法

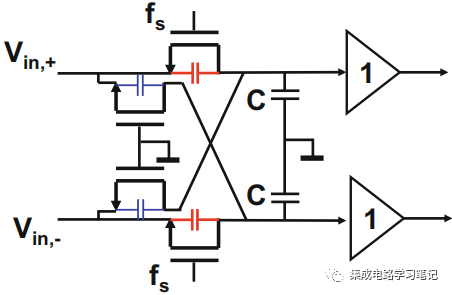

3. 差分采樣

在模擬集成電路設(shè)計中,差分是一種常見的消除偶次非線性的方法。如圖4所示,實際采樣電路中,不僅有時鐘饋通和溝道電荷注入等非理想因素,輸入信號通過MOS管的漏源寄生電容Cds(紅色標識)也會饋通到輸出端。通過增加兩個常關(guān)斷的MOS開關(guān)大小與采樣開關(guān)一致,并結(jié)合差分結(jié)構(gòu)可以有效的減小輸入信號饋通的影響。

該差分結(jié)構(gòu)相較于底板采樣等方法具有采樣精度高的優(yōu)點,但這是以增加功耗和面積換來的。

圖4 差分采樣結(jié)構(gòu)

-

adc

+關(guān)注

關(guān)注

99文章

6640瀏覽量

548298 -

信號

+關(guān)注

關(guān)注

11文章

2842瀏覽量

77918 -

模數(shù)轉(zhuǎn)換器

+關(guān)注

關(guān)注

26文章

3301瀏覽量

127969 -

寄生電容

+關(guān)注

關(guān)注

1文章

297瀏覽量

19656 -

采樣保持電路

+關(guān)注

關(guān)注

3文章

13瀏覽量

20149

發(fā)布評論請先 登錄

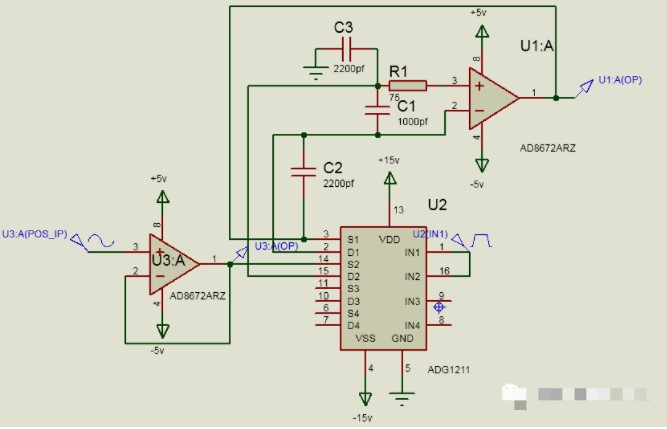

簡易的AD轉(zhuǎn)換器的采樣保持電路的模擬開關(guān)如何實際

采樣保持電路原理(S/H)

ADG1211開關(guān)實現(xiàn)采樣保持電路

評論