與硅器件相比,SiC MOSFET的跨導(增益)更低,內部柵極電阻更高,其柵極導通閾值可能低于2 V。因此,在關斷狀態(tài)下,必須向SiC MOSFET施加負柵源電壓(通常為-5 V)。SiC器件的柵源電壓通常要求在18 V ~ 20 V之間,以降低導通狀態(tài)下的導通電阻(RDS)。SiC MOSFET工作在低VGS下可能會導致熱應力或由于高RDS而可能導致故障。與低增益相關的其他影響會直接影響幾個重要的動態(tài)開關特性,在設計適當的柵極驅動電路時必須考慮這些影響,包括導通電阻、柵極電荷(米勒平臺)和過電流(DESAT)保護。

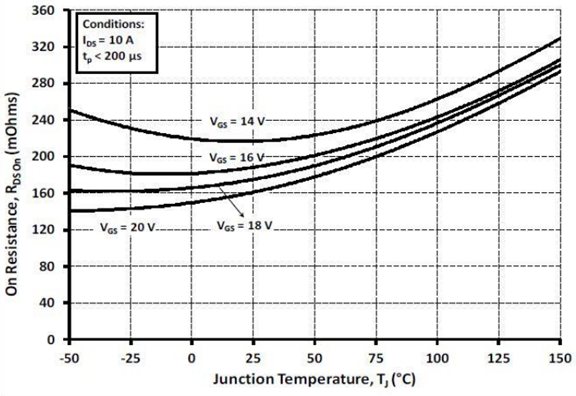

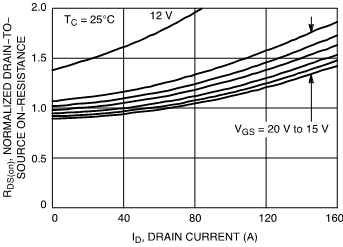

二導通電阻在低VGS時,一些SiC器件的導通電阻與結溫特性之間的關系曲線看起來是拋物線*(由于內部器件特性的組合)。(*這適用于安森美M1和M2 SiC MOSFET。)當VGS = 14 V時,RDS似乎具有負溫度系數(NTC)特性,即電阻隨溫度升高而降低。SiC MOSFET的這一獨特特征直接歸因于其低增益,這意味著如果兩個或更多的SiC MOSFET并聯(lián)工作在低VGS(負溫度系數)下,可能會導致災難性損壞。因此,只有當VGS足以確保可靠的正溫度系數工作時(即VGS>18V),才建議將SiC MOSFET并聯(lián)工作。

圖2:M3 SiC MOSFET的導通電阻與結溫之間的關系曲線

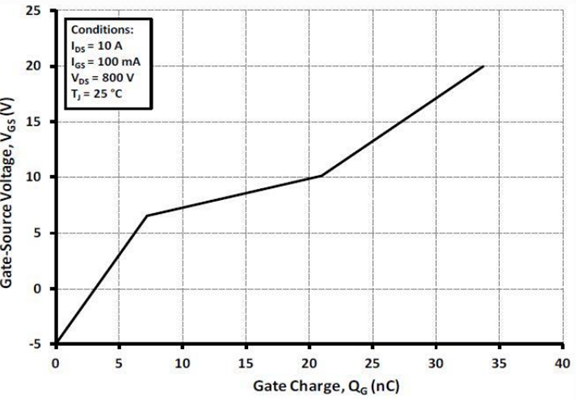

三柵極電荷向SiC MOSFET施加柵源電壓(VGS)時,電荷被傳輸以盡快使VGS從VGS(MIN)(VEE)和VGS(MAX)(VDD)升高。由于器件的內部電容是非線性的,因此可以使用VGS與柵極電荷(QG)的關系曲線來確定在給定的VGS下必須傳輸多少電荷。SiC MOSFET的這種 "米勒平臺 "發(fā)生在較高的VGS上,而且不像硅MOSFET那樣平坦。不平坦的米勒平臺意味著在相應的電荷范圍內,VGS不是不變的,這也是由于器件低增益導致的。同樣值得注意的是,QG = 0 nC(關斷SiC MOSFET所需的電荷量) 不會發(fā)生在VGS = 0 V時,因此VGS必須為負 (本例中為-5 V),以使柵極完全放電。

由于我們想測量導通或關斷SiC MOSFET所需的電荷量,我們的曲線只繪制了Qg的增量(或Qg的累積或Qg的變化)。這個數值也叫Qg。這可能會引起混淆。我們需要將這張圖解讀為需要的能量,而不純粹是存儲在柵源電容器中的能量。

圖3:SiC MOSFET柵源電壓與柵極電荷的關系

使用負柵極驅動阻斷電壓主要是為了減少關斷狀態(tài)下的漏電流。這也是由于跨導增益低造成的。使用負的阻斷電壓還可以減少開關損耗,主要是在關斷期間的開關損耗。

因此,幾乎對于所有的SiC MOSFET,都建議在關斷狀態(tài)下使用的最小VGS為-5 V < VGS(MIN) < -2 V,有些制造商規(guī)定電壓低至-10 V。

四欠壓保護(DESAT)DESAT保護是一種過電流檢測,起源于IGBT的驅動電路。在導通時,如果IGBT不能再保持飽和狀態(tài)("去飽和"),集電極-發(fā)射極電壓就會上升,同時全集電極電流流過。顯然,這對效率有不利影響,在最壞的情況下,可能導致IGBT的災難性故障。所謂的 "DESAT "功能監(jiān)測IGBT的集電極-發(fā)射極電壓,并檢測何時出現(xiàn)潛在的破壞性條件。雖然SiC MOSFET中的故障機制有些不同,但會有類似的情況,在最大ID流過時VDS可能上升。如果導通期間的最大VGS太低,柵極驅動導通沿太慢,或者存在短路或過載情況,就會出現(xiàn)這種不理想的條件。在滿載ID的情況下,RDS會增加,導致VDS意外上升。當SiC MOSFET發(fā)生欠飽和事件時,VDS的反應非常迅速,而最大漏極電流繼續(xù)流過不斷增加的導通電阻。當VDS達到預定的閾值時,就可以激活保護。應特別注意避免感測VDS的延遲,因為延遲會掩蓋這種現(xiàn)象。因此,DESAT是柵極驅動電路的一個重要的輔助性保護。

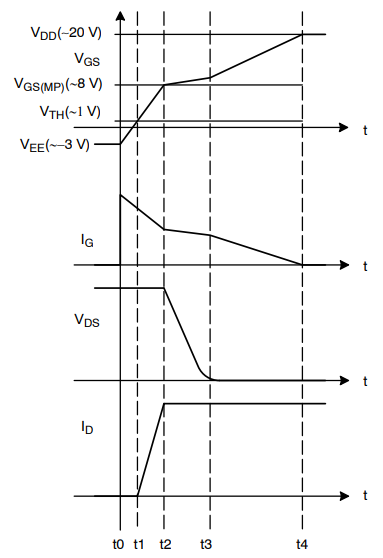

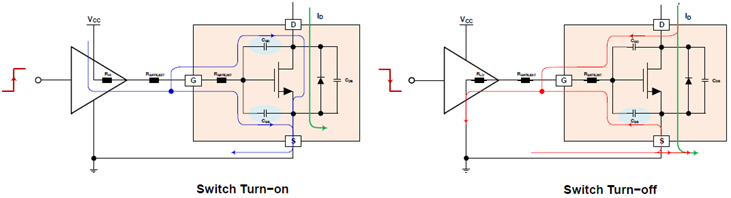

五動態(tài)開關SiC MOSFET的導通和關斷狀態(tài)有四個不同的階段。所示的動態(tài)開關波形呈現(xiàn)的是理想工作條件的情況。然而,在實踐中,封裝寄生物,如引線和邦定線電感、寄生電容和PCB布局會極大地影響實際波形。合適的器件選擇、最佳的PCB布局,以及對設計好的柵極驅動電路的重視,對于優(yōu)化開關電源應用中使用的SiC MOSFET的性能都是至關重要的。

圖4:SiC MOSFET導通序列的4個階段

六柵極驅動電路的設計要求為了補償器件低增益,同時實現(xiàn)高效、高速的開關,對SiC柵極驅動電路有以下關鍵要求:

-

對于大多數SiC MOSFET,驅動電壓在-5 V > VGS > 20 V之間時性能最佳。柵極驅動電路應能承受VDD = 25 V和VEE = -10 V,以適用于最廣泛的可用器件

-

VGS必須有快速的上升沿和下降沿(在幾ns范圍內)

-

在整個米勒平臺區(qū)域內,有能力提供高的峰值柵極灌電流和拉電流(數安培)

-

當VGS下降到米勒平臺以下時,需要提供一個非常低的阻抗保持或 "鉗位",以實現(xiàn)高的灌電流能力。灌電流的額定值應超過僅對SiC MOSFET的輸入電容放電所需的電流。10A左右的峰值灌電流最小額定值應適用于高性能、半橋電源拓撲結構

-

VDD欠壓鎖定(UVLO)水平,與開關開始前VGS>~16 V的要求相匹配

-

VEE UVLO監(jiān)測能力確保負電壓軌在可接受的范圍內

-

能夠檢測、報告故障和提供保護的去飽和功能,使SiC MOSFET長期可靠運行

-

支持高速開關的低寄生電感

-

小尺寸驅動器封裝,布局盡可能靠近SiC MOSFET

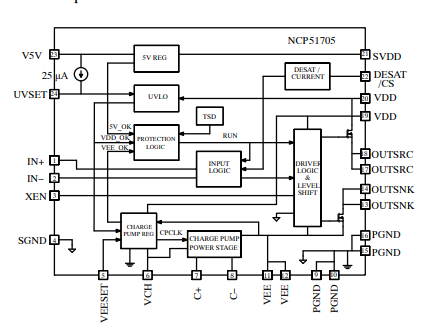

安森美的NCP51705是一款SiC柵極驅動器IC,提供高的設計靈活度和集成度,幾乎與任何SiC MOSFET兼容。NCP51705集成許多通用柵極驅動器IC所共有的功能,包括:

-

VDD正電源電壓最高28V

-

高峰值輸出電流:6 A拉電流和10 A灌電流

-

單獨的信號和電源接地連接

-

單獨的源和灌輸出引腳

-

內置熱關斷保護

-

單獨的非反相和反相TTL、PWM輸入

然而,該IC集成幾個獨特的功能,能夠以最少的外部元器件設計出可靠的SiC MOSFET柵極驅動電路。這些功能包括:

八總結

在選擇合適的柵極驅動器IC時,SiC MOSFET的低增益給設計人員帶來了難題。通用的低邊柵極驅動器不能高效和可靠地驅動SiC MOSFET。NCP51705集成一系列功能,為設計人員提供了一個簡單、高性能、高速的解決方案,高效、可靠地驅動SiC MOSFET。

希望以上這些內容可以在實際設計過程中對大家有所幫助。將安森美加入星標,更新不容錯過。點個星標,茫茫人海也能一眼看到我

原文標題:如何優(yōu)化SiC MOSFET的柵極驅動?這款IC方案推薦給您

文章出處:【微信公眾號:安森美】歡迎添加關注!文章轉載請注明出處。

-

安森美

+關注

關注

32文章

1674瀏覽量

91995

原文標題:如何優(yōu)化SiC MOSFET的柵極驅動?這款IC方案推薦給您

文章出處:【微信號:onsemi-china,微信公眾號:安森美】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

相關推薦

英飛凌推出新型MOTIX TLE9189柵極驅動器IC

電隔離柵極驅動器選型指南

新型驅動器IC優(yōu)化高速功率MOSFET的開關特性

柵極驅動ic和源極的區(qū)別 柵極驅動ic選型看哪些參數

WBG 器件給柵極驅動器電源帶來的挑戰(zhàn)

柵極驅動ic和源極的區(qū)別在哪

英飛凌推出新款雙通道隔離柵極驅動器IC

Littelfuse發(fā)布IX4352NE低側SiC MOSFET和IGBT柵極驅動器

Littelfuse宣布推出IX4352NE低側SiC MOSFET和IGBT柵極驅動器

用于SiC MOSFET和高功率IGBT的IX4352NE低側柵極驅動器

如何優(yōu)化SiC MOSFET的柵極驅動?這款IC方案推薦給您

如何優(yōu)化SiC MOSFET的柵極驅動?這款IC方案推薦給您

評論