以太網口是我們日常工程中常用的通信接口,以太網接口有很多種,本文將對常用以太網接口進行科普介紹。

1、GMII接口

1.1、GMII接口概述

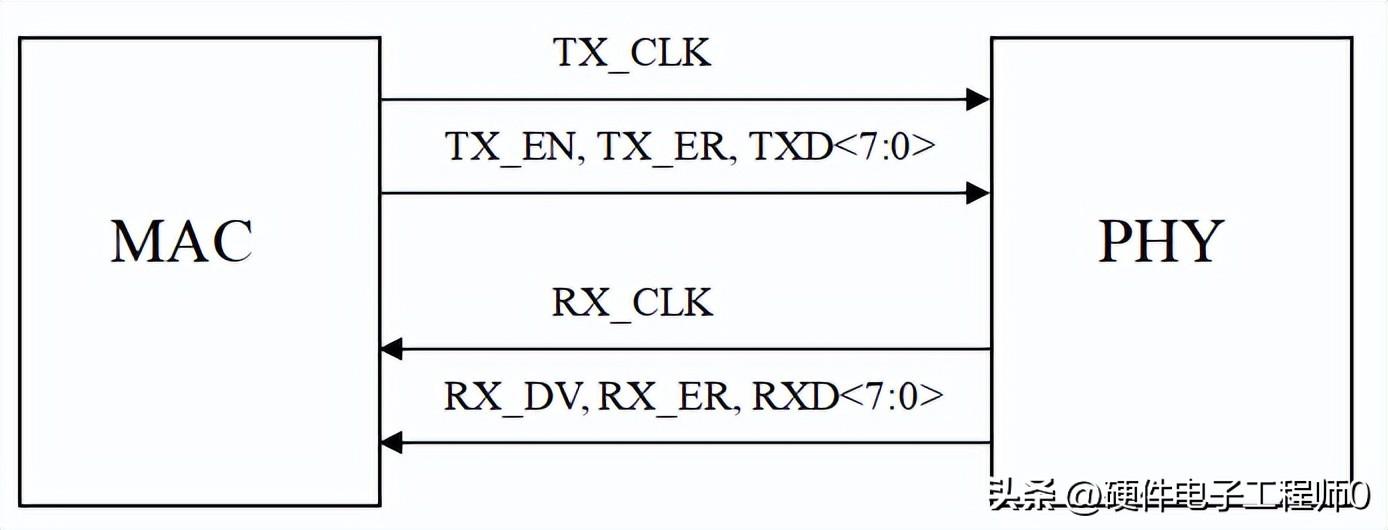

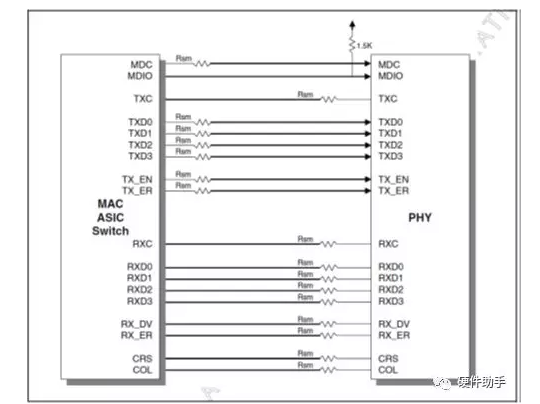

GMII接口屬于源同步時鐘類型(時鐘與數據都是由同一芯片驅動),時鐘速率125MHz,接口連接關系如圖1所示,22根線,其中TX_EN, TX_ER, TXD<7:0>這些信號同步于TX_CLK;RX_DV, RX_ER,

圖1 GMII接口原理框圖

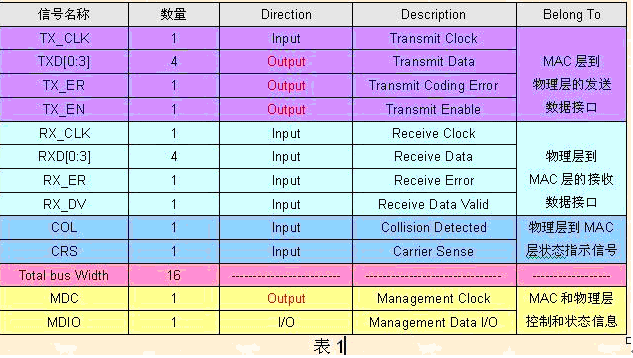

RXD<7:0>這些信號同步于RX_CLK。其它的兩個信號CRS, COL只用于半雙工模式,一般設計中不會用到,而且這兩個信號與時鐘是異步的,對這兩個信號不做要求。各信號說明見表1。

表1 UTOPIA LEVEL 2接口信號說明

| 信號名稱 | 信號說明 |

| TX_CLK | 發送方向時鐘信號 |

| TX_EN | 發送方向使能信號 |

| TX_ER | 發送方向錯誤指示信號 |

| TXD<7:0> | 發送方向數據信號 |

| RX_CLK | 接收方向時鐘信號 |

| RX_DV | 接收方向使能信號 |

| RX_ER | 接收方向錯誤指示信號 |

| RXD<7:0> | 接收方向數據信號 |

| COL | 碰撞指示信號 |

| CRS | 載荷檢測信號 |

1.2、設計原則

1、要求同方向的時鐘數據嚴格等長,即TX_EN, TX_ER, TXD<7:0>這些控制/數據信號與TX_CLK等長;RX_DV, RX_ER, RXD<7:0>這些控制/數據信號與RX_CLK等長。一般設計中,要求控制/數據信號與時鐘信號的長度差不大于1cm(約0.1ns)。

2、要求信號的發送端(包括時鐘/數據/控制信號)串接33歐姆電阻以減小反射,提高信號完整性。

3、信號走線中要注意保持阻抗的連續性,盡量減少過孔數量(一般過孔數量在3個以內)

4、因信號線較多,在布局允許情況下,PHY與MAC盡量靠近,減小高速信號受的串擾。

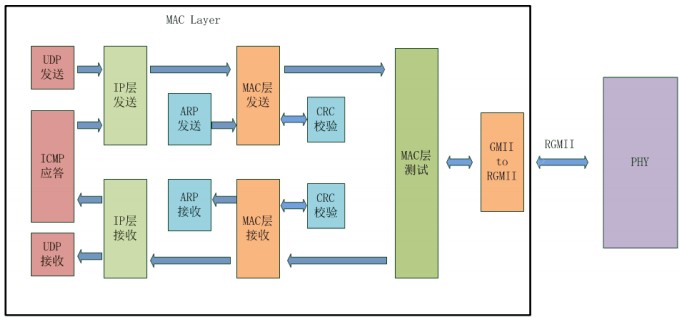

2、RGMII接口概述

2.1、RGMII接口概述

RGMII屬于源同步時鐘類型,最初是由HP制定的一個GMII精簡版專利標準,得到各大主流廠家的認可,成為一個普遍應用的關于xMII系列接口的標準。RGMII經歷了1.01.11.21.2a1.32.0幾個版本。從2.0版本開始支持HSTL,之前的版本支持2.5V CMOS。

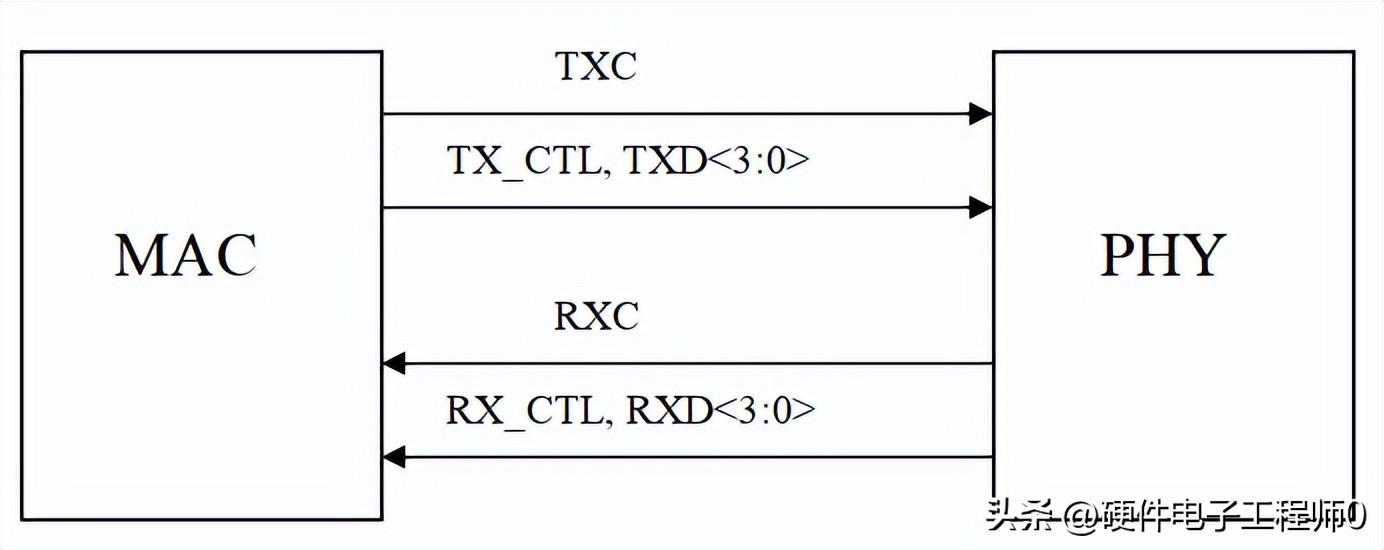

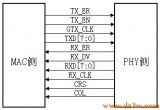

TXC/RXC時鐘頻率支持125MHz,25MHz,2.5MHz,可以適配1000M,100M,10M速率。在時鐘的上升沿和下降沿均進行數據采樣,相比GMII接口,數據信號線收發方向各減半變為4根,信號線總共有12根。如圖2和表2說明。

圖2 RGMII接口原理框圖

表2 RGMII接口信號說明

| 信號 | 方向 | 說明 |

| TXC | MAC-->PHY | 發送時鐘信號 |

| TX[3:0] | MAC-->PHY | 發送數據信號 |

| TX_CTL | MAC-->PHY | 發送控制信號 |

| RXC | MAC<--PHY | 接收時鐘信號 |

| RX[3:0] | MAC<--PHY | 接收數據信號 |

| RX_CTL | MAC<--PHY | 接收控制信號 |

2.2、設計原則

1、要求同方向的時鐘數據嚴格等長,即TX_CTL,TXD<3:0>這些控制/數據信號與TXC等長; RX_CTL,RXD<3:0>這些控制/數據信號與RXC等長。一般設計中,要求控制/數據信號與時鐘信號的長度差不大于0.5cm(約0.05ns)。

2、要求信號的發送端(包括時鐘/數據/控制信號)串接33歐姆電阻以減小反射,提高信號完整性。

3、信號走線中要注意保持阻抗的連續性,盡量減少過孔數量(一般過孔數量在3個以內)。

4、因信號線較多,在布局允許情況下,PHY與MAC盡量靠近,減小高速信號受的串擾,線長最好小于4000mil。

3、SS_SMII接口

3.1、SS_SMII 接口概述

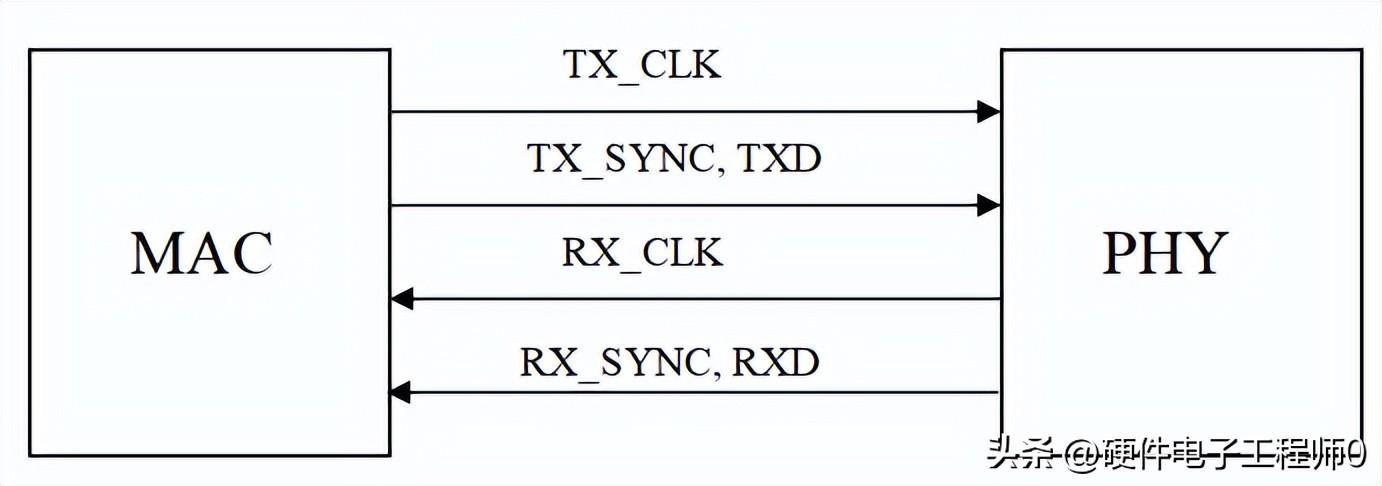

SS_SMII(又叫S3MII)接口屬于源同步時鐘類型,接口原理框圖如圖3所示,時鐘速率125M Hz;信號與時鐘間的關系等同于GMII。

圖3 S3MII接口原理框圖

3.2、SS_SMII接口設計原則

1、要求TX_SYNC, TXD信號與TX_CLK等長;RX_SYNC, RXD信號與RX_CLK等長。一般設計中,要求控制/數據信號與時鐘信號的長度差不大于1cm(約0.1ns)。

2、要求信號的發送端(包括時鐘/數據/控制信號)串接33歐姆電阻以減小反射,提高信號完整性。

3、信號走線中要注意保持阻抗的連續性,盡量減少過孔數量(一般過孔數量在3個以內)。

4、在時間允許的情況下,盡量對接口進行仿真。

4、SMII接口

4.1、SMII接口概述

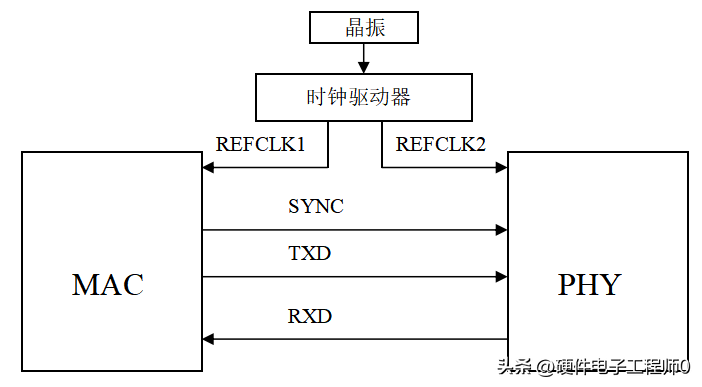

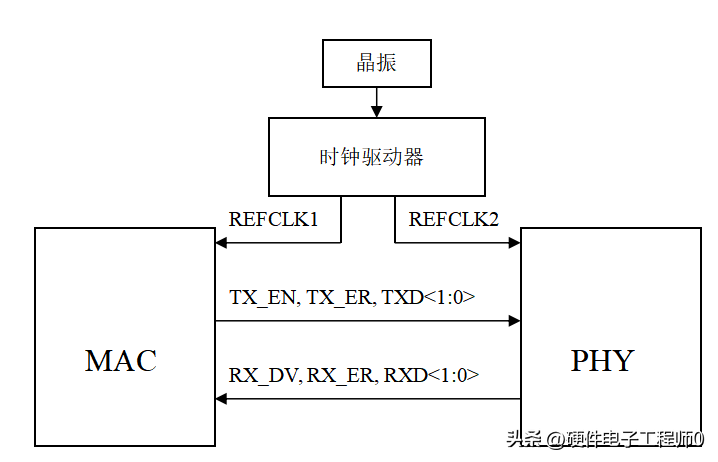

SMII接口公共時鐘模型(兩端芯片的時鐘來自共同的時鐘BUFFER),時鐘速率125M Hz,接口原理框圖如圖4所示;并不要求數據線與時鐘等長。

4.2、SMII接口設計原則

設計時可以先考慮使REFCLK1, REFCLK2等長。

圖4 SMII接口原理框圖

2、要求SYNC,TXD,RXD這幾個信號走線盡量短;(從芯片資料理論上看出這些線

的最大長度為1.5ns,21cm;但由于芯片差異性較大,因此實際布線中盡量走短)。

要求信號的發送端(包括時鐘/數據/控制信號)串接33歐姆電阻以減小反射,提高信號完整性;

信號走線中要注意保持阻抗的連續性,盡量減少過孔數量(一般過孔數量在3個以內)。

5、RMII接口

5.1、RMII接口概述

RMII接口屬于公共時鐘傳輸模型,時鐘速率50M Hz;并不要求數據線與時鐘等長。圖5所示為RMII接口的原理框圖。

圖5 RMII接口原理框圖

5.2、RMII接口設計原則

設計時可以先考慮使REFCLK1, REFCLK2等長。

要求其它的數據/控制信號走線盡量短;(RMII規范規定信號的驅動能力在包含負載輸入電容情況下不小于12inch,也就是30cm;但由于芯片差異,實際布線情況下盡量短)。

要求信號的發送端(包括時鐘/數據/控制信號)串接33歐姆電阻以減小反射,提高信號完整性。

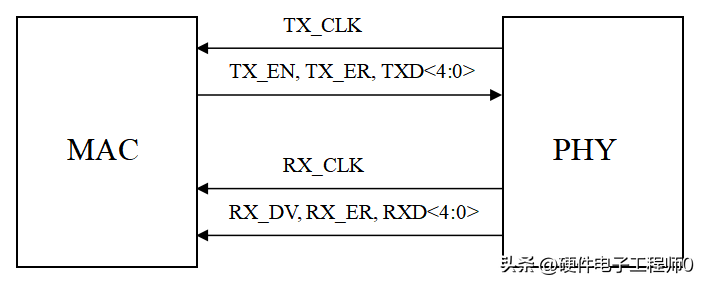

6、MII接口

MII接口屬于公共時鐘傳輸模型,時鐘頻率25M(100M以太網)或2.5M(10M以太網)。兩個時鐘都是由Phy發送給MAC的。接口框圖如圖6所示。另外,該接口的其它兩個信號CRS、COL是異步信號,無特殊要求,故不在此圖中畫出。

對于MII信號,由于信號速率較低,因此在布線上無特殊要求,只要求Phy與MAC離的不要太遠就可以了。

圖6 MII接口原理框圖

審核編輯:劉清

-

以太網

+關注

關注

40文章

5419瀏覽量

171598 -

Mac

+關注

關注

0文章

1104瀏覽量

51458 -

PHY

+關注

關注

2文章

301瀏覽量

51732 -

RMII

+關注

關注

0文章

8瀏覽量

12056 -

以太網接口

+關注

關注

0文章

147瀏覽量

17092

發布評論請先 登錄

相關推薦

針對10Mbps到100Gbps不同以太網Drive Side接口類型

摸透以太網的MAC和PHY之間的MII

具有單MII/RMII/Turbo MII支持LAN9303的以太網交換機

具有雙RMII或單MII / RMII / Turbo MII接口的全功能三端口以太網交換機

一文讀懂以太網MII/RMII/GMII三種接口

以太網基礎介紹:MII接口和RMII接口

以太網各種網絡總線介紹

以太網PHY芯片的MII接口和MDIO接口介紹

【科普】GMII/RGMII/S3MII/SMII/RMII/MII以太網接口基礎知識

【科普】GMII/RGMII/S3MII/SMII/RMII/MII以太網接口基礎知識

評論