本文基于VC_SpyGlass_CDC_UserGuide整理了3種常見的cdc(Clock Domain Crossing)錯誤。需要注意的是:

?本文描述的跨時鐘錯誤在特定場景下,有些是允許的,甚至有些是正常設計。因此IC設計者想要確認跨時鐘錯誤需要分析應用場景。

?還有一些CDC錯誤是spyglass 工具無法發現的,因此不能全部依賴工具檢查。

?有些項目組為了避免新手對cdc理解不深刻造成bug,對跨時鐘設計做了更加嚴格的規范。例如,下文中的裸跨是不允許存在的。

1、CDC Unsynchronized(沒有跨時鐘)

沒有采用跨時鐘模塊,即咱們通常說的裸跨,不同時鐘域的數據直接互連,會存在亞穩態問題。同步電路會進行STA(靜態時序分析)保證setup-hold time滿足要求,因此寄存器能夠保證正確采樣。而不同時鐘域的信號之間沒有setup-hold time要求,無法保證正確采樣。

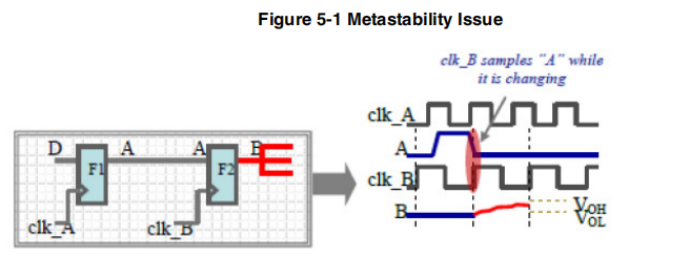

圖5-1 所示為亞穩態的案例,F1是clk_A時鐘域的寄存器,F2是clk_B時鐘域的寄存器,clk_A和clk_B是異步時鐘,寄存器F1的輸出信號A發生跳變的時刻有可能與clk_B的上升沿發生重疊,此時對寄存器F2來說,在setup-hold time時間區間內,輸入A沒有保持穩定,因此寄存器F2輸出的B是不確定狀態,這就是亞穩態。

解決方案:根據實際場景添加對應的跨時鐘模塊,例如bit同步器,脈沖跨時鐘模塊,異步fifo,多比特跨時鐘等等。

鴿子解讀1

沒有跨時鐘,不一定就是錯誤;在一些場景中,為了節約資源不跨時鐘是允許的。

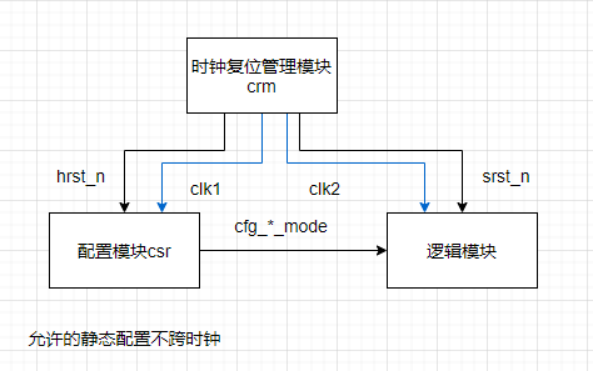

下圖所示案例:配置模塊csr模塊產生的配置信號cfg_*_mode是clk1時鐘域,直接用于clk2時鐘域的邏輯模塊。

在芯片使用過程中,復位和配置順序如下:hrst_n先釋放--->完成csr模塊寄存器配置--->釋放srst_n。

在srst_n復位釋放后,靜態配置cfg_*_mode不再發生改變。這種情況中,功能邏輯模塊處于復位狀態時,cfg_*_mode發生跳變,這種情況下即使發生了亞穩態也沒有影響,因為功能邏輯模塊還沒允許。

鴿子解讀2:

在部分握手機制的模塊中,沒有跨時鐘,也能保證不會出現亞穩態。

CDC無法識別是否實現握手機制,如果跨時鐘模塊實現握手機制,即能夠保證圖5-1中的F2準備采樣時信號A已保持穩定,雖然會報錯,但是不會出現亞穩態。在多bit的配置信號跨時鐘模塊中就存在這樣的情況。

2、CDC Glitch (毛刺)

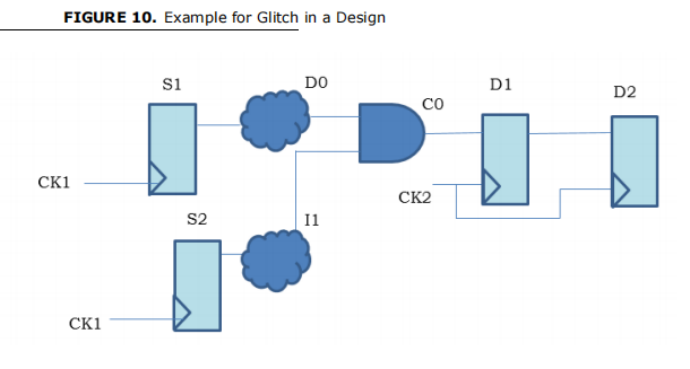

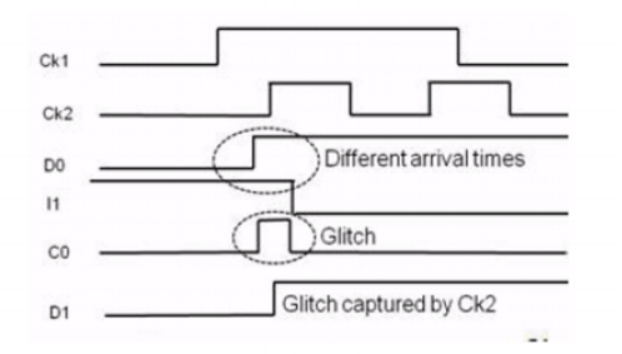

簡單來說,就是組合邏輯直接跨時鐘,組合邏輯會存在glitch,導致glitch被目的時鐘采樣到,導致出現不期望的信號

解決方案:增加源時鐘域寄存器打拍,寄存器輸出的信號才跨時鐘。

特殊場景:如果圖10中的D0或者I1是一個準靜態信號(幾乎不會跳變的),那么不會產生glitch,也是可以接受的。

Glitches的產生有如下三種場景:

1)同一個bit信號的組合邏輯跨時鐘

2)多個源時鐘域的信號的組合邏輯跨時鐘

3)同一個時鐘域的多個源信號的組合邏輯跨時鐘

3、CDC-Convergence(跨時鐘重新匯聚)

CDC-Convergence會產生不期望的信號組合,從而導致功能異常。

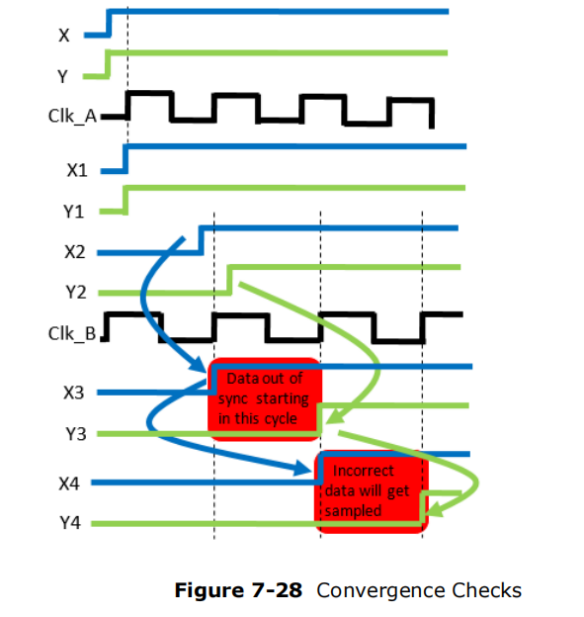

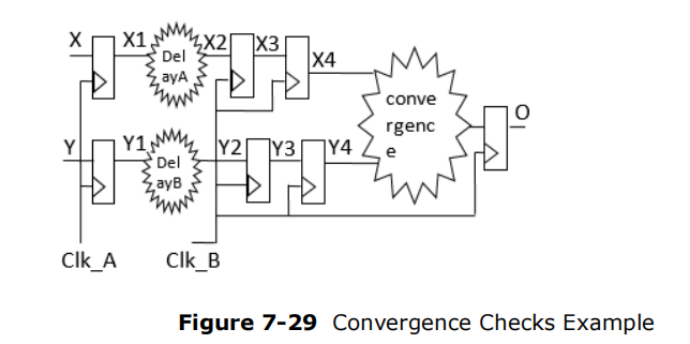

如果多個信號從源時鐘域通過不同的跨時鐘路徑進入目的時鐘域,然后這些信號在目的時鐘域中又聚合到一起,那么就有可能因為信號的重新聚合導致電路功能上的異常。例如下圖7-29和7-28中,x和y的組合(x,y)在同步前只有(1,1)和(0,0)的組合,在同步后出現了(1,0)的組合,還有可能出現(0,1)組合。

如下圖7-29和7-28所示,X、X1、Y和Y1 屬于clk_a時鐘域,delay A和delay B表示不同的延時(走線延時),X3,X4,Y3,Y4屬于clk_b時鐘域。clk_a和clk_b屬于異步時鐘。X4和Y4作為輸入進行組合邏輯獲得O。

假設因為某些原因,x和y的組合(x,y)只會出現2'b00 或者2‘b11的情況。在正確設計過程中,我們期望x4和y4的組合(x4,y4)也只會出現2'b00 或者2‘b11的情況。但是由于不同的跨時鐘路徑會導致(x4,y4)出現錯誤組合。見圖7-28,由于delay A和delay B的延時不同,導致X2和Y2到達同步器D端口的時間有差異,因此采樣后的值X3和Y3可能會出現一個clk_b周期的差異,此時(x3,y3)出現了2‘b10的組合,此組合會傳遞到(x4,y4)。因此輸出的Q可能是不符合預取的值。此為Convergence導致的錯誤

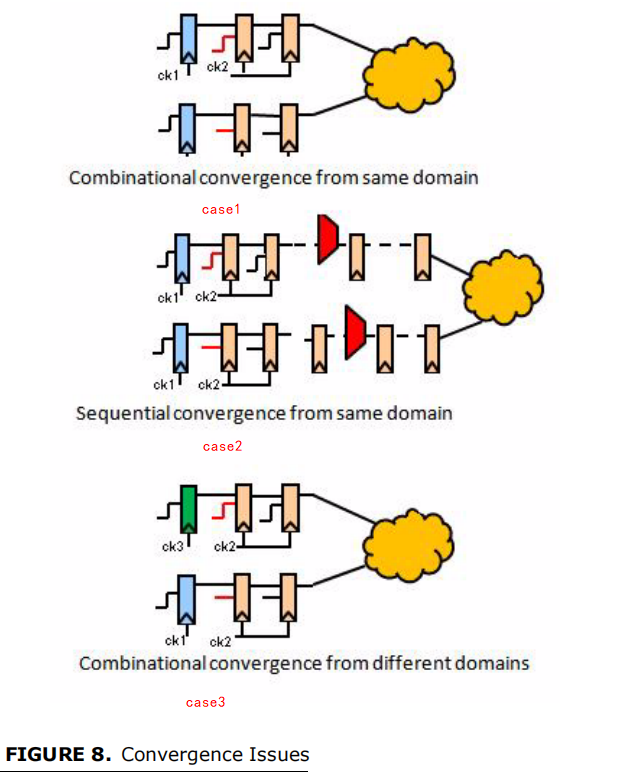

圖8顯示了3種匯聚的情況:

case1:同一個源時鐘域的信號同步后立即匯聚在組合邏輯

case2:源時鐘域信號同步后在目的時鐘域打了若干拍后再匯聚。如果當目的時鐘域打拍數量過大,例如20級,超過了spyglass 工具默認配置值,此種情況spyglass工具就無法檢查出問題了。

case3: 不同源時鐘域的信號同步后立即匯聚在組合邏輯

審核編輯:劉清

-

寄存器

+關注

關注

31文章

5336瀏覽量

120230 -

靜態時序分析

+關注

關注

0文章

28瀏覽量

9586 -

時鐘域

+關注

關注

0文章

52瀏覽量

9535 -

CDC技術

+關注

關注

0文章

9瀏覽量

6859

原文標題:Spyglass:你一定要懂的CDC錯誤

文章出處:【微信號:處芯積律,微信公眾號:處芯積律】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

你一定要懂的CDC錯誤

你一定要懂的CDC錯誤

評論