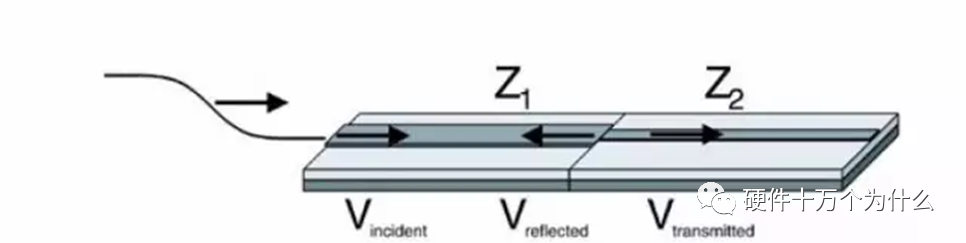

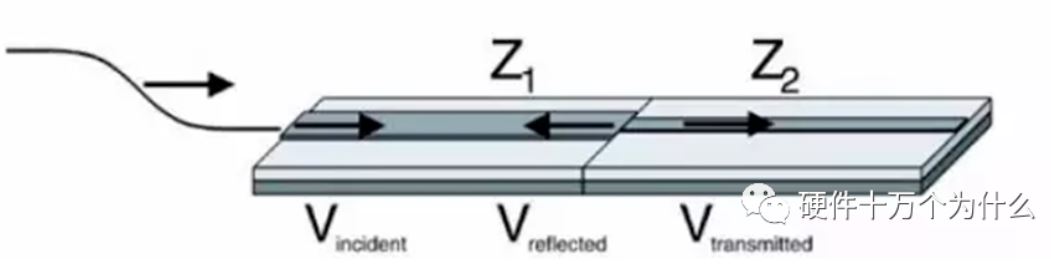

由于電信號在PCB上傳輸,我們在PCB設計中,可以把PCB走線認為是信號的通道。當這個通道的深度和寬度發生變化時,特別是一些突變時,都會產生反射。此時,一部分信號繼續傳播,一部分信號就可能反射。而我們在設計的過程中,一般都是控制PCB的寬度。所以,我們可以把信號走在PCB走線上,假想為河水流淌在河道里面。當河道的寬度發生突變時,河水遇到阻力自然會發生反射、旋渦等現象。

同樣的,信號在PCB上走線當遇到PCB的阻抗突變了,信號也會發生反射。

我們以光的反射類比信號的反射。光的反射,指光在傳播到不同物質時,在分界面上改變傳播方向,返回原來物質中的現象。光在碰到介質界面時,其折射率和反射率由。光線在臨界面上的反射率僅與介質的物理性能,光線的波長,以及入射角相關。

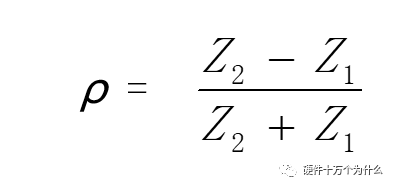

同樣的,信號/電磁波在傳輸過程中,一旦傳輸線瞬時阻抗發生變化,那么就將發生反射。信號的反射有一個參數叫作反射系數(ρ),計算公式如下:

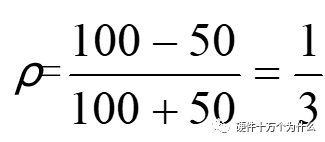

式中,Z1為變化前的阻抗;Z2為變化后的阻抗。假設PCB線條的特性阻抗為50Ω,傳輸過程中遇到一個理想的100Ω的貼片電阻接地,那么反射系數運用公式計算得到:

信號有1/3被反射回源端。反射系數ρ計算公式的推導過程,此處不展開。

信號沿傳輸線向前傳播時,每時每刻都會可能發生阻抗變化,如PCB走線寬度變化、PCB厚度變化、換層、電阻、電容、電感、過孔、PCB轉角、接插件、器件管腳;這個阻抗可能是傳輸線本身的,也可能是中途或末端其他元件的。對于信號來說,它不會區分到底是什么,信號是否反射,只會根據阻抗而變化。如果阻抗是恒定的,那么他就會正常向前傳播,只要阻抗發生了變化,不論是什么引起的,信號都會發生反射。

不管是COMS電路,還是SSTL電路,抑或是射頻電路,電路設計工程師希望整個傳輸鏈路阻抗都是一致的,最理想的情況就是源端、傳輸線和負載端都一樣。但實際總是事與愿違,因為發送端的芯片內阻通常會比較小,而傳輸線的阻抗又是50Ω,這就造成了不匹配,使信號發生反射。這種情況在并行總線和低速信號電路中常常出現,而通常對于高速SerDes電路而言,芯片內阻與差分傳輸線的阻抗是匹配的。

如果確實出現了阻抗不匹配,通常的做法是在芯片之外采用電阻端接匹配來實現阻抗一致性。常用的端接方式有源端端接、終端并聯端接、戴維寧端接、RC 端接、差分端接等。那端接電阻要使用幾顆?端接電阻怎么放置?阻值是選擇多大呢?

1、點對點拓撲結構

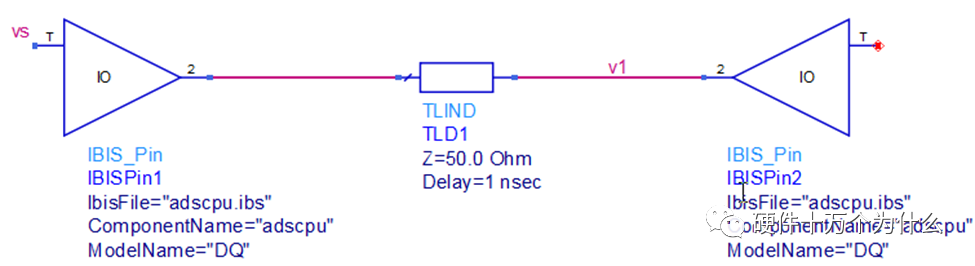

在介紹端接之前,先了解下電路的拓撲結構。電路的拓撲是指電路中各個元件之間的連接關系。常見的電路拓撲結構包括點對點的拓撲、星型拓撲、T型拓撲、菊花鏈拓撲等,最簡單的拓撲就是點對點拓撲結構的連接設計。點對點設計也是最常見的電路拓撲設計,尤其是在高速電路中幾乎都是點對點的連接設計。

點對點雖然簡單,但這種拓撲設計限制了帶負載的數量。點對點設計,由于驅動端的內部阻抗與傳輸線的阻抗常常不匹配,很容易就會形成信號反射,使信號失真。這就是一個信號完整性問題。

如下圖所示,是點對點的拓撲結構,由驅動端、傳輸線和接收端組成。

▲點對點無端接拓撲結構

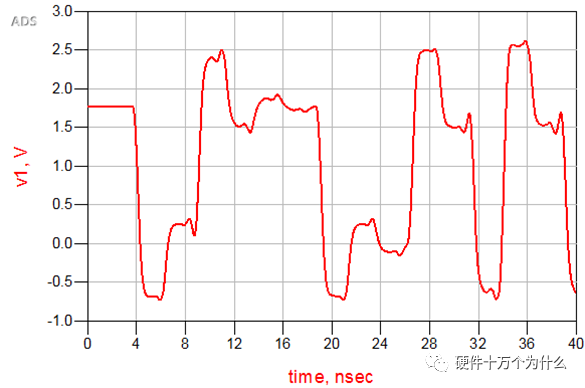

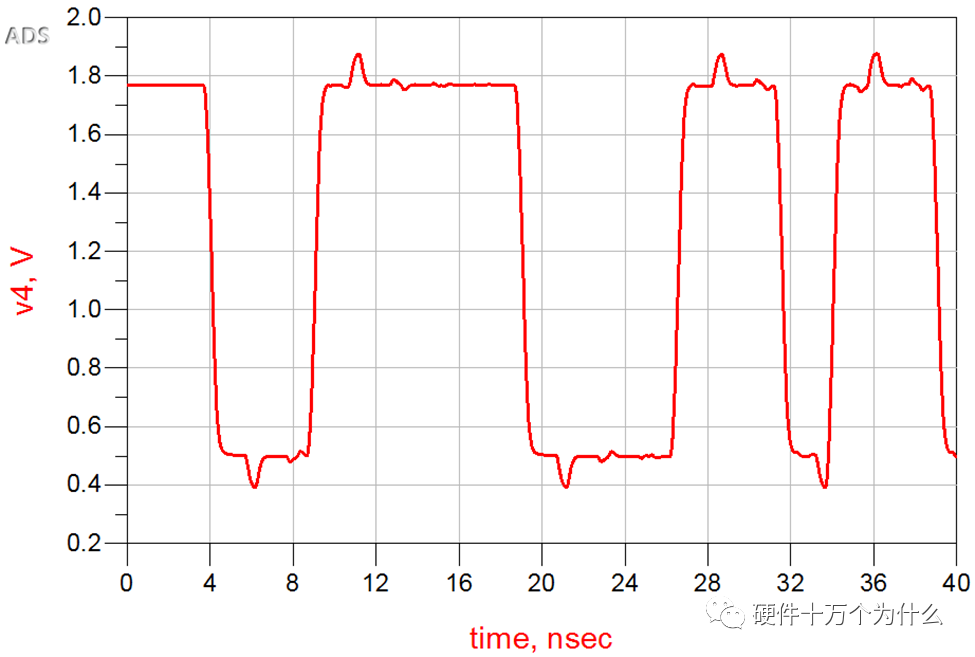

在這個電路拓撲中,其接收端的信號波形,如下圖所示:

▲點對點無端接的信號波形

從波形上分析,信號在高電平時穩定電壓在1.8V,但是最大值達到了2.619V,有819mV的過沖;最小值達到了-731mV,低于0V達到了731mV。這種情況在電路設計中需要盡量避免,因為這么大的過沖很容易損毀芯片,即使不損毀,也存在可靠性的問題。

所以,在設計中需要把過沖降低,盡量保證電壓幅值在電路可接受的范圍內,如此案例盡量保證滿足1.8V+/-5%,這時就需要通過 端接電阻來改善信號質量。

2、源端端接

源端端接設計也叫串聯端接設計,是一種常用的端接設計。端接方式是只在芯片端出來之后添加一顆端接電阻,盡量靠近輸出端。在此電路結構中,關鍵的是加多大阻值的電阻,需要根據電路的實際情況進行仿真或計算確認。

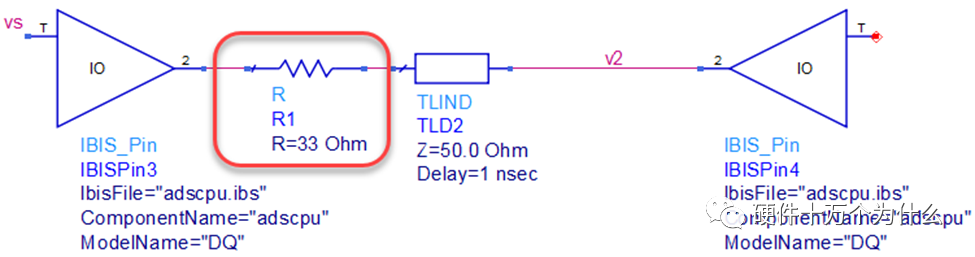

計算的原則是源端阻抗Rs與所加端接電阻R0的值等于傳輸線的阻抗Z0。在前面的點對點拓撲結構中,加入端接電阻值為33Ω的R1,其電路拓撲結構,如下圖所示。

▲源端端接拓撲結構

此時在接收端獲得的信號波形,如下圖所示:

▲源端端接后的波形

使用源端端接后,原本的存在的過沖已經基本消除,信號質量得到極大的改善。在加入源端端接電阻之后,信號的上升沿變緩,上升時間變長。

源端端接在電路匹配時,可以使電路匹配得非常好,但并不是適合于每一種電路設計。源端端接有自身的一些特性,大致歸納如下:

(1)源端端接非常簡單,只需要使用一顆電阻即可完成端接。

(2)當驅動端器件的輸出阻抗與傳輸線特性阻抗不匹配時,使用源端端接在開始就可以使阻抗匹配;當電路不受終端阻抗影響時,非常適合使用源端端接;如果接收端存在反射現象,就不適合使用源端端接。

(3)適用于單一負載設計時的端接。

(4)當電路信號頻率比較高時,或者信號上升時間比較短(特別是高頻時鐘信號)時,不適合使用源端端接。因為加入端接電阻后,會使電路的上升時間變長。

(5)合適的源端端接可以減少電磁干擾(EMI)輻射。

3、并聯端接

并聯端接即把端接電阻并聯在鏈路中,一般把端接電阻在靠近信號接收端的位置,并聯端接分為上拉電阻并聯端接和下拉電阻并聯端接。電路圖如下:

▲并聯端接拓撲結構

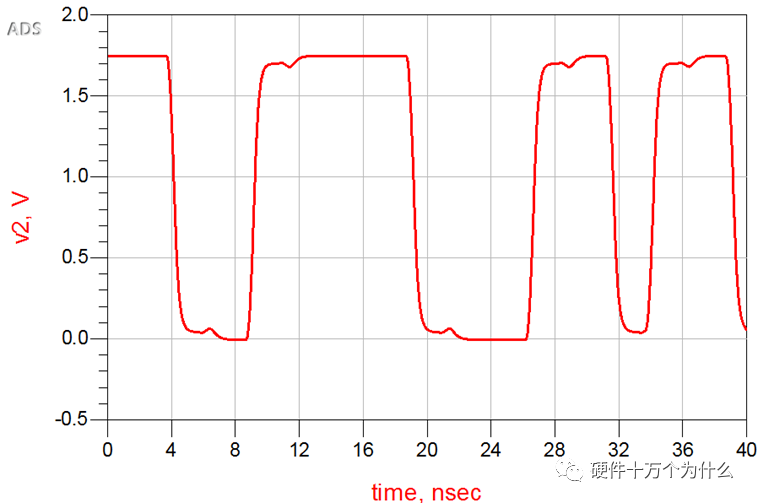

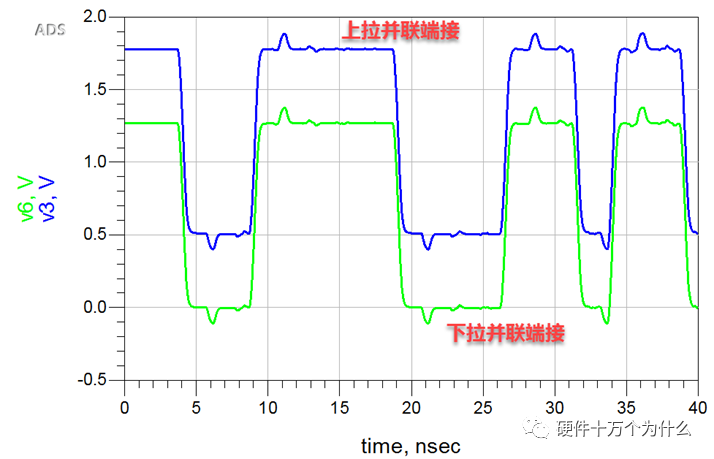

端接電阻值R0與傳輸線的阻抗一致。使用并聯端接后,其接收端的信號波形,如下圖所示:

▲并聯端接后的信號波形

從波形上分析,過沖基本被消除。上拉并聯端接的波形低電平有很明顯的上移,下拉并聯端接的波形高電平有很明顯的下移。不管是上拉并聯端接還是下拉并聯端接,信號波形的峰峰值都比使用源端端接時要小一些。

并聯端接放在接收端,所以能很好地消除反射,使用的元件也只有電阻。

從電路結構就可以看出,即使電路保持在靜態情況,并聯端接依然會消耗電流,所以驅動的電流需求比較大,很多時候驅動端無法滿足并聯端接的設計,在特別是多負載時,驅動端更加難以滿足并聯端接需要消耗的電流。所以,一般并聯端接不用于TTL和COMS電路。同時,由于幅值被降低,所以噪聲容限也被降低了。

4、戴維寧端接

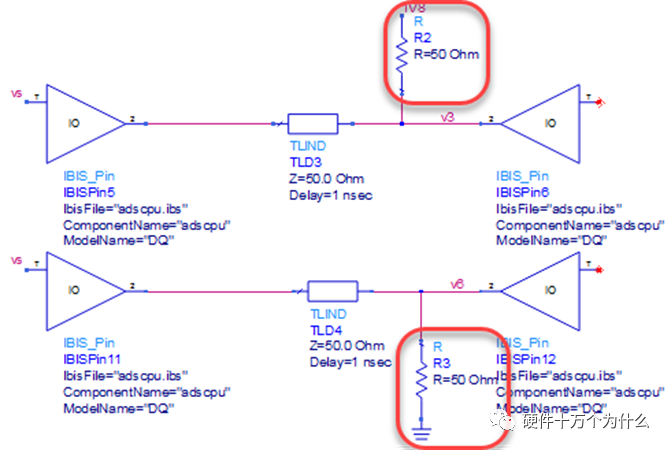

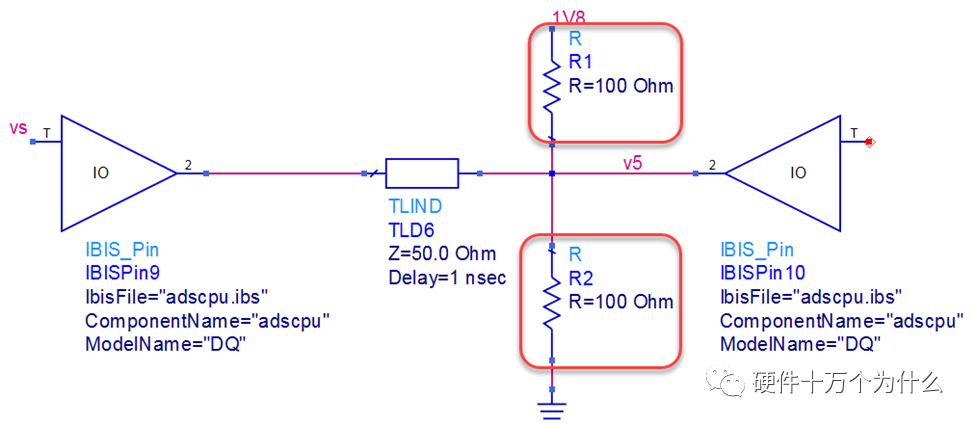

戴維寧端接就是使用兩顆電阻組成分壓電路,即用上拉電阻R1和下拉電阻R2構成端接,通過R1和R2吸收反射能量。戴維寧端接的等效電阻必須等于走線的特性阻抗。電路拓撲結構,如下圖所示:

▲戴維寧端接拓撲結構

使用戴維寧端接后,其接收端的信號波形,如下圖所示:

▲戴維寧端接后的信號波形

從上述信號波形分析,戴維寧端接匹配的效果也非常好,也基本能消除過沖的影響。

戴維寧端接方式,由于一直存在直流功耗,所以對電源的功耗要求比較多,也會降低源端的驅動能力。從信號接收端的波形可以看出,戴維寧端接的幅度降低了,所以噪聲容限也被降低。同時,戴維寧端接需要使用兩顆分壓電阻,電阻的選型也相對比較麻煩,使很多電路設計工程師在使用這類端接時總是非常謹慎。

DDR2和DDR3的數據和數據選通信號網絡的ODT端接電路就采用了戴維寧端接。

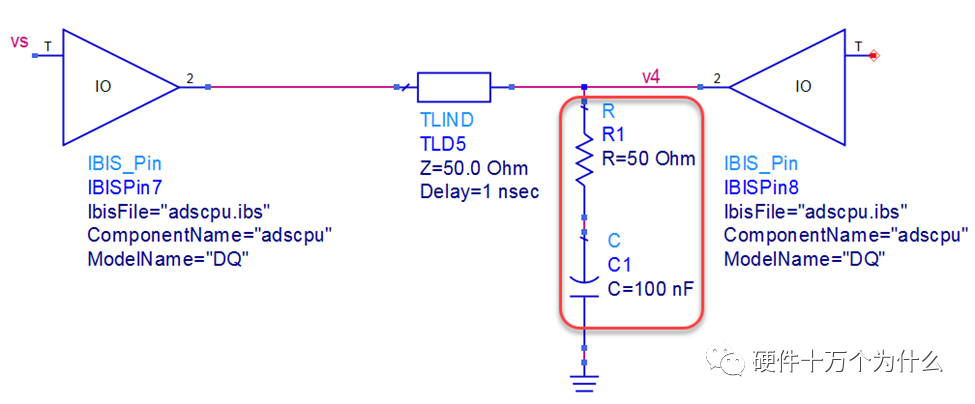

5、RC端接

RC端接在并聯下拉端接的電阻下面增加一顆電容,并下拉到地,所以RC端接是由一顆電阻和一顆電容組成的端接。RC端接也可以看作是一種并聯端接。電阻值的大小等于傳輸線的阻抗,電容值通常取值比較小。RC端接電路的拓撲,如下圖所示:

▲RC端接拓撲結構

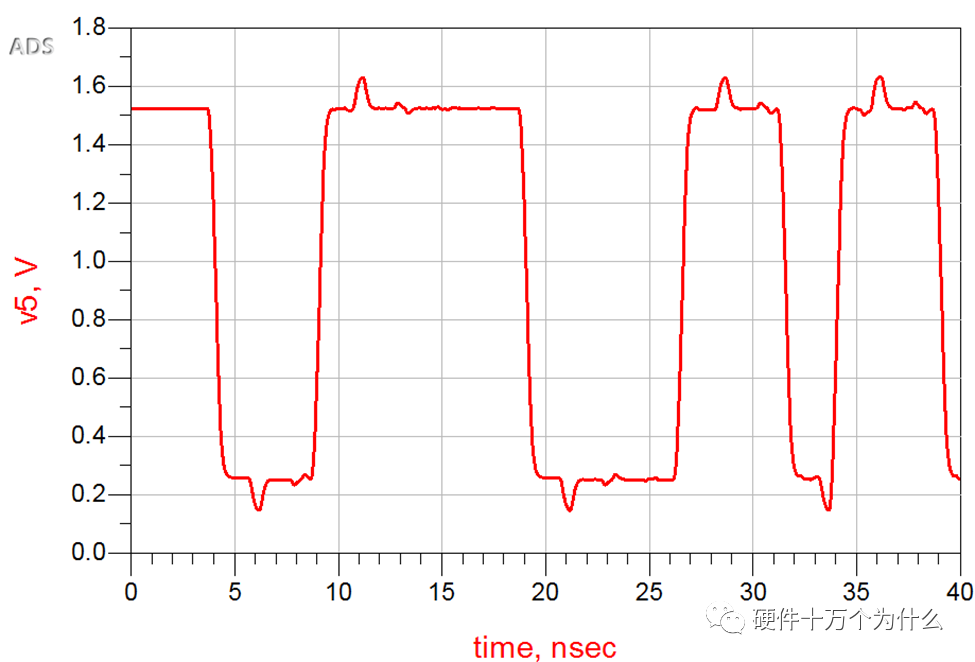

使用RC端接后,其接收端的信號波形,如下圖所示:

▲RC端接后的信號波形

從接收端的波形分析,RC端接也使過沖基本被消除了。RC端接能非常好的消除源端帶來的反射影響,但是RC電路也有可能導致新的反射。由于RC端接電路中有電容存在,所以電路靜態時的直流功耗非常小。

信號波形的低電平電壓提升了很多,所以RC端接后電路的噪聲容限被降低。RC端接后,由于引入了RC延時電路,所以信號波形邊沿也明顯的變緩慢,其變化程度與RC端接的電阻值和電容值有直接關系。所以,RC端接并不適合非常高速的信號及時鐘電路的端接。同時,RC端接方式需要使用電阻和電容兩顆器件。

從上面分析的幾種電阻端接類型來看,基本都能達到電路匹配端接的效果,使信號在傳遞過程中保持信號不失真,即滿足信號完整性的設計要求。對于電子產品設計而言,這是一個系統工程,其中涉及各個方面,包括信號完整性設計與電源完整性,也包括電磁兼容性、電路可靠性、可加工性、成本等。那么,在使用電阻端接來解決反射問題時,也要考慮到這些方面的原因。在實際項目的應用中,就需要根據項目工程的應用選擇電阻端接的類型。

總而言之,從電氣性能的角度來講,電阻端接匹配不僅僅可以改善信號質量,還可以用于控制信號邊沿變化的速率,即控制信號的上升時間;也可以改變信號電平的類型,即起到轉換的作用。

來源:硬件十萬個為什么

審核編輯:湯梓紅

-

電阻

+關注

關注

86文章

5507瀏覽量

171924 -

pcb

+關注

關注

4319文章

23080瀏覽量

397510 -

信號

+關注

關注

11文章

2789瀏覽量

76730 -

拓撲結構

+關注

關注

6文章

323瀏覽量

39189

原文標題:為什么在PCB走線上串個電阻?有什么用?

文章出處:【微信號:mcu168,微信公眾號:硬件攻城獅】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

信號線上串個小電阻干啥用的?

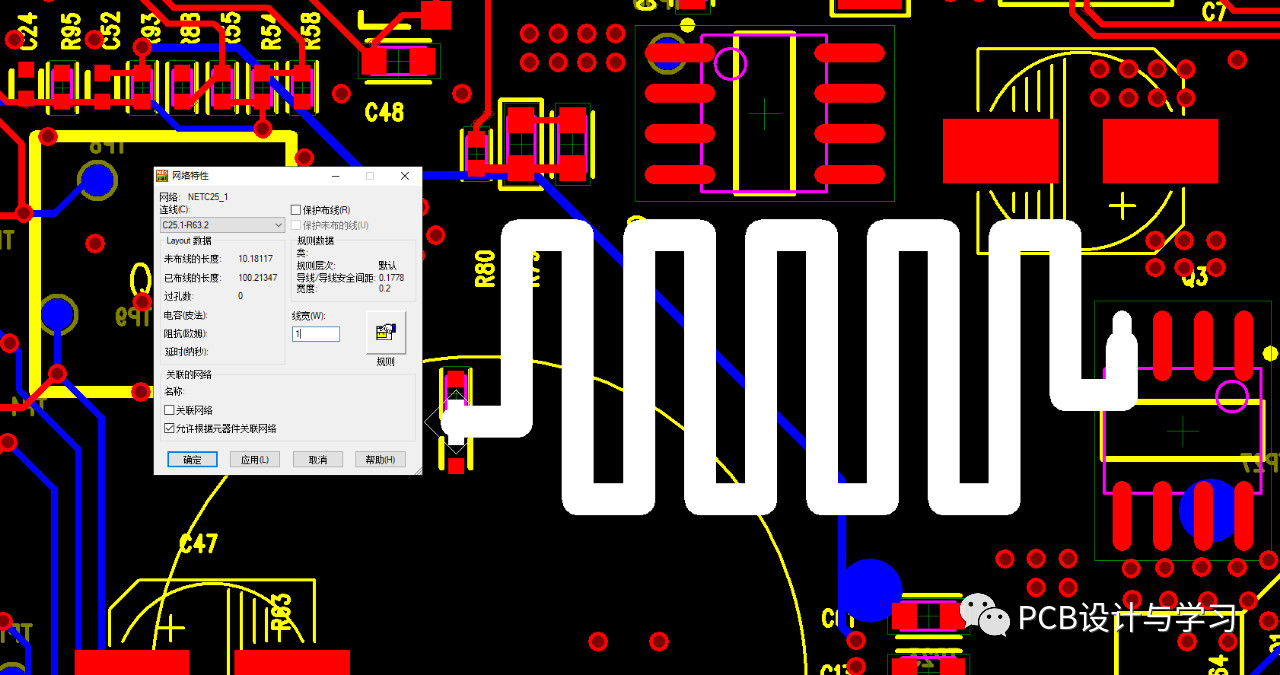

PCB布局之蛇形走線

用PCB走線來設計一個采樣電阻

如何利用PCB走線設計一個0.05歐姆的采樣電阻?

PCB走線上串個電阻的作用

PCB走線上串個電阻的作用

評論