據統計,超過30%的半導體故障是由靜電放電(ESD)造成的。根據美國ESD協會的定義,ESD是指“由高靜電場引起的靜電電荷快速、自發轉移”。ESD會擾亂電子系統的正常運行,導致設備發生故障。ESD引起的損壞情況有很多,從泄漏、短路到結和金屬化燒毀、柵極氧化物破裂、電阻-金屬接口劣化等,不一而足。在現實生活中,ESD引起的芯片故障示例包括:智能手機漏電、健身追蹤器屏幕閃爍,或自動緊急制動系統失靈。

為了盡可能地降低ESD的影響,半導體公司在芯片中集成了保護器件或電路。這些元器件的功能實際上就是為了形成低電阻率放電電流路徑,從而防止內部電路以及保護元件本身在ESD事件期間受到損壞。如果實施得當,保護元件能夠提供很好的保護效果,但要如何在最新的工藝節點上進行抗ESD的硅片設計,這也變得越來越有挑戰性。事實上,單片式片上系統(SoC)中封裝了數十億個電路,供ESD保護元件使用的區域非常有限,而且這些元件需要經過精心的布置和驗證。此外,在Multi-Die系統中,處理器、存儲器和互連之間還存在復雜的熱電相互作用,進而會產生一系列新的ESD問題。

本文將進一步討論不斷演化的ESD挑戰如何促使半導體公司利用新一代全芯片設計工具來增強傳統的靜態檢查器,從而快速分析芯片并仿真數百萬種瞬態ESD電涌。

設計具有ESD保護的芯片

在集成電路(IC)中,ESD事件通常會感應產生0.1-10 A的電流,并耗散大約10-100 W的能量。為了盡可能地降低或消除靜電放電的影響,首先第一步便是設計出耐靜電放電的產品和組件。

絕緣材料具有至少1.0 x1011Ω的表面電阻或體積電阻,有助于防止和限制電子流動。耗散材料則可在絕緣材料和導電材料之間提供電阻。根據ESD協會的規定,這些耗散材料的表面電阻應大于或等于1.0 x 104Ω,小于1.0 x 1011Ω,或者體積電阻大于或等于1.0 x 104Ω,小于1.0 x 1011Ω。

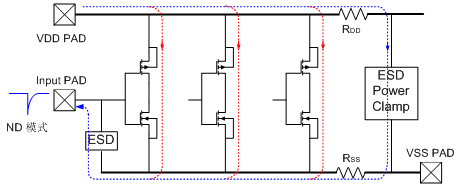

除了絕緣材料和耗散材料之外,片上ESD保護結構也發揮著重要作用。保護結構提供安全的ESD放電路徑(放電到接地母線/地軌),從而保護核心電路的輸入、輸出和電源引腳。在系統正常運行期間,這些保護結構通常處于不活動狀態。發生ESD事件時,保護電路會將引腳箝位至低電壓,并在釋放過量電流后關斷。

用于構建保護箝位的器件主要有以下三種:

二極管:二極管結構簡單,滿足低壓ESD應用的關鍵要求。正向偏置時,二極管具有低導通電壓和低導通電阻,能夠處理高ESD電流,被認為是最有效的保護元件之一。然而,在反向偏置條件下,二極管具有高導通電壓、高導通電阻和低電流處理能力。

柵極接地N溝道MOSFET:柵極接地N溝道MOSFET(GGNMOS)通常用于保護基于CMOS的設計。盡管GGNMOS在結構和操作上與常規MOS相似,但為了盡可能地提高ESD性能,布局技術會有所不同。GGNMOS器件可以在主動模式或急速返回(snapback)模式下運行,其中急速返回模式是最常見和最有效的模式。

可控硅整流器:可控硅整流器(SCR)采用雙極傳導機制,常被評為最高效、最魯棒的ESD保護器件。盡管SCR很容易“閂鎖”,即在ESD事件結束后傳導電流,但通過優化芯片設計可以有效彌補這一缺點。

驗證芯片對瞬態ESD電涌的承受能力

半導體公司使用多種器件級標準來驗證芯片對瞬態ESD電涌的承受能力,包括人體模型(HBM)和充電器件模型(CDM)。根據ESD協會的定義,HBM代表從站立人體的指尖傳遞到器件的放電情況。HBM通常以100 pF電容為模型,由高壓電源通過高歐姆電阻(通常為兆歐級)充電,隨后通過開關元件和1.5 kW(1,500Ω)串聯電阻放電。標準HBM波形包括2-10 ns的上升時間、0.67 A/kV的峰值電流以及寬度為200 ns的雙指數衰減。

CDM事件則指帶電器件接觸接地物體時的放電情況。具體來說,器件是電荷源,通過接地體放電。CDM測試步驟包括:將器件放在場板上,使引線朝上,然后給器件充電再放電。所有引腳都被同等對待,并在正充電和負充電后放電。CDM事件是現代電路中ESD故障的主要原因。盡管放電持續時間通常不到1ns,但峰值電流可能達到數十安培,從而導致顯著壓降和介質擊穿。

全面的全芯片ESD分析

半導體公司發現,定期執行CDM測試并獲得一致的結果變得越來越困難。由于CDM直接受環境影響,因此需要精確的芯片和封裝基板數據,才能準確定義仿真變量。然而,獲取這些數據并進行仿真比以往任何時候都更具挑戰性,因為高密度的單片SoC通常包含數十億個電路,而新的Multi-Die系統在單個封裝中的多個芯片之間引入了復雜的熱電相互作用。

事實上,ESD故障可能發生在金屬互連、ESD器件本身以及ESD器件要保護的核心器件上。雖然金屬互連是ESD放電路徑的關鍵要素,但對它們的評估通常是手動進行的,或是使用非專用的工具來完成,這些工具無法獨立地對大型復雜芯片或Multi-Die系統中的CDM電流進行仿真。因此,半導體公司現在利用全芯片ESD工具來驗證互連、ESD器件和核心器件能否承受HBM和CDM事件。

全芯片ESD工具可以突出顯示有風險的設計,精確定位易受影響的器件,并自動生成電流密度違規和高電阻路徑的報告。此外,全芯片ESD工具可以對整個芯片和封裝進行瞬態仿真,幫助分析所有的互連以及保護元器件,包括感應器、電感和電容。全芯片ESD工具還可以對電路布局驗證(LVS)前后的干凈布局進行分析,從而快速識別和糾正潛在問題。最后,層次化調試可以從宏觀和微觀角度審視芯片設計,給出關于ESD問題的精細洞察。

結語

ESD事件導致了超過三分之一的半導體故障,因而我們需要盡可能地降低ESD影響。為此,芯片開發者在芯片中集成了保護器件和電路,以形成低電阻率放電電流路徑。雖然保護元件在實施得當時效果非常好,但隨著高密度SoC中封裝的電路數量達到數十億,而Multi-Die系統又會引入新的ESD問題,因此在采用先進制程工藝的芯片中,ESD保護設計變得越來越具挑戰性。為了準確驗證互連、ESD器件和核心器件對HBM和CDM事件的承受能力,半導體公司需要專用的ESD工具來全面分析所有互連和元器件,同時對整個芯片和封裝進行瞬態仿真。

原文標題:全芯片ESD工具為復雜SoC提供超強保護力!讓芯片不再被“電”

文章出處:【微信公眾號:新思科技】歡迎添加關注!文章轉載請注明出處。

-

新思科技

+關注

關注

5文章

800瀏覽量

50364

原文標題:全芯片ESD工具為復雜SoC提供超強保護力!讓芯片不再被“電”

文章出處:【微信號:Synopsys_CN,微信公眾號:新思科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

HDMI接口的ESD保護方案

全芯片ESD工具為復雜SoC提供超強保護力!讓芯片不再被“電”

全芯片ESD工具為復雜SoC提供超強保護力!讓芯片不再被“電”

評論