CoWos是最流行的 GPU 和 AI 加速器封裝技術(shù)。

人工智能正在蓬勃發(fā)展。每個人都想要更多的人工智能加速器,而主要的限制因素是將5nm ASIC 和 HBM 組合在一起的 CoWos 先進封裝。這種容量不足導致 GPU 短缺,這種短缺將持續(xù)到明年第二季度。

本文主要聚焦供給側(cè)。臺積電正在向設備制造商緊急訂購,以填充其位于竹南的新先進封裝工廠。三星、英特爾、Amkor、JCET 和 ASE 也在擴展他們的一些競爭技術(shù),以分得一杯羹。由于一些通用數(shù)據(jù)中心支出被生成型人工智能支出(例如內(nèi)存和 CPU)所蠶食,了解仍在增長的支出對于了解供應鏈至關(guān)重要。在這篇文章中,我們將詳細介紹 CoWos 的制造工藝流程。

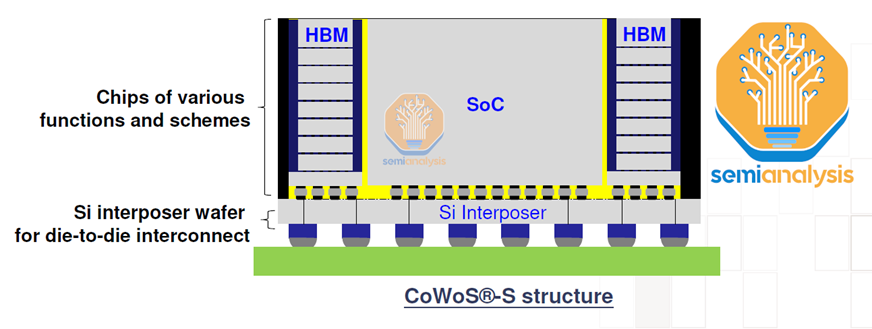

CoWoS 是臺積電的一種“2.5D”封裝技術(shù),其中多個有源硅芯片(通常的配置是邏輯和 HBM 堆棧)集成在無源硅中介層上。中介層充當頂部有源芯片的通信層。然后將內(nèi)插器和有源硅連接到包含要放置在系統(tǒng) PCB 上的 IO 的基板上。CoWos是最流行的 GPU 和 AI 加速器封裝技術(shù),因為它是共同封裝 HBM 和邏輯以獲得訓練和推理。

我們現(xiàn)在將詳細介紹 CoWoS-S(主要變體)的關(guān)鍵制造步驟。

硅中介層關(guān)鍵工藝步驟

第一部分是制造硅中介層,其中包含連接芯片的“電線”。這種硅中介層的制造類似于傳統(tǒng)的前端晶圓制造。人們經(jīng)常聲稱硅中介層是采用 65 納米工藝技術(shù)制造的,但這并不準確。CoWoS 中介層中沒有晶體管,只有金屬層,可以說它與金屬層間距相似,但事實并非如此。

這就是為什么 2.5D 封裝通常由領(lǐng)先的代工企業(yè)內(nèi)部完成,因為他們可以生產(chǎn)硅中介層,同時還可以直接訪問領(lǐng)先的硅。雖然 ASE 和 Amkor 等其他OSAT 已完成類似于 CoWoS 或 FOEB 等替代品的先進封裝,但他們必須從 UMC 等代工廠采購硅中介層/橋接器。

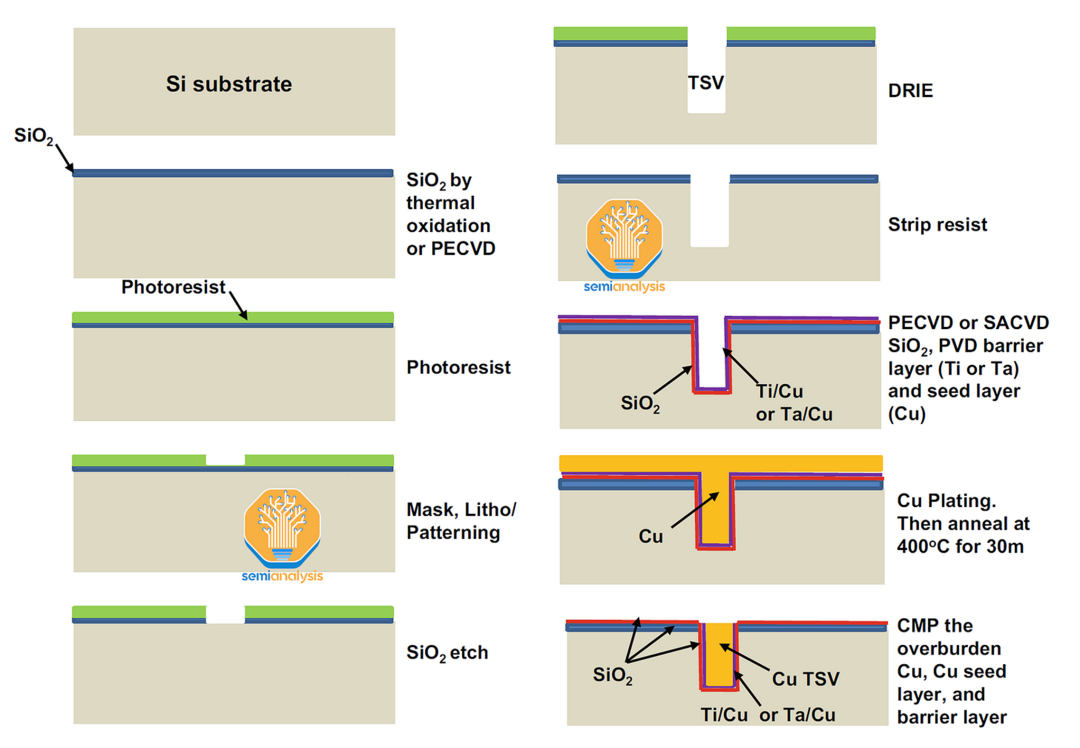

硅中介層的制造首先采用空白硅晶圓并生產(chǎn)硅通孔(TSV)。這些 TSV 穿過晶圓,提供垂直電氣連接,從而實現(xiàn)中介層頂部的有源硅(邏輯和 HBM)芯片與封裝底部的 PCB 基板之間的通信。這些 TSV 是芯片向外界發(fā)送 I/O 以及接收電源的方式。

為了形成 TSV,晶圓上涂有光致抗蝕劑,然后使用光刻技術(shù)進行圖案化。然后使用深反應離子蝕刻 (DRIE) 將 TSV 蝕刻到硅中,以實現(xiàn)高深寬比蝕刻。使用化學氣相沉積 (CVD) 沉積絕緣層(SiOX、SiNx)和阻擋層(Ti 或 TA)。然后使用物理氣相沉積(PVD) 沉積銅種子層。然后使用電化學沉積 (ECD) 用銅填充溝槽以形成 TSV。通孔不穿過整個晶圓。

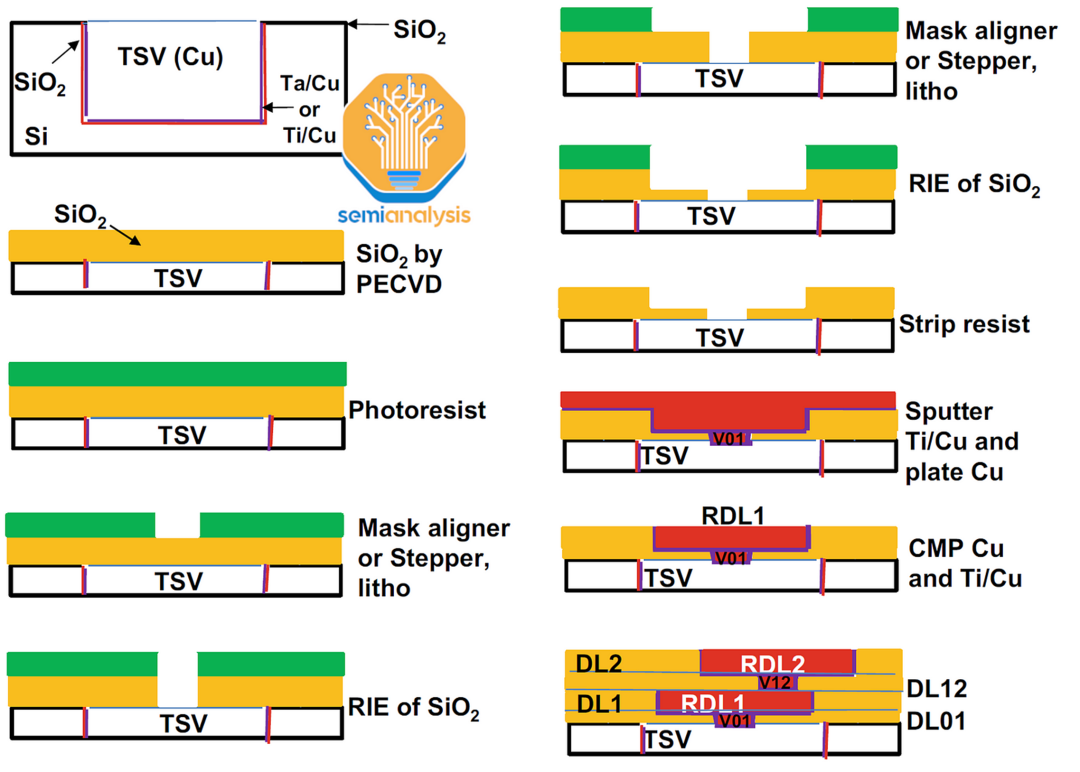

TSV 制造完成后,再分布層 (RDL) 將形成在晶圓的頂部。將 RDL 視為將各種有源芯片連接在一起的多層電線。每個 RDL 由較小的通孔和實際 RDL 組成。

通過 PECVD 沉積二氧化硅 (SiO2),然后涂覆光刻膠并使用光刻對 RDL 進行圖案化,然后使用反應離子蝕刻去除 RDL 通孔的二氧化硅。此過程重復多次,以在頂部形成較大的 RDL 層。

在典型的配方中,濺射鈦和銅,并使用電化學沉積(ECD) 沉積銅。然而,我們認為臺積電使用極低 k 電介質(zhì)(可能是 SiCOH)而不是 SiO2 來降低電容。然后使用 CMP 去除晶圓上多余的電鍍金屬。主要是標準的雙鑲嵌工藝。對于每個附加 RDL,重復這些步驟。

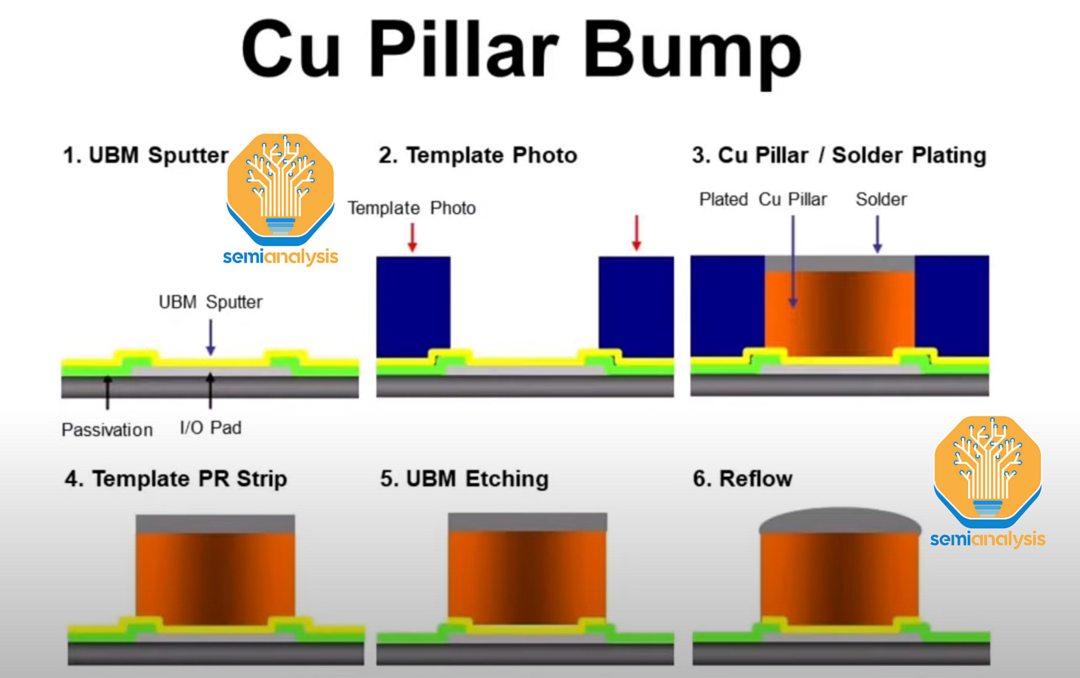

在頂部 RDL 層上,通過濺射銅形成凸塊下金屬化 (UBM) 焊盤。施加光致抗蝕劑,通過光刻曝光以形成銅柱圖案。銅柱經(jīng)過電鍍,然后用焊料覆蓋。光刻膠被剝離,多余的 UBM 層被蝕刻掉。UBM 和隨后的銅柱是芯片連接到硅中介層的方式。

晶圓上芯片關(guān)鍵工藝步驟

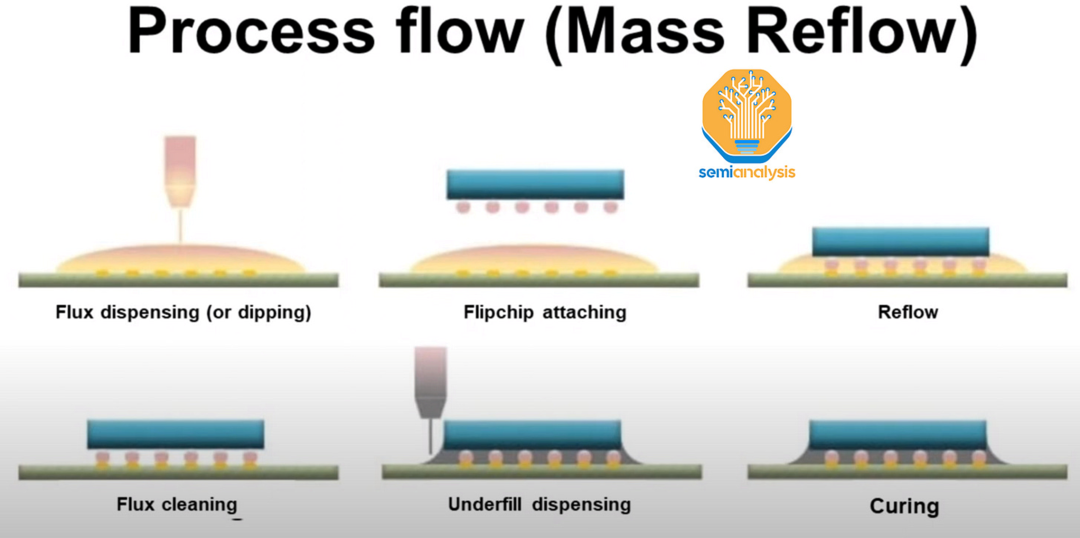

現(xiàn)在,使用傳統(tǒng)的倒裝芯片大規(guī)模回流工藝將已知的良好邏輯和 HBM 芯片附著到中介層晶圓上。助焊劑涂在中介層上。然后,倒裝芯片接合機將芯片放置到中介層晶圓的焊盤上。然后將放置有所有芯片的晶圓放入回流焊爐中烘烤,以固化凸塊焊料和焊盤之間的連接。清除多余的助焊劑殘留物。

然后用樹脂填充有源芯片和中介層之間的間隙,以保護微凸塊免受機械應力。然后再次烘烤晶圓以固化底部填充膠。

接下來,用樹脂對頂部芯片進行模制以將其封裝,并使用 CMP 使表面光滑并去除多余的樹脂。現(xiàn)在,通過研磨和拋光將模制中介層翻轉(zhuǎn)并減薄至約100um 厚度,以露出中介層背面的 TSV。

盡管已變薄,但附接到中介層晶圓頂部的頂部管芯和封裝可以為晶圓提供足夠的結(jié)構(gòu)支撐和穩(wěn)定性,因此并不總是需要載體晶圓來支撐。

基板上晶圓關(guān)鍵工藝步驟

中介層的背面經(jīng)過電鍍和 C4 焊料凸點凸點處理,然后切成每個單獨的封裝。然后,再次使用倒裝芯片將每個中介層芯片附著到增層封裝基板上以完成封裝。

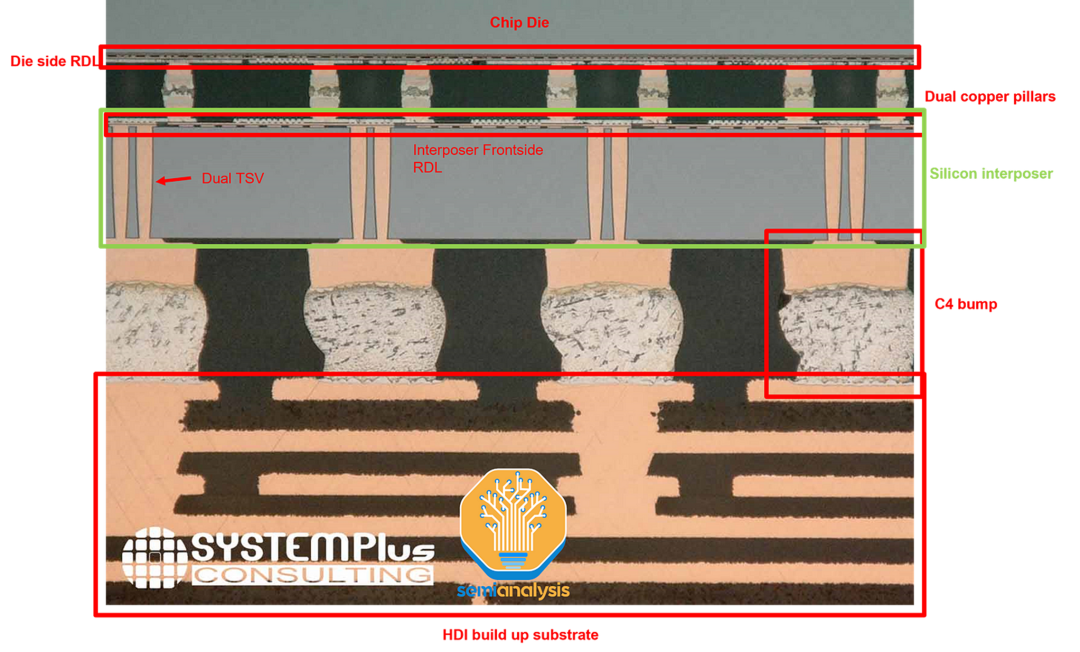

在下面英偉達 A100 的 SEM 橫截面中,我們可以看到 CoWoS 封裝的所有各個元素。

頂部是帶有 RDL 的芯片芯片和銅柱微凸塊,這些銅柱微凸塊粘合到硅中介層正面的微凸塊上。然后是頂部有 RDL 的硅中介層。我們可以看到 TSV 穿過中介層,下面每個 C4 凸塊有 2 個 TSV。底部是封裝基板。

請注意,A100 的中介層正面僅有單面 RDL。A100的架構(gòu)更簡單,只有內(nèi)存和GPU,因此路由要求更簡單。MI300由內(nèi)存、CPU 和 GPU 組成,全部位于AID 之上,因此這需要更復雜的 CoWoS,從而影響成本和產(chǎn)量。

審核編輯:劉清

-

人工智能

+關(guān)注

關(guān)注

1792文章

47409瀏覽量

238923 -

硅芯片

+關(guān)注

關(guān)注

0文章

91瀏覽量

16995 -

CoWoS

+關(guān)注

關(guān)注

0文章

140瀏覽量

10501 -

HBM

+關(guān)注

關(guān)注

0文章

384瀏覽量

14779 -

AI加速器

+關(guān)注

關(guān)注

1文章

69瀏覽量

8654

原文標題:AI 擴展 - CoWoS 和 HBM 的供應鏈分析

文章出處:【微信號:ICViews,微信公眾號:半導體產(chǎn)業(yè)縱橫】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

利用Minitab應對供應鏈中斷問題

CoWoS先進封裝技術(shù)介紹

智能制造裝備行業(yè)的供應鏈特點分析

華立搭乘CoWoS擴產(chǎn)快車,封裝材料業(yè)績預翻倍

7.行業(yè)研究及十五五規(guī)劃分析報告(行業(yè)發(fā)展環(huán)境分析和行業(yè)供應鏈分析)

印能科技3.5代產(chǎn)品打入美光科技HBM供應鏈

AI芯片需求猛增,CoWoS封裝供不應求,HBM技術(shù)難度升級

HBM供應商議價提前,2025年HBM產(chǎn)能產(chǎn)值或超DRAM 3分

臺積電新版CoWoS封裝技術(shù)拓寬系統(tǒng)級封裝尺寸

英偉達超級芯片供應鏈市場分析

戴爾榮獲Gartner供應鏈的最高榮譽“年度供應鏈突破獎”

CoWoS和HBM的供應鏈分析

CoWoS和HBM的供應鏈分析

評論