今天一位工程師問了我一個問題,“一個模塊有幾個輸入管腳,V+、V-、signal、Gnd,還有金屬外殼,甲方測試驗收的時候,分別打V+對外殼、V-對外殼,Signal對外殼,Gnd對外殼,打的電壓還挺高,至少幾百伏,有的電路板就給打壞了,問這種打法有問題沒有?是不是還是說明了我們設(shè)計的模塊有問題?“

類似的問題,在這一兩年間,在一些大型科研單位里也發(fā)生過兩三次。甚至后來都找到了某些GB電氣安全標準的制定人,但也是爭論半天,因為很多標準只是國外標準翻譯過來的,也沒說清真正的依據(jù)。知其然,知其所以然,才是治學之道。

那到底應(yīng)該怎么做呢?為什么這樣做呢?

首先說結(jié)論,應(yīng)該把所有管腳接在一起,然后統(tǒng)一對外殼打耐壓,才是正確的方式。

原因是電路中的某些地方確實是有可能存在絕緣強度的隱患的,最常見的部位之二是DIP封裝的器件Pin腳,在電路板固定后,與金屬板之間的間距小;二是電路板固定安裝孔附近的螺絲與電路板的走線或覆銅層的間距小;當然還有很多其他的地方。

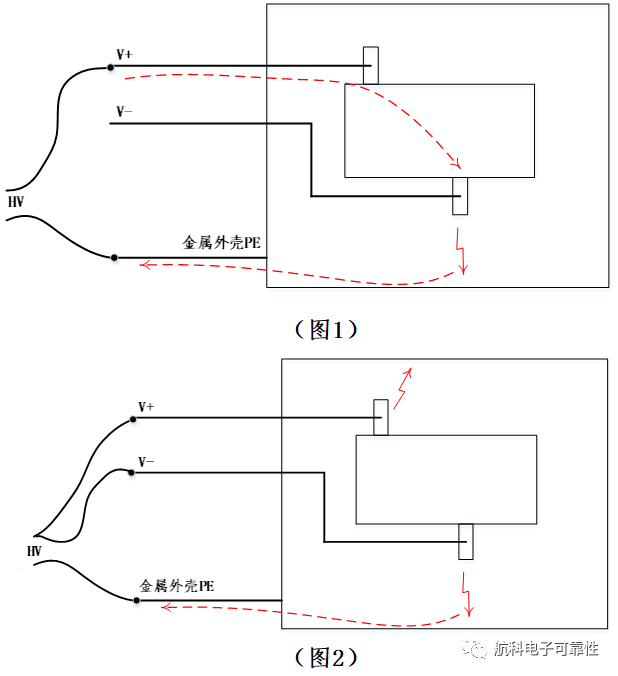

萬一模塊中有這種絕緣阻抗不足的情況時,各腳單獨對外殼打高壓,就容易形成如(圖1)的情況,圖中V+對外殼打耐壓,但電路中的某個pin腳對外殼距離很近,則有可能形成如圖紅線的泄放通路,泄放電流如此之大,器件焉能不壞?如果實際工況中不會有任何距離外殼近的情況發(fā)生,即使V+加上了高壓,沒有泄放通路,整塊單板也會處于一個高壓等電位,板上沒有壓差形不成電流,板子也不會壞。

總結(jié)成一句話:

如果沒隱患,兩種打法都沒問題;

如果有隱患,則單pin分別對外殼打,則有損傷內(nèi)部電路的風險。

如果采用了所有輸入引腳接在一起后,統(tǒng)一對外殼打的方式,就算是某些pin腳存在了對外殼的絕緣強度不夠的問題,因為所有輸入管腳的等電位,在電路中的器件自身里內(nèi)部不易形成放電通路,可以有效地保護器件。

總結(jié)成一句:

所有輸入管腳接在一起,對外殼打耐壓,可以遇到有隱患的電路板則可以更好的保護,避免損壞。

當然,可能有杠頭會說一個觀點,如果電路中的某個中間電路的引腳對外殼很近,那V+V-雖然等電位,但會不會兩邊包抄通過這個引腳對外殼放電呢?答案是仍有可能的。不過這種情況發(fā)生的概率確實會相對比較低得多。

北京漢通達科技主要業(yè)務(wù)為給國內(nèi)用戶提供通用的、先進國外測試測量設(shè)備和整體解決方案,產(chǎn)品包括多種總線形式(臺式/GPIB、VXI、PXI/PXIe、PCI/PCIe、LXI等)的測試硬件、相關(guān)軟件、海量互聯(lián)接口等。經(jīng)過二十年的發(fā)展,公司產(chǎn)品輻射全世界二十多個品牌,種類超過1000種。值得一提的是,我公司自主研發(fā)的BMS測試產(chǎn)品、芯片測試產(chǎn)品代表了行業(yè)一線水平。

-

電路

+關(guān)注

關(guān)注

172文章

5926瀏覽量

172353 -

測試

+關(guān)注

關(guān)注

8文章

5315瀏覽量

126709 -

耐壓

+關(guān)注

關(guān)注

0文章

31瀏覽量

10573

發(fā)布評論請先 登錄

相關(guān)推薦

使用ADS1298的12導聯(lián)心電記錄儀絕緣耐壓測試,絕緣耐壓測試不通過是什么原因呢?

熔斷器的耐壓測試方法

chroma 19053耐壓測試器-美國致茂

請問AMC1200絕緣耐壓是如何測試的?

耐壓絕緣測試儀測變電站的絕緣性能

耐壓絕緣測試儀在電路板應(yīng)用

絕緣耐壓測試的一個爭議問題

絕緣耐壓測試的一個爭議問題

評論