理解了寄存器的原理,在了解實(shí)際電路設(shè)計(jì)方法之前,先讓我們了解一下,在數(shù)字集成電路設(shè)計(jì)時,需要處理一些什么樣的信號類型,并且如何通過常用的電路結(jié)構(gòu)實(shí)現(xiàn)對這些信號的處理,以便應(yīng)用到實(shí)際電路的設(shè)計(jì)工程中。

時鐘信號

RTL設(shè)計(jì)以同步電路設(shè)計(jì)為基礎(chǔ),這意味著在某個局部電路中,所有寄存器都被同一個時鐘驅(qū)動。

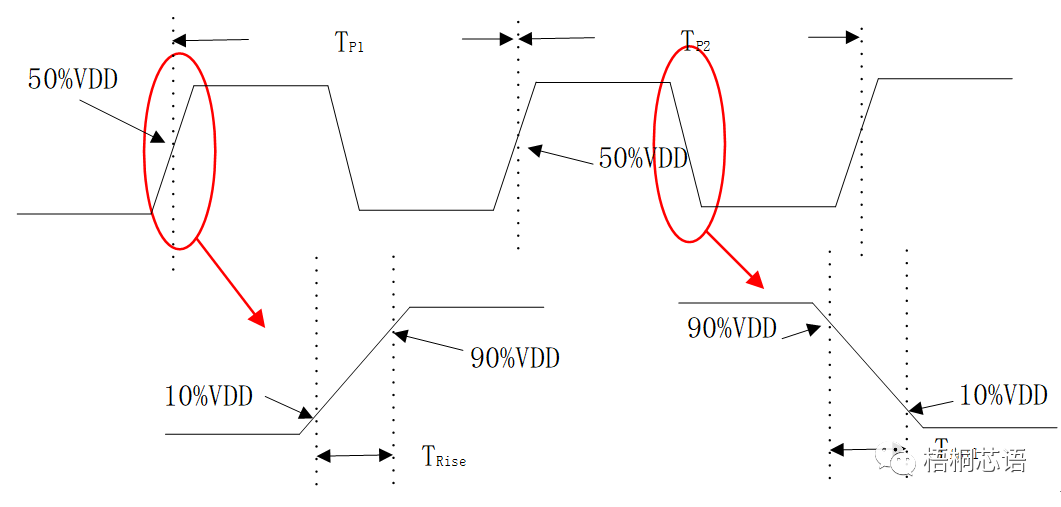

這里所說的時鐘,是一種規(guī)律性的邏輯電平信號,每隔一個固定周期,就會進(jìn)行一次電平的翻轉(zhuǎn)。如下圖所示:

一般說來,時鐘信號包含以下四個關(guān)鍵屬性:

- 周期(Period)/頻率(Frequency)

時鐘信號一次邏輯1和隨后一次邏輯0總共持續(xù)的時間,被稱之為該時鐘的時鐘周期(Clock Period),測量時一般是從某個上升沿50%VDD到下一個上升沿50%VDD之間的時間,如上圖中的TP1和TP2。而周期的倒數(shù),則稱之為該時鐘工作頻率(Clock Frequency)。

比如說,一個時鐘信號的時鐘周期如果是1ns,則其工作頻率就是1/1ns=1GHz。 - Duty Cycle

在一個時鐘周期內(nèi),該時鐘信號電平信號保持為邏輯1的時間,占用整個時鐘周期的比例。比如說,一個時鐘信號的時鐘周期是1ns,而邏輯1的持續(xù)時間是0.3ns,則該時鐘信號的duty cycle為0.3/1=30%。

一般來說,我們希望使用的時鐘,是一個duty cycle為50%的驅(qū)動信號。原因是如果使用該時鐘的反相時鐘,則其反相時鐘的duty cycle仍然能保持50%,這在電路設(shè)計(jì)或時序收斂時,會更容易實(shí)現(xiàn),電路設(shè)計(jì)的工作頻率也更容易提高。 - 時鐘抖動(Jitter)

時鐘抖動,Jitter,有2種概念:

一種是相鄰周期時鐘抖動,即相鄰2個周期的時鐘周期差值。以上圖所示,即為,這種差值主要會影響時序分析中setup timing的計(jì)算,需要添加在時鐘路徑上。

另一種是時鐘源最大抖動,即某時鐘產(chǎn)生源,比如說晶體振蕩器(Oscillator)、鎖相環(huán)(PLL、DLL)等,在不同工作環(huán)境(如溫度、電壓、濕度、負(fù)載等)、不同生產(chǎn)批次(生產(chǎn)工藝偏差),同一個配置條件下,可能產(chǎn)生的最大時鐘周期與最小時鐘周期的差值。該數(shù)值主要用于評估時鐘產(chǎn)生源的質(zhì)量。 - 變換時間(Transition Time)

字面理解transition time即時鐘變換時間,可以理解為時鐘上升或下降需要的時間,這與其他邏輯信號中transition time是一個概念。如圖中所示TRise以及TFall,分別表示時鐘信號的上升時間和下降時間。一般工程上認(rèn)定的測量方式,是10%VDD與90%VDD之間的變換時間。實(shí)際在標(biāo)準(zhǔn)單元庫的時序建模時,一部分測量點(diǎn)使用了30%VDD和70%VDD并進(jìn)行數(shù)學(xué)延展,可以參考標(biāo)準(zhǔn)單元庫的使用說明文件來進(jìn)一步理解。

與普通邏輯信號的transition time相比,為了更好的控制時鐘質(zhì)量,需要盡可能減小其數(shù)值,以減小對setup或hold時序違背的影響。其次在設(shè)計(jì)時鐘驅(qū)動電路時,需要盡可能的平衡輸出端PMOS和NMOS的驅(qū)動能力,已獲得相當(dāng)?shù)纳仙睾拖陆笛刈儞Q時間,由此提高驅(qū)動電路輸出信號的噪聲容限。

在RTL設(shè)計(jì)當(dāng)中,只要是驅(qū)動時序邏輯元件(如寄存器、鎖存器)時鐘輸入端的信號,都會被默認(rèn)為時鐘信號。如下圖所示,流經(jīng)S-D1和S-D2兩段路徑的信號都會被看做時鐘信號,

而針對驅(qū)動每一個時序邏輯元件的時鐘輸入端,則額外存在以下2個關(guān)鍵屬性:

- 時鐘延時(Clock Latency)

時鐘延時,即從時鐘源到達(dá)該元件時鐘驅(qū)動端的延時。如T1與T2,會因?yàn)榻?jīng)過不同的邏輯,到達(dá)所需驅(qū)動時序元件的延時有所不同。控制T1和T2以及同樣從S端到達(dá)其他寄存器延時盡量相同,叫做時鐘樹平衡(Clock Tree Balance),是時序收斂的重要手段。

- 時鐘延時差(Clock Skew)

可以看出,從同一個時鐘源,到達(dá)不同元件的時鐘驅(qū)動端,都會有所不同。則T1與T2的差值,就可以看成兩個寄存器的時鐘延時差,即Clock Skew,當(dāng)然對于從S端到達(dá)所有需要驅(qū)動的寄存器,時鐘延時最大值與最小值只差,就是這顆時鐘樹的Clock Skew。

剛才說了,為了做時鐘樹平衡,需要盡量減少Clock Skew,不過,在具體工程時,可能會因?yàn)楣脑O(shè)計(jì)、特殊路徑優(yōu)化等的需要,在時鐘樹上,為某些特定的葉部(對于時鐘樹來說,把源頭看成根部root,則每一個時序邏輯終點(diǎn)叫做葉部,即leaf)增加Latency,以加大clock skew。

電平信號與脈沖信號

RTL的設(shè)計(jì)是建立在同步電路基礎(chǔ)上的,因此寄存器與寄存器之間的通訊,都是通過時鐘作為同步信號來實(shí)現(xiàn)的。這里所說的電平信號,一般指信號寬度大于等于2個時鐘周期的數(shù)據(jù)。而脈沖信號,這里指只有1個時鐘周期信號寬度的數(shù)據(jù)。

而對于遠(yuǎn)遠(yuǎn)小于1個時鐘周期信號寬度的數(shù)據(jù),行業(yè)內(nèi)多數(shù)稱之為毛刺,是不可靠的數(shù)據(jù)。

-

寄存器

+關(guān)注

關(guān)注

31文章

5437瀏覽量

124701 -

數(shù)字信號

+關(guān)注

關(guān)注

2文章

998瀏覽量

48389 -

RTL

+關(guān)注

關(guān)注

1文章

390瀏覽量

61190 -

VDD

+關(guān)注

關(guān)注

1文章

316瀏覽量

35305 -

PLL電路

+關(guān)注

關(guān)注

0文章

92瀏覽量

6823

發(fā)布評論請先 登錄

數(shù)字信號處理實(shí)踐方法——EC.Ifeachor著,羅鵬飛等譯

數(shù)字信號的糾錯原因及解決方法

集成電路設(shè)計(jì)方法學(xué)概論

數(shù)字信號處理實(shí)踐方法.part1

數(shù)字信號處理的PDF電子書免費(fèi)下載

數(shù)字信號全相位譜分析與濾波技術(shù)的PDF電子書免費(fèi)下載

評論