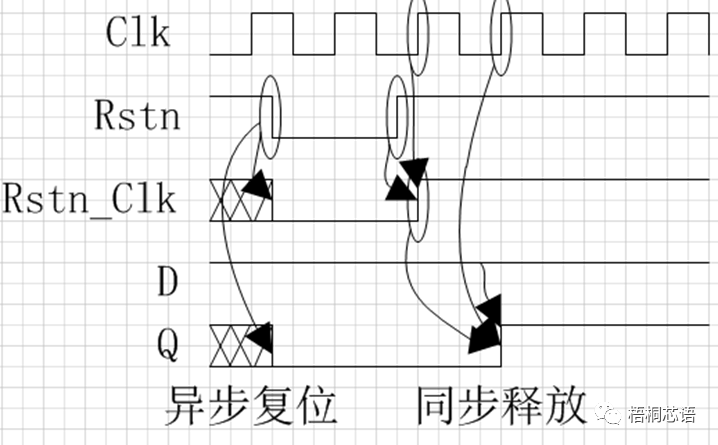

異步復位

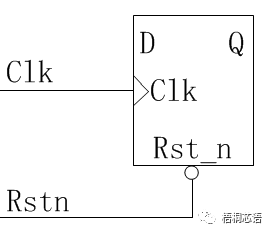

在前面的文章中有過對于寄存器行為的描述,而復位方面,在電路設計時建議使用帶異步復位/置位的寄存器。原因是只要復位信號有效,則無論時鐘是否到來,都會對寄存器進行復位,使電路處于一個穩定的狀態。而復位信號釋放后,需要等時鐘到來,才會更新數據。

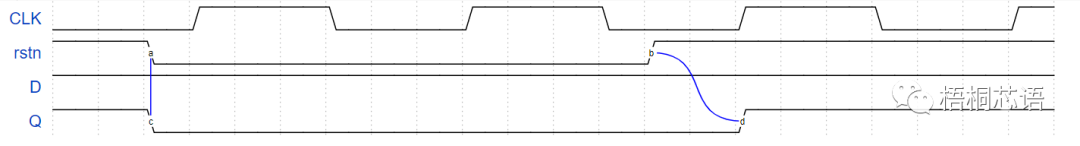

當異步復位有效時,無論有沒有時鐘,寄存器都會處于復位狀態,也會穩定輸出,因此沒有過于擔心的問題。但如果復位信號釋放,而此時D端數據與Q端數據不一致,那么當寄存器時鐘有效時,就會更新Q端數據。由此也會出現一個時序的要求,也就是recovery/remove timing的時序要求。

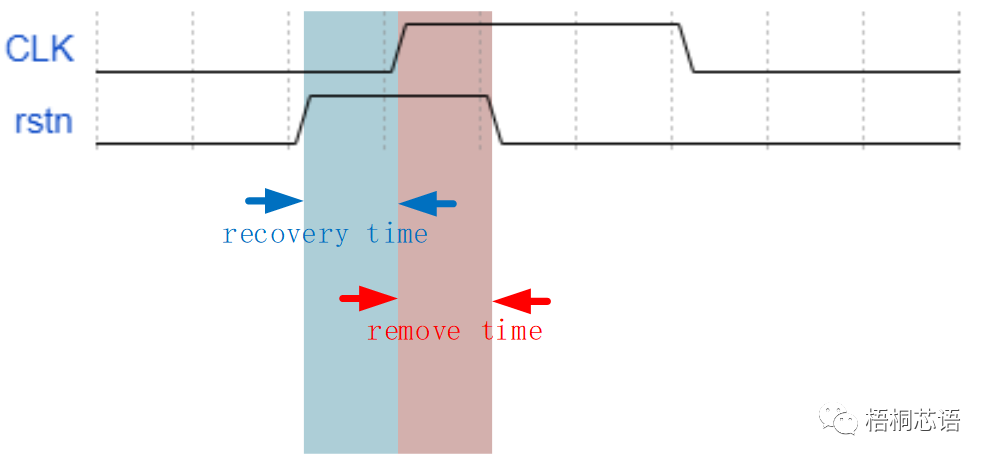

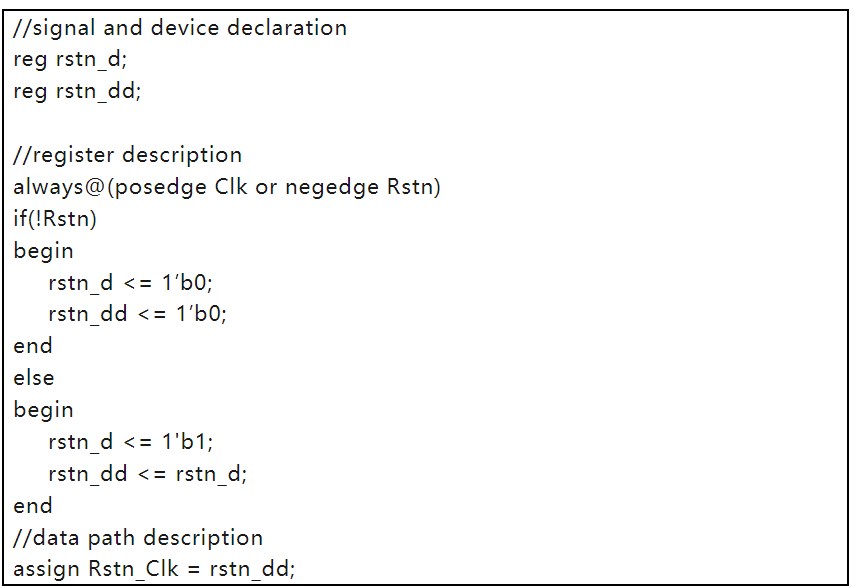

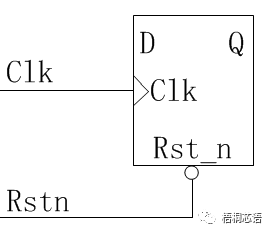

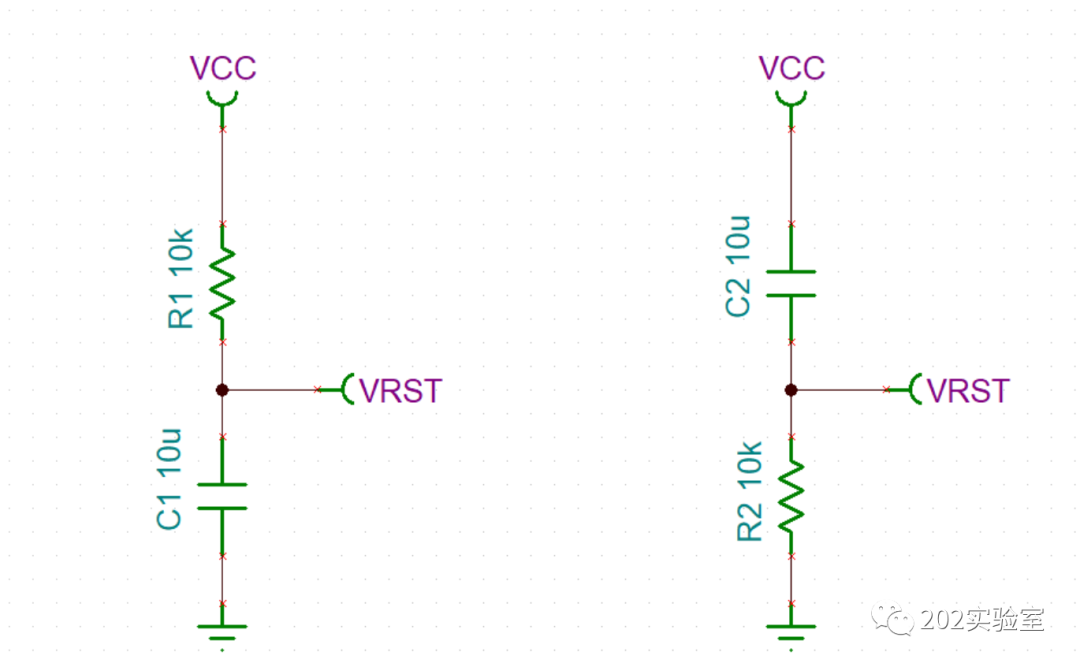

為了確保復位信號的使用沒有問題,一般采用以下電路來實現異步復位信號釋放時與時鐘的同步處理,以便讓EDA工具自動識別時序路徑,進行時序分析及時序優化。

這樣操作,我們稱為異步復位同步釋放。可以最大限度保證時序的穩定性。

以上RCU框圖中的電路,,用Verilog HDL描述如下所示:

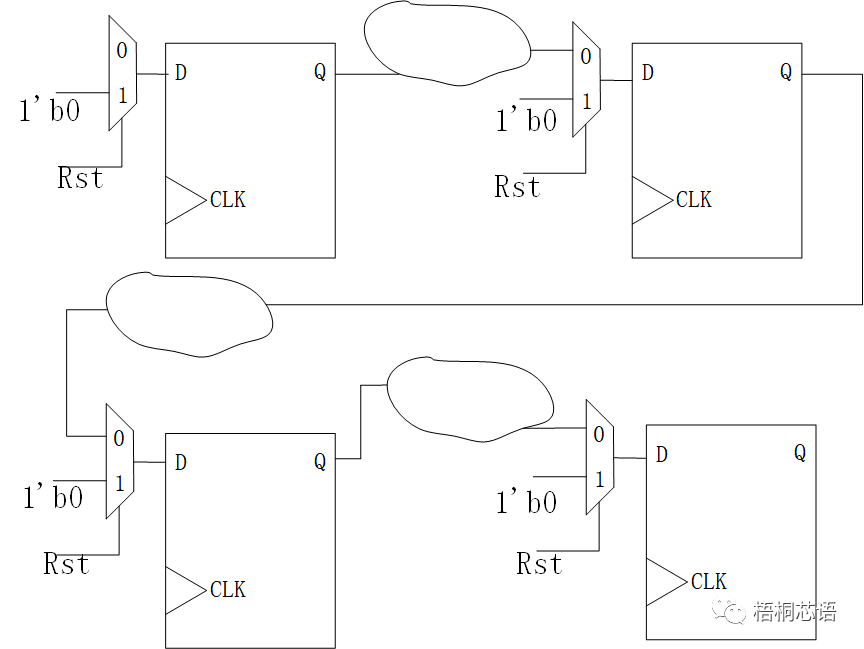

同步復位

有些早期的電路,在設計時使用了同步復位,而沒有使用異步復位來進行模塊級復位管理。原因是早期的EDA工具對復位信號的處理還不是很好,需要像時鐘一樣做復位樹來進行時序平衡(當時還沒有recovery/remove的時序概念),這是為了確保復位的穩定性所作出的犧牲。

如上圖所示,同步復位Rst實際上就是DFF的一個輸入,所以在時序上直接可以被看做數據路徑來處理,這對于早起的EDA工具來說,是比較友好。

但是我們需要看到一個問題,那就是所有的寄存器在上電時,輸出都是不可知的結果。因此需要等待時鐘有效后,才能確保電路的穩定復位完成,接著再釋放復位信號。在當今復雜的SoC系統中,PLL或者片內晶體振蕩器何時穩定輸出,且輸出波形正常,是需要一定的管理電路。用不穩定來管理不穩定,是不可行的。

因此對于同步復位的早期遺留電路來說,在外圍做好復位管理,確保上電后,其輸出不會影響整個系統,也是可以的。

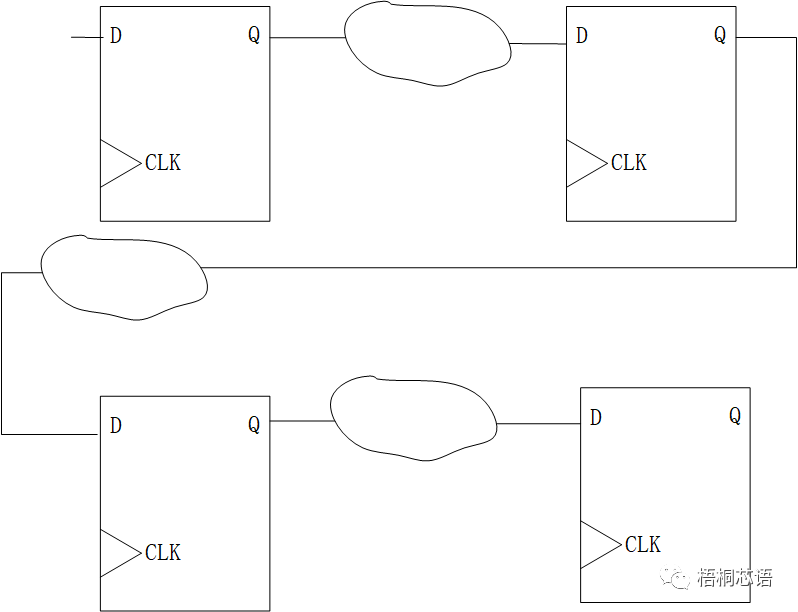

沒有復位

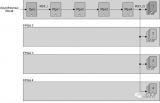

有時候,過于在意面積的電路中,會使用沒有復位的寄存器來實現電路。如下圖所示。

這種情況比較極端,確實寄存器的面積是比較大的,如果減少復位電路,勢必有較大的面積收益(20%左右)。但這就需要在設計的時候考慮好每個寄存器復位值是多少。然后通過輸入,以及一定次數的時鐘傳遞,將電路穩定復位。

比如說上面這幅圖,第四級寄存器,上電后是個未知輸出,需要4個時鐘周期,才能穩定到初態。

這樣的電路如果比較大,則上電后復位的時間會比較久,少則幾十個時鐘周期,多則上百上千個時鐘周期。而且如果有部分寄存器需要特定初始值,還需要專門送進去(可以參考同步復位的操作)。

混用復位

以上三種電路復位的方式,可以混用,在節省面積、穩定復位以及早期遺留電路集成上,會有一些幫助。但還是建議能用異步復位就用異步復位吧。

-

寄存器

+關注

關注

31文章

5336瀏覽量

120232 -

EDA工具

+關注

關注

4文章

267瀏覽量

31787 -

晶體振蕩器

+關注

關注

9文章

617瀏覽量

29106 -

異步復位

+關注

關注

0文章

47瀏覽量

13312 -

rcu

+關注

關注

0文章

21瀏覽量

5446

發布評論請先 登錄

相關推薦

復位信號是什么意思?復位信號的作用?詳解Xilinx FPGA復位信號那些事

FPGA設計中層次結構設計和復位策略影響著FPGA的時序

淺析FPGA中異步復位同步釋放的原理

【PUC、POR】MSP430的復位信號

淺析復位信號的設計和時序

淺析復位信號的設計和時序

評論