電子發燒友網報道(文/周凱揚)在半導體設計領域,IP公司擁有的各大優秀IP除了要經過客戶的驗證外,其實還有不少認證工作需要完成。比如在汽車領域,往往就需要通過ISO 26262的功能安全認證。而對于是否能經過生產制造認證,晶圓廠也準備了自己的一套標準或認證計劃,比如臺積電的TSMC9000計劃。

臺積電的IP認證

臺積電從很早就開始和IP廠商達成合作,成立了臺積電開放創新平臺(OIP),該平臺的關鍵組成之一就是IP聯盟和TSMC9000 IP認證計劃。該聯盟將為半導體業界提供最大的流片生產認證且臺積電專用的IP。IP聯盟的成員會分配單獨的客戶經理,不僅可以訪問臺積電的技術數據用于設計IP,還可以獲得臺積電技術支持團隊的專門支持。

至于早在2000年就開啟的TSMC9000 IP認證計劃,則是臺積電為IP質量下限設定的一系列要求。IP合作伙伴必須提供數據,隨后申請為其IP進行TSMC9000評估。評估項目包括DRC/LVS、數據一致性檢驗、ESD耐受性驗證、設計余量驗證等。

評估結果也會發布到TSMC的在線數據庫,幫助客戶對這一IP的可用性和風險性有一個了解。除了IP本身的質量外,TSMC9000還有額外的系統層級測試驗證項目,從而確保整體的設計體驗,且針對車規設計,臺積電也準備了專門的TSMC9000A認證。

龐大的IP陣容

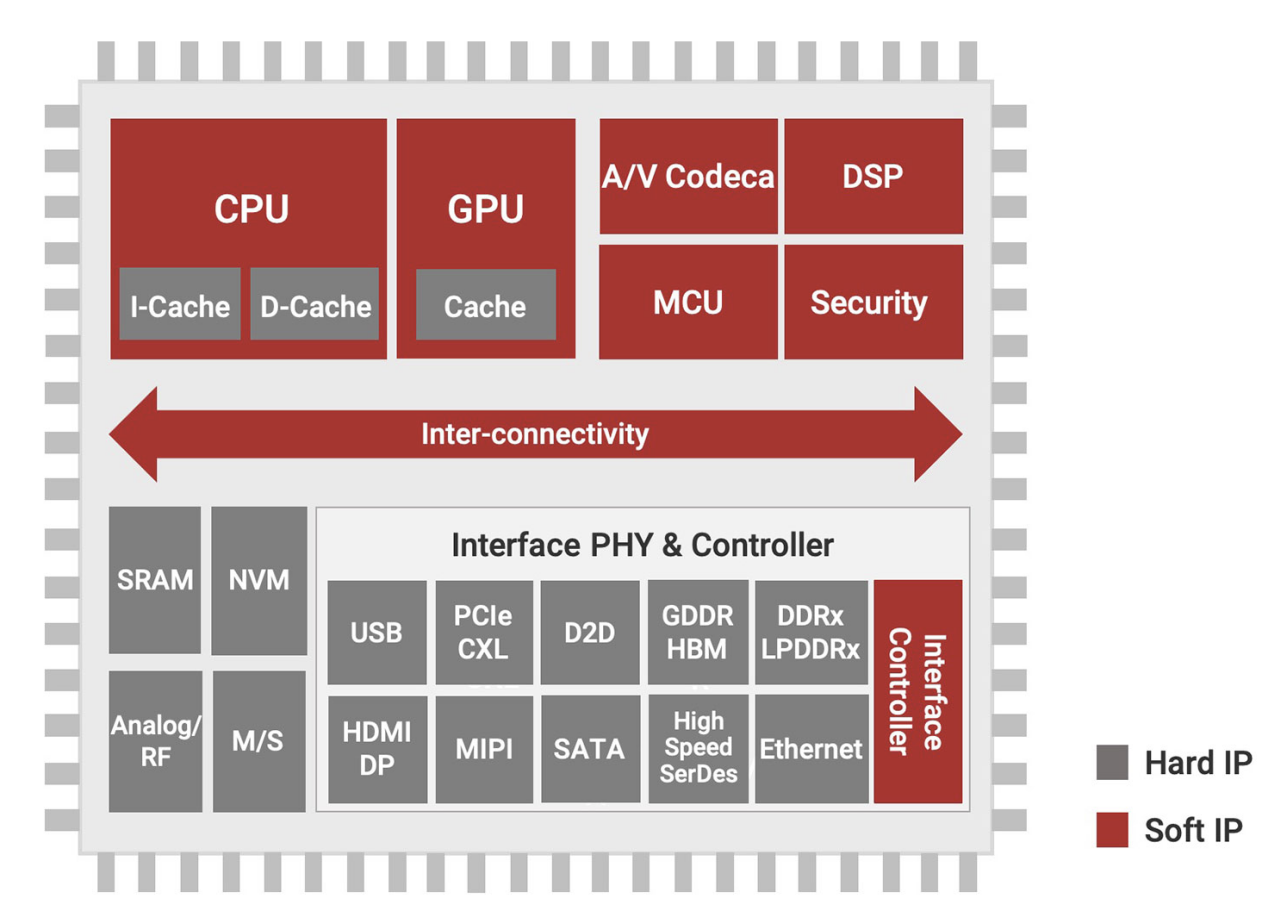

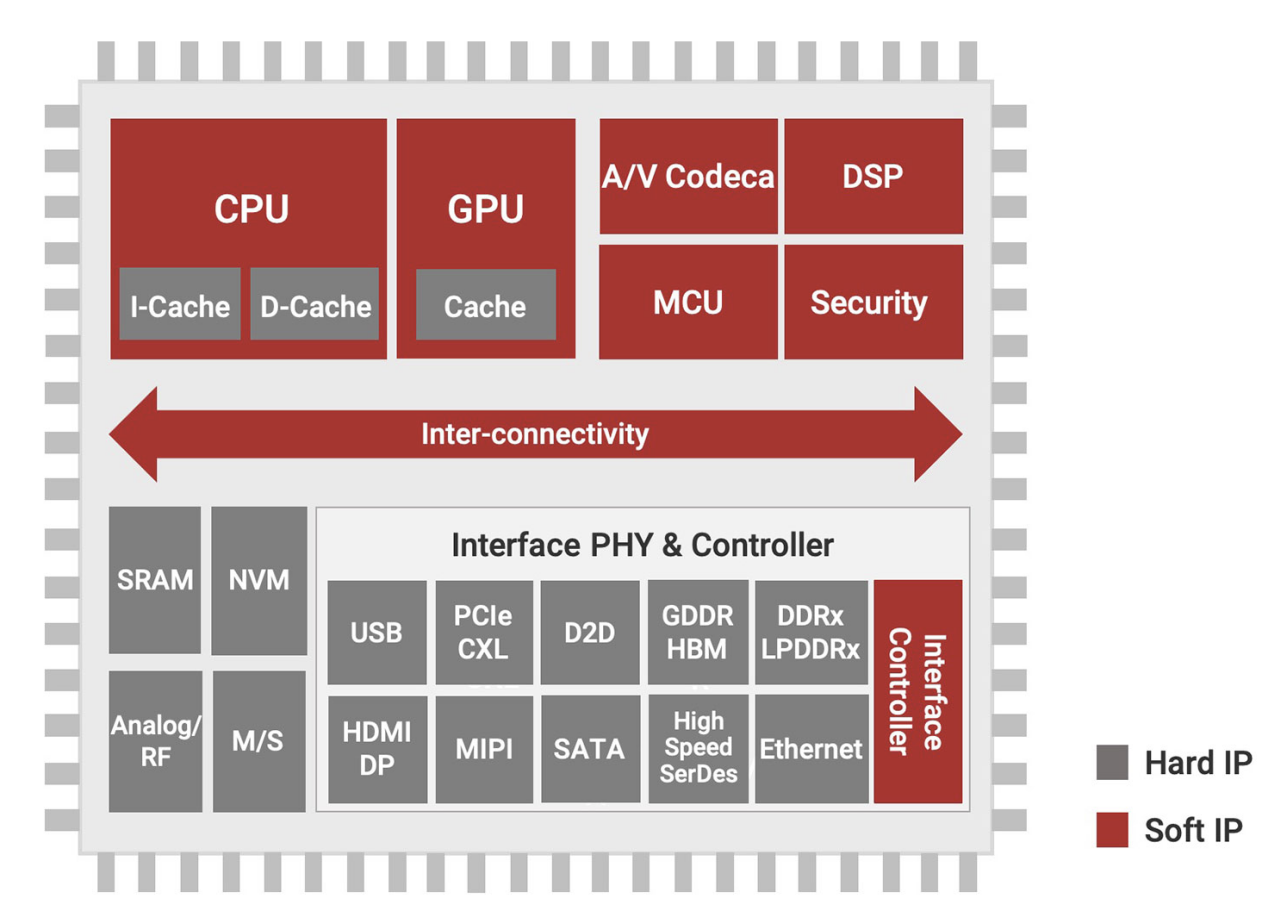

如今的TSMC9000在多年發展下來,已經擁有了極度完備的IP支持陣容。臺積電也對這些IP做好了細致的分類,既有CPU、GPU、編解碼器、DSP、MCU和互聯之類的軟IP,也有SRAM、HDMI、USB、以太網之類的硬IP。

現代SoC設計中的軟硬IP劃分 / 臺積電

不少IP廠商將新IP正式投入商用供應時,往往都會先通過TSMC9000認證,然后公開這一消息,從而給到客戶一個側面的質量保證承諾。同時,臺積電每年都會頒發年度IP合作伙伴獎,是否獲得TSMC9000認證也是評選因素之一,此外還有客戶反饋、流片次數、晶圓量和客戶支持等。

就拿新思、Cadence等廠商來說,作為臺積電的主要OIP合作伙伴,都會在TSMC9000上下大功夫,比如新思的DesignWare PVT、Cadence的Tensilica DSP IP等,都會針對臺積電的最新工藝進行優化,從而通過TSMC9000的認證。

寫在最后

可以看出,使得臺積電成為芯片設計公司首選晶圓代工廠的原因,不僅僅只有其先進的制造工藝,還有它那成熟的OIP合作伙伴生態。早在2013年,就有39家廠商共9500個IP對臺積電的各大工藝節點提供了支持,如今這個數量更是增加到了40多個IP廠商和49000多個IP,致使如今的廠商在開發新的IP時,也是優先考慮在臺積電工藝節點上的流片可行性。在這樣的IP合作生態和驗證計劃下,設計公司在選取IP時進行系統設計和制造上,也會更加放心。

臺積電的IP認證

臺積電從很早就開始和IP廠商達成合作,成立了臺積電開放創新平臺(OIP),該平臺的關鍵組成之一就是IP聯盟和TSMC9000 IP認證計劃。該聯盟將為半導體業界提供最大的流片生產認證且臺積電專用的IP。IP聯盟的成員會分配單獨的客戶經理,不僅可以訪問臺積電的技術數據用于設計IP,還可以獲得臺積電技術支持團隊的專門支持。

至于早在2000年就開啟的TSMC9000 IP認證計劃,則是臺積電為IP質量下限設定的一系列要求。IP合作伙伴必須提供數據,隨后申請為其IP進行TSMC9000評估。評估項目包括DRC/LVS、數據一致性檢驗、ESD耐受性驗證、設計余量驗證等。

評估結果也會發布到TSMC的在線數據庫,幫助客戶對這一IP的可用性和風險性有一個了解。除了IP本身的質量外,TSMC9000還有額外的系統層級測試驗證項目,從而確保整體的設計體驗,且針對車規設計,臺積電也準備了專門的TSMC9000A認證。

龐大的IP陣容

如今的TSMC9000在多年發展下來,已經擁有了極度完備的IP支持陣容。臺積電也對這些IP做好了細致的分類,既有CPU、GPU、編解碼器、DSP、MCU和互聯之類的軟IP,也有SRAM、HDMI、USB、以太網之類的硬IP。

現代SoC設計中的軟硬IP劃分 / 臺積電

不少IP廠商將新IP正式投入商用供應時,往往都會先通過TSMC9000認證,然后公開這一消息,從而給到客戶一個側面的質量保證承諾。同時,臺積電每年都會頒發年度IP合作伙伴獎,是否獲得TSMC9000認證也是評選因素之一,此外還有客戶反饋、流片次數、晶圓量和客戶支持等。

就拿新思、Cadence等廠商來說,作為臺積電的主要OIP合作伙伴,都會在TSMC9000上下大功夫,比如新思的DesignWare PVT、Cadence的Tensilica DSP IP等,都會針對臺積電的最新工藝進行優化,從而通過TSMC9000的認證。

寫在最后

可以看出,使得臺積電成為芯片設計公司首選晶圓代工廠的原因,不僅僅只有其先進的制造工藝,還有它那成熟的OIP合作伙伴生態。早在2013年,就有39家廠商共9500個IP對臺積電的各大工藝節點提供了支持,如今這個數量更是增加到了40多個IP廠商和49000多個IP,致使如今的廠商在開發新的IP時,也是優先考慮在臺積電工藝節點上的流片可行性。在這樣的IP合作生態和驗證計劃下,設計公司在選取IP時進行系統設計和制造上,也會更加放心。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

臺積電

+關注

關注

44文章

5632瀏覽量

166423

發布評論請先 登錄

相關推薦

OpenAI攜手博通、臺積電打造內部芯片

近日,據消息人士透露,OpenAI正在與博通和臺積電展開合作,共同研發其首款內部芯片,旨在為其人工智能系統提供更強大的支持。 為應對基礎設施需求的激增,OpenAI在芯片供應方面采取了

OpenAI攜手博通臺積電打造自主芯片

OpenAI正在與博通和臺積電兩大半導體巨頭攜手合作,共同打造其首款自主研發的“in-house”芯片,旨在為其人工智能系統提供更強大的算力

M31円星科技連續七年獲頒「臺積電OIP硅智財伙伴獎」,並發表ONFI5.1 I/O IP于臺積電5奈米制程成功完成硅驗證

M31的ONFI5.1 I/O IP在數據傳輸速度上的效能尤為突出,藉由臺積電5奈米制程技術,該IP成功達到了3600MT/s的傳輸速率,已

Alphawave推出業界首款支持臺積電CoWoS封裝的3nm UCIe IP

的3nm Die-to-Die(D2D)多協議子系統IP。這一里程碑式的成果不僅標志著半導體互連技術的又一次飛躍,還通過深度融合臺積電的Chip-on-Wafer-on-Substra

SK集團與臺積電加強AI芯片合作

韓國SK集團與全球領先的半導體制造商臺積電近日宣布加強在人工智能(AI)芯片領域的合作。據SK集團官方消息,集團會長崔泰源于6月6日親自會見了臺

新思科技與臺積公司深化EDA與IP合作

新思科技近日與臺積公司宣布,在先進工藝節點設計領域開展了廣泛的EDA和IP合作。雙方的合作成果已經成功應用于一系列人工智能、高性能計算和移動

Cadence與臺積電深化合作創新,以推動系統和半導體設計轉型

楷登電子(美國 Cadence 公司,NASDAQ:CDNS)與臺積電(TSMC)深化了雙方的長期合作,官宣了一系列旨在加速設計的創新技術進展,包括從 3D-IC 和先進制程節點到設計

Marvell將與臺積電合作2nm 以構建模塊和基礎IP

Marvell將與臺積電合作2nm 以構建模塊和基礎IP 張忠謀于1987年成立的臺灣積體電路制

十年新增四萬個IP,臺積電打造的IP合作生態

十年新增四萬個IP,臺積電打造的IP合作生態

評論