SEMulator3D將在半導體器件設計和制造中發揮重要作用

作者:泛林集團 Semiverse Solutions 部門 SEMulator3D?應用工程總監Benjamin Vincent

動態隨機存取存儲器 (DRAM) 是一種集成電路,目前廣泛應用于需要低成本和高容量內存的數字電子設備,如現代計算機、顯卡、便攜式設備和游戲機。

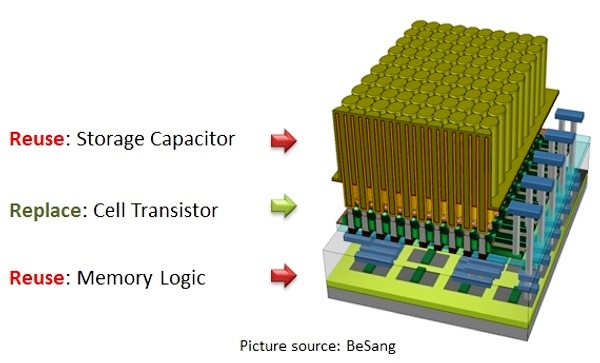

技術進步驅動了DRAM的微縮,隨著技術在節點間迭代,芯片整體面積不斷縮小。DRAM也緊隨NAND的步伐,向三維發展,以提高單位面積的存儲單元數量。(NAND指“NOT AND”,意為進行與非邏輯運算的電路單元。)

l 這一趨勢有利于整個行業的發展,因為它能推動存儲器技術的突破,而且每平方微米存儲單元數量的增加意味著生產成本的降低。

l DRAM技術的不斷微縮正推動向使用水平電容器堆疊的三維器件結構的發展。

行業由2D DRAM發展到3D DRAM預計需要多長時間?以目前的技術能力來看,需要5到8年。與半導體行業的許多進步一樣,下一階段始于計劃。或者說,在DRAM領域,下一階段始于架構。

泛林集團正在使用SEMulator3D?計算機仿真軟件構想3D DRAM的架構,來探索DRAM的未來。SEMulator3D?計算機仿真軟件通常通過模擬實際晶圓制造的過程來虛擬加工半導體器件。以下是我們對3D DRAM架構的設想,涉及六個方面:

l 微縮問題

l 堆疊挑戰

l 面積縮小

l 創新連接

l 通孔陣列

l 工藝要求

微縮問題

DRAM單元電路由一個晶體管和一個電容器組成。晶體管負責傳輸電流,使信息(位)能夠被寫入或讀取,而電容器則用于存儲位。

DRAM結構由被稱為“位線(BL)”的導電材料/結構組成,位線提供注入晶體管的載流子(電流)。晶體管就像一個閘門,可以打開(接通)或關閉(斷開),以保持或停止電流在器件內的流動。這種柵極狀態由施加在被稱為“字線(WL)”的接觸導電結構上的電壓偏置來定義。如果晶體管導通,電流將流過晶體管到達電容器,并存儲在電容器中。

電容器需要有較高的深寬比,這意味著它的高度遠大于寬度。在一些早期的DRAM中,電容器的有源區被嵌入到硅襯底中。在最近幾代DRAM中,電容器則是在晶體管頂部進行加工。

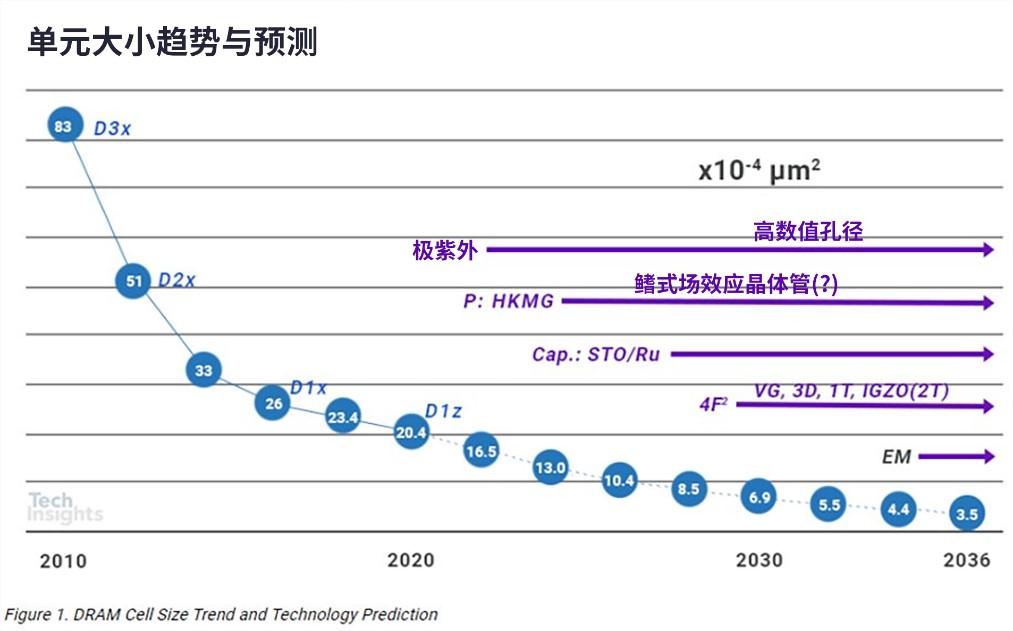

一個區域內可存儲的位數或者說單位存儲單元的平均面積對微縮至關重要。目前(見上圖D1z),每個存儲單元的面積約為20.4E-4μm2。很快,通過增高電容器減小面積以提高位密度(即進一步減小單位存儲單元面積)的方法將變得不可行,因為用于電容器制造的刻蝕和沉積工藝無法處理極端(高)的深寬比。

上圖顯示,半導體行業預計能夠在單位存儲單元面積達到約10.4E-4μm2前(也就是大約5年后)維持2D DRAM架構。之后,空間不足將成為問題,這很可能提升對垂直架構也就是3D DRAM的需求。

堆疊挑戰

為了推進DRAM微縮,很自然地需要將2D DRAM組件側放并堆疊起來。但這面臨幾個難題:

l 水平方向需要橫向刻蝕,但由于凹槽尺寸差異很大,橫向刻蝕非常困難。

l 在堆棧刻蝕和填充工藝中需要使用不同的材料,這給制造帶來了困難。

l 連接不同3D組件時存在集成難題。

最后,為了讓這一方案更具競爭力,需要縮短電容器(Cap)的長度(電容器的長度不能和高度一樣)并進行堆疊,以提升單位面積的存儲單元數量。

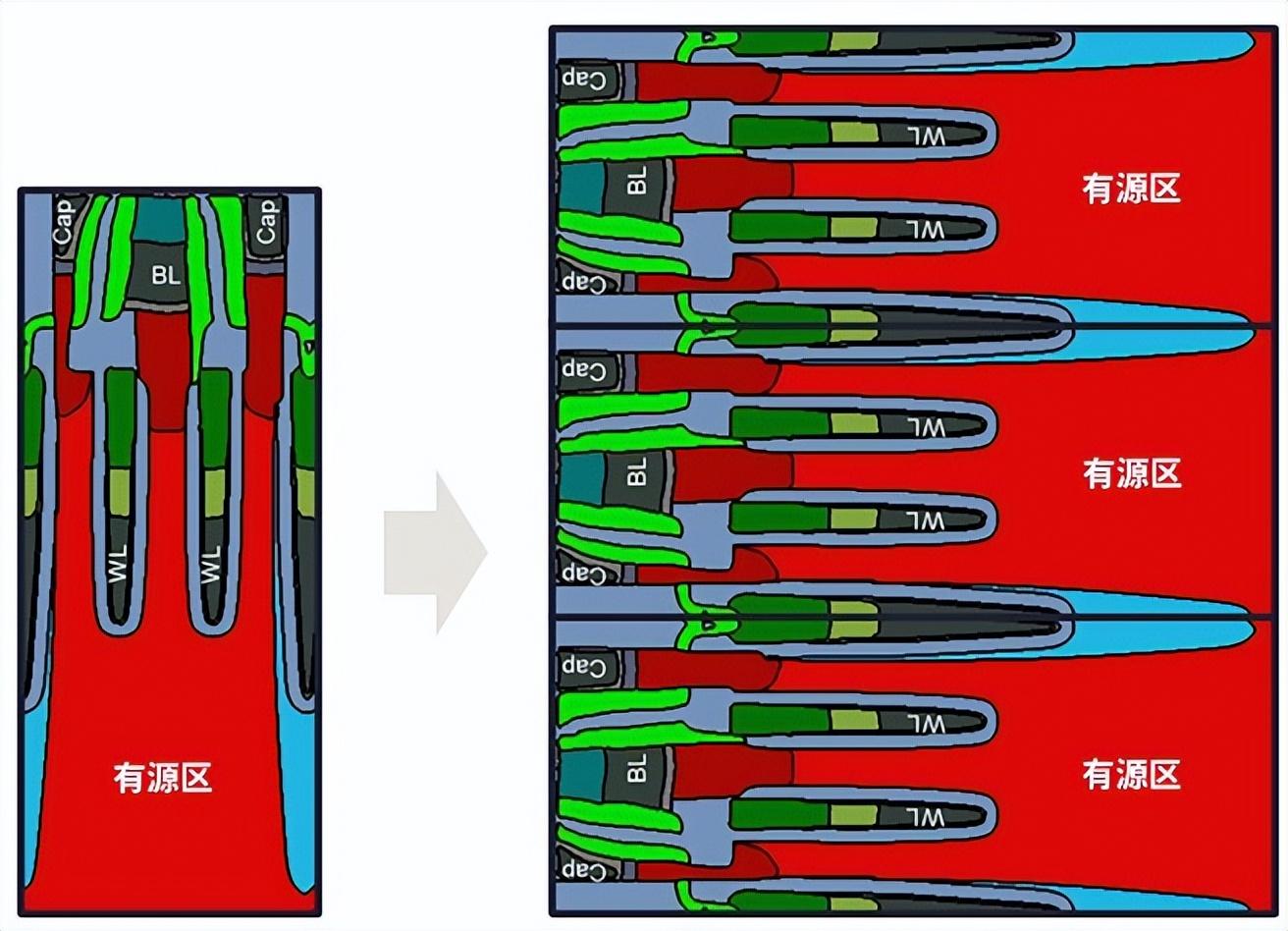

2D DRAM架構垂直定向視圖(左圖)。將其翻轉并將結構堆疊在一起(右圖)的做法不可行的主要原因是需要刻蝕橫向空腔,并將其以不同的橫向深度填充到硅有源區中。

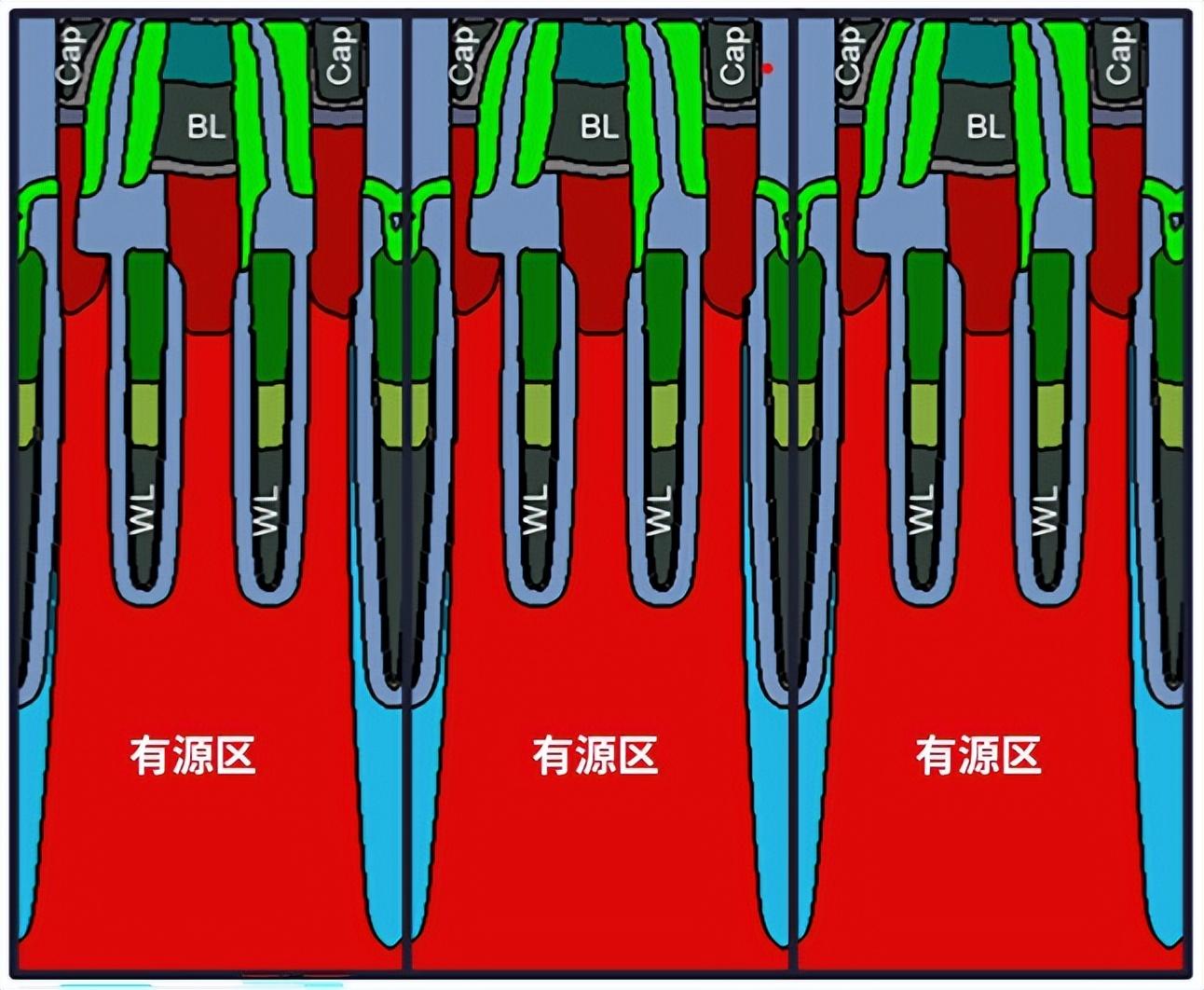

想象一下,上圖表示的結構不變,將其順時針旋轉90度,結構將處于自上而下的視圖中。在這個方向上,可以堆疊納米薄片。但同樣,這種情況下,原始設計顯示的區域非常密集,因此位線和電容器需要自上而下地進行工藝處理,并且距離很近。要實現這種方向的堆疊 (3D),需要重新設計架構。

重新構想的架構

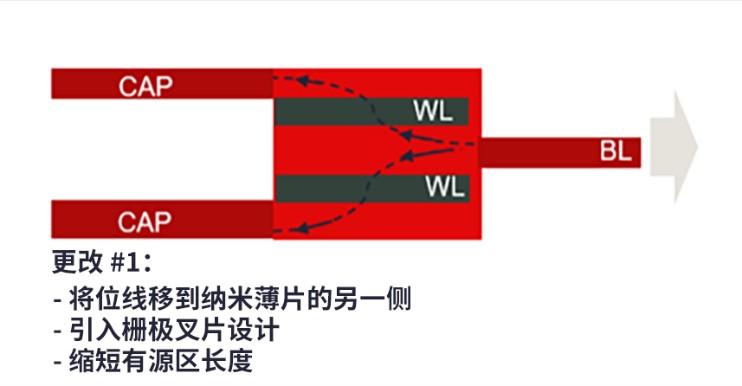

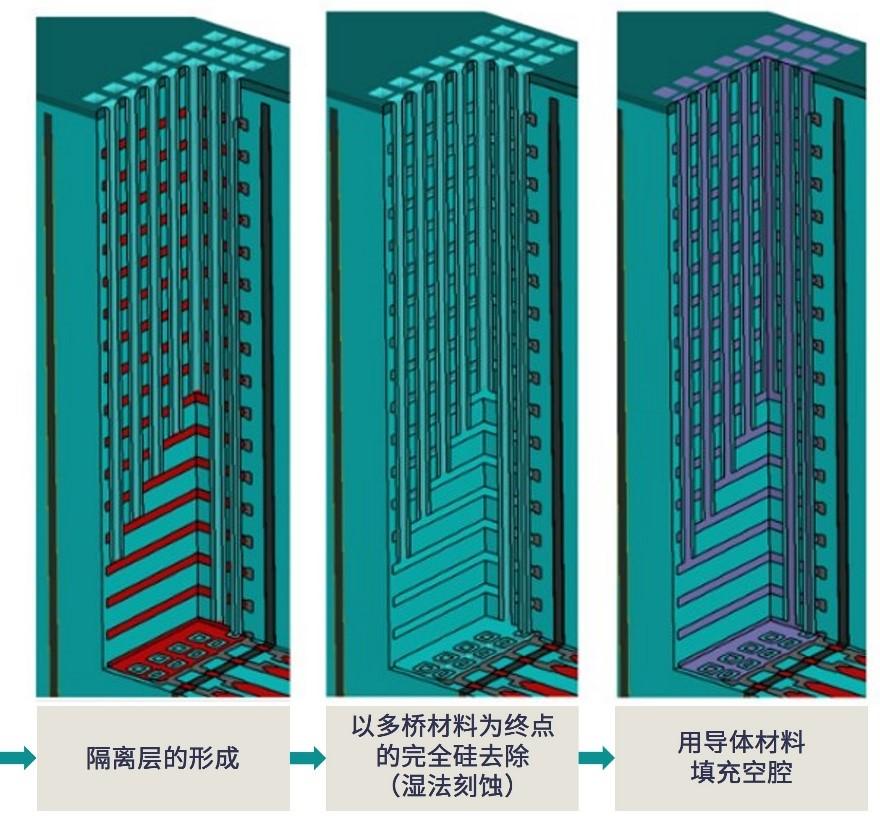

我們的團隊使用泛林集團SEMulator3D進行了幾處更改,在減小硅區域的同時為電容器的工藝處理提供更多空間,從而縮小納米薄片的面積。

首先,我們將位線移到了納米薄片的另一側,使電流通過晶體管柵極穿過整個納米薄片,這能夠從總體上增加電容器工藝處理的空間,并減小硅區域的面積。

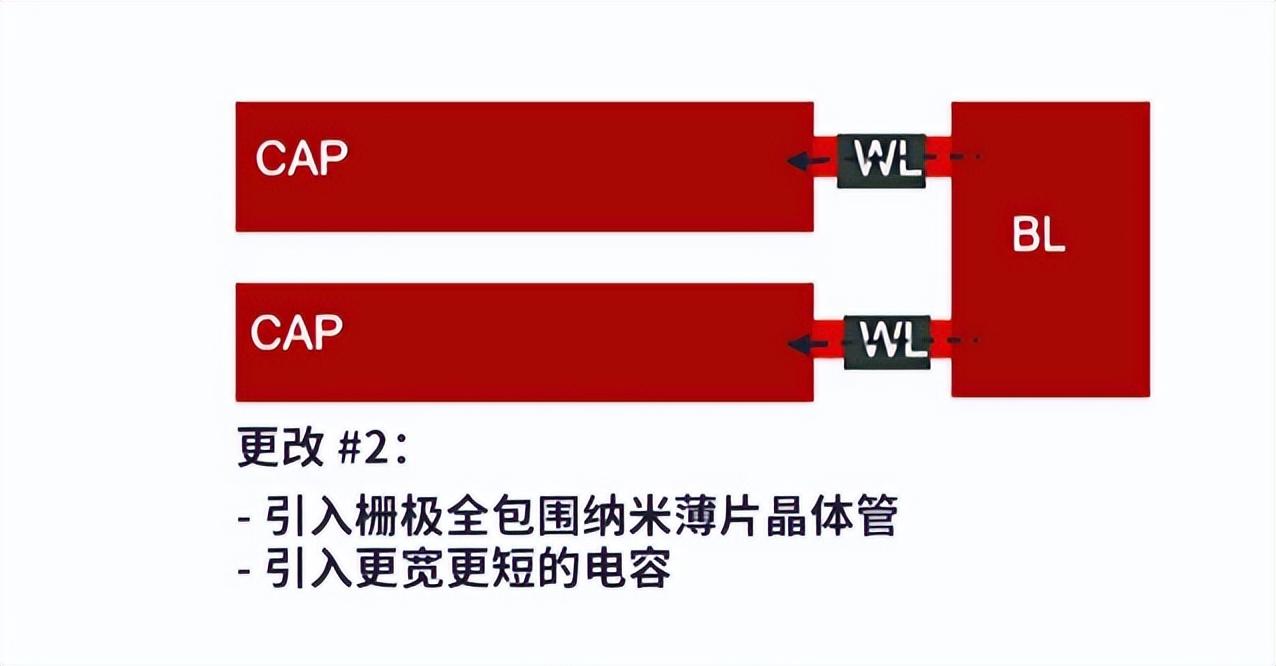

其次,我們引入柵極全包圍晶體管,以進一步縮小硅有源區。此外,我們還將曾經又窄又高的電容器變得又短又寬。之所以能夠做到這一點,是因為把位線移到架構的中心,從而獲得了更多空間。

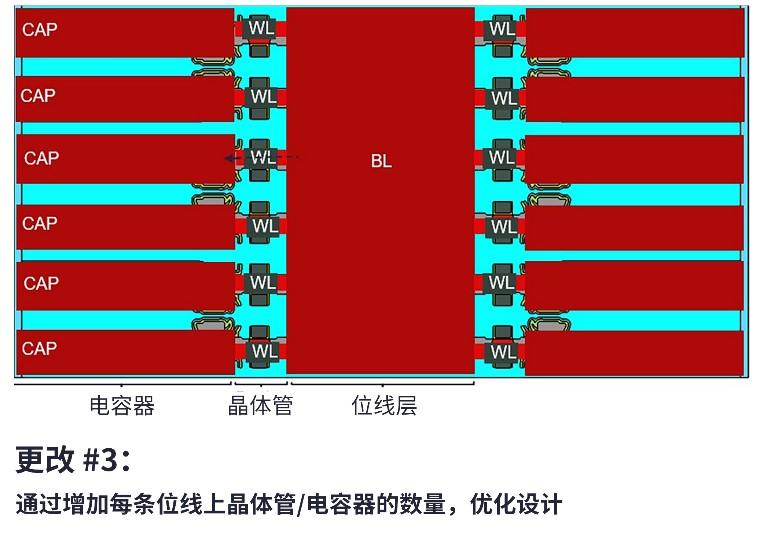

最后,我們通過在位線接觸點兩側放置晶體管/電容器的方式增加每個位線接觸點的晶體管/電容器數量(沒有理由將每條位線的晶體管數量限制在兩個以內)。之后,就可以堆疊這種重新配置(如上圖自上而下的視圖所示)的納米薄片了。

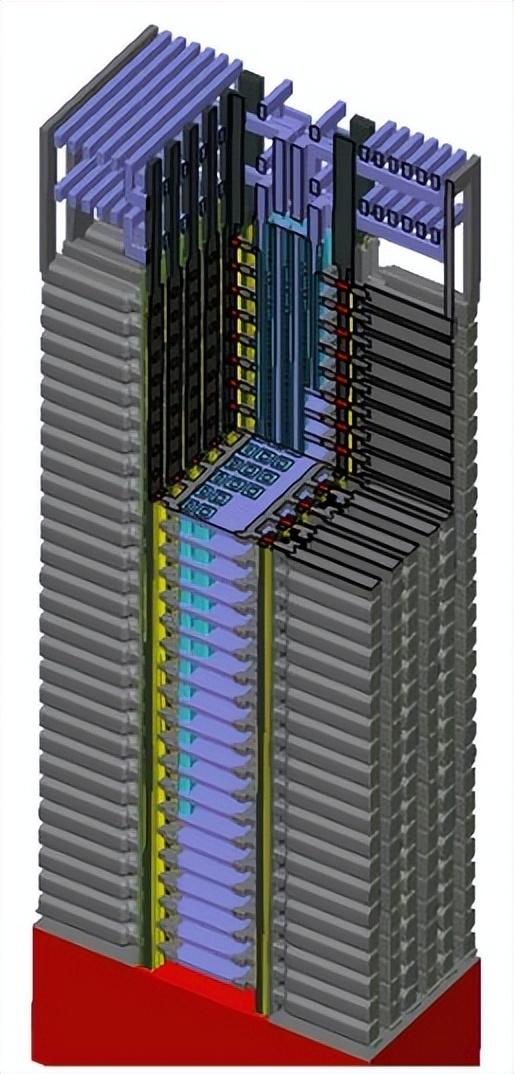

堆疊3D DRAM的第一次迭代有28層高(上圖),將比現在的D1z高兩個節點(單位存儲單元面積約13E-4μm2)。當然,層數越多,位數越多,密度也就越大。

創新連接

3D DRAM的新架構只是一個開始。除了配置之外,還必須就金屬化和連接性做出改變。

我們在設計中提出了幾種新的方法來促使電流通過中央的位線堆疊,包括連接各層的水平MIM(金屬-絕緣層-金屬)電容器陣列,以及將柵極包裹在硅晶體管周圍(柵極全包圍)。其原理是,當電流通過時,只有目標位線(層)被激活。在被激活的層中,電流可以連接到正確的晶體管。

28層3D納米薄片的關鍵組件包括:

l 一疊柵極全包圍納米薄片硅晶體管

l 兩排晶體管之間的位線層

l 24 個垂直字線

l 位線層和晶體管之間、晶體管和電容器之間的互連

l 水平MIM(金屬-絕緣層-金屬)電容器陣列

通孔陣列

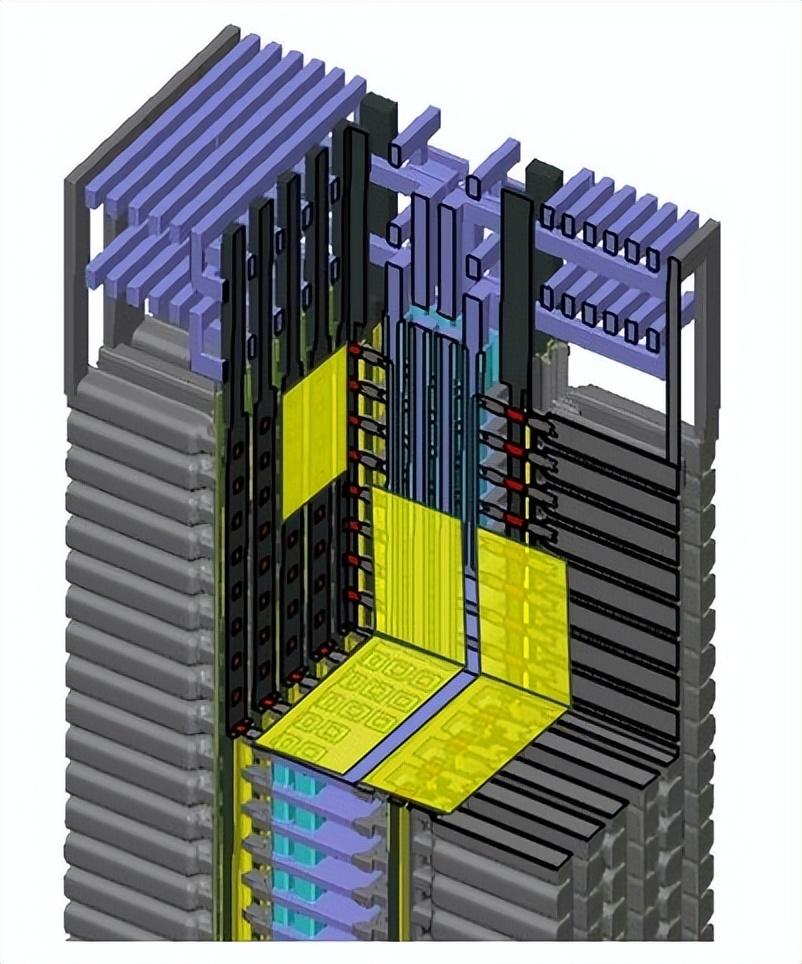

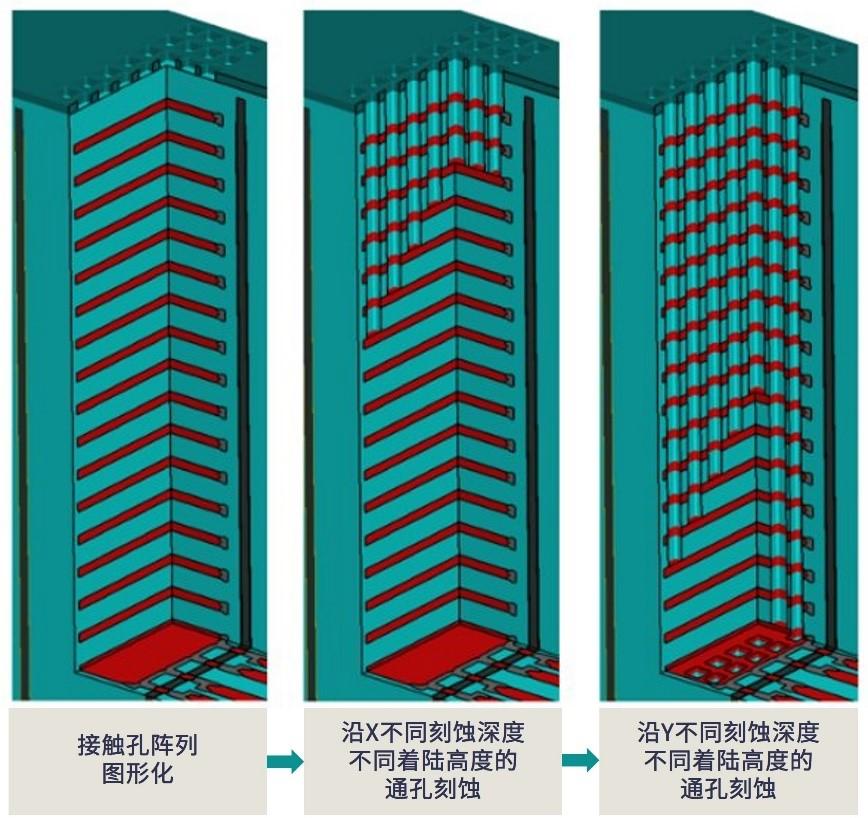

為了避免3D NAND中使用的臺階式結構的局限性,我們建議引入穿過硅堆棧層且可以在特定層停止(每層一個通孔)的通孔陣列結構,將接觸點置于存儲單元內部。溝槽制作完成后,我們引入只存在于側墻的隔離層。

高溝槽用于引入刻蝕介質以去除硅,然后在空溝槽中引入導電金屬。其結果是,頂部的每個方格(下面最后三張圖片中的淺綠色和紫色方框)只與下面的一層連接。

位線接觸圖形化

工藝要求

這一虛擬工藝中涉及到的幾個模塊需要獨特且創新的工藝。迄今為止,對于此類路徑的探索,變量都是通過物理測試發現和完善的。使用Semulator3D,我們可以實現對這些參數的虛擬優化調整。

我們的實驗使工藝要求方面對規格的要求非常嚴格。刻蝕和沉積專家可能會對我們的模型要求感到震驚:例如,在我們的架構中,需要刻蝕和填充關鍵尺寸為30nm、深度為2μm的溝槽。

3D DRAM是一種前沿設計,要求采用從未見過或嘗試過的工藝和設計,這是從概念走向原型的唯一途徑。我們可以進一步推進實驗,以了解不同晶圓之間的工藝差異。

未來趨勢

3D DRAM技術有望成為推動DRAM微縮的關鍵因素。單位存儲單元面積和電容器尺寸(長度)之間的適當平衡需要通過各種工藝/設計優化來確定,就如上述的這些方案。

通過虛擬加工新架構設計的原型,測試不同存儲密度下的不同DRAM設計方案,并為可以幫助制造未經測試器件技術的單位工藝提升規格要求,SEMulator3D可以在制造中發揮重要作用。

這項研究是未來技術評估的起點,有助于確定詳細的工藝和設備規格要求、可制造性和良率分析,并因此助力工藝可用性和變異性、技術性能以及面積和成本方面的分析。

審核編輯 黃宇

-

DRAM

+關注

關注

40文章

2311瀏覽量

183448 -

泛林集團

+關注

關注

0文章

58瀏覽量

11801

發布評論請先 登錄

相關推薦

為了延長DRAM存儲器壽命 必須短時間內采用3D DRAM

Sematech與合作伙伴聯手克服未來3D晶片技術挑戰

3D XPoint的原理解析 NAND和DRAM為什么拼不過它

關于3D超級DRAM技術簡單剖析

如何看待3D DRAM技術?

三星電子在硅谷設立下一代3D DRAM研發實驗室

三星2025年后將首家進入3D DRAM內存時代

三星電子:2025年步入3D DRAM時代

3D DRAM進入量產倒計時,3D DRAM開發路線圖

3D DRAM時代即將到來,泛林集團這樣構想3D DRAM的未來架構

3D DRAM時代即將到來,泛林集團這樣構想3D DRAM的未來架構

評論