前言

前面我們學(xué)習(xí)了8259A,但8259A 只適合單 CPU 的情況,為了充分挖掘 SMP 體系結(jié)構(gòu)的并行性,能夠把中斷傳遞給系統(tǒng)中的每個(gè) CPU 至關(guān)重要。基于此理由,Intel 引入了一種名為 I/O 高級(jí)可編程控制器的新組件,來(lái)替代老式的 8259A 可編程中斷控制器。下面一起來(lái)學(xué)習(xí)一下APIC。

0 APIC概述

Intel從Pentium處理器開(kāi)始引入了APIC(Advanced Programmable Interrupt Controller)機(jī)制,直譯為高級(jí)可編程中斷控制器。引入APIC機(jī)制是為了適應(yīng)multiple processor(MP,多處理器)環(huán)境。

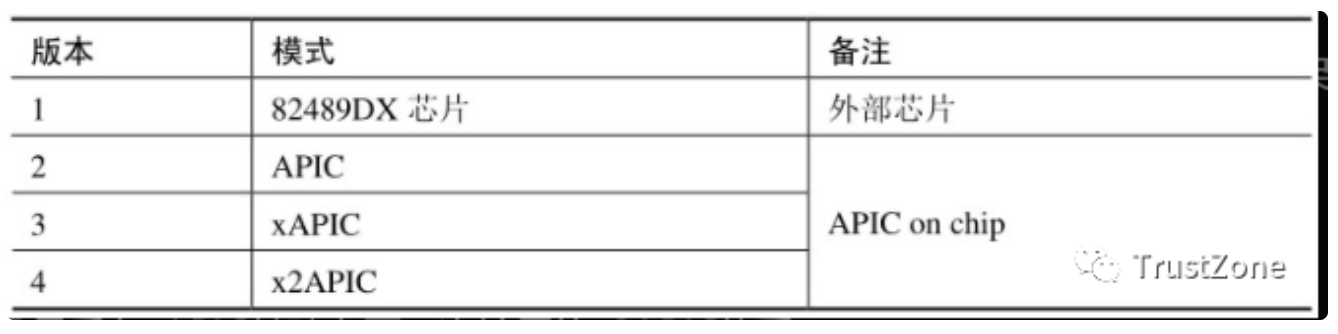

APIC經(jīng)歷了4個(gè)版本

最初的APIC屬于外部設(shè)備,以外部的82489DX芯片形式存在。在P6家族和Pentium處理器后,以APIC on Chip形式存在,引入了處理器內(nèi)部的local APIC架構(gòu),和82489DX 外部APIC相比較功能得到了擴(kuò)展和增強(qiáng)。

Pentium 4和Intel Xeon處理器在APIC的基礎(chǔ)上進(jìn)一步擴(kuò)展,形成了xAPIC體系,以及最后在xAPIC基礎(chǔ)上再一次擴(kuò)展的x2APIC體系。

1 APIC

每個(gè)logical processor(邏輯處理器)都有自己的local APIC,每個(gè)local APIC包括了一組local APIC寄存器,用來(lái)控制local和external中斷的產(chǎn)生、發(fā)送和接收等,也產(chǎn)生和發(fā)送IPI(處理器間的中斷消息)。local APIC寄存器組以?xún)?nèi)存映射形式映射到物理地址空間上,因此軟件可以使用MOV指令進(jìn)行訪(fǎng)問(wèn)。

然而在x2APIC模式上local APIC寄存器映射到MSR寄存器組來(lái)代替映射內(nèi)存,軟件使用RDMSR和WRMSR指令來(lái)訪(fǎng)問(wèn)local APIC寄存器。

如下所示,這是在支持Intel Hyper-Threading Technology的MP系統(tǒng)上,兩個(gè)logical processor(線(xiàn)程)共享一個(gè)processor core執(zhí)行單元。

每個(gè)local APIC有自己的local APIC ID,這個(gè)ID決定了logical processor在system bus上的地址,可以用于處理器間的消息接收和發(fā)送,也可用于外部中斷消息的接收。

標(biāo)準(zhǔn)PC上兩片級(jí)聯(lián)的8259提供了理論上15個(gè)中斷輸入源,但實(shí)際系統(tǒng)中這些中斷源遠(yuǎn)遠(yuǎn)不夠用。

從Pentium開(kāi)始,微機(jī)系統(tǒng)中引入了高級(jí)可編程中斷控制器APIC(Advanced Programmable Interrupt Controller), APIC兼容PIC(Programmable Interrupt Controller)。

新型高級(jí)可編程中斷控制器SAPIC(StreamLined Advanced Programmable Interrupt Controller)是APIC的64位升級(jí)版本。

APIC可以用于單CPU和多CPU系統(tǒng)中。 引入APIC一方面是為了支持多處理器系統(tǒng)需要 ,使外部中斷能被有選擇地交給某一個(gè)CPU來(lái)處理。

CPU利用處理器間中斷IPI (Inter-Processor Interrupt),可以將一個(gè)外部中斷交給另一個(gè)CPU來(lái)處理 ,也可以在CPU之間發(fā)布消息,或者實(shí)現(xiàn)搶占式調(diào)度。

多處理器系統(tǒng)中,CPU通過(guò)彼此發(fā)送中斷來(lái)完成它們之間的通信。另一方面,擴(kuò)展了系統(tǒng)可用的中斷數(shù)達(dá)到24個(gè),分隔了PCI/ISA設(shè)備使用的中斷,在APIC系統(tǒng)中只有PCI設(shè)備才能使用16~23號(hào)中斷,而ISA設(shè)備仍然使用常規(guī)的0~15號(hào)中斷,解決了使用8259中斷控制器所帶來(lái)的中斷共享、中斷優(yōu)先級(jí)不易控制等問(wèn)題。

ISA總線(xiàn): (Industry Standard Architecture:工業(yè)標(biāo)準(zhǔn)體系結(jié)構(gòu))是為PC/AT電腦而制定的總線(xiàn)標(biāo)準(zhǔn),為16位體系結(jié)構(gòu),只能支持16位的I/O設(shè)備,數(shù)據(jù)傳輸率大約是16MB/S。也稱(chēng)為AT標(biāo)準(zhǔn)。ISA是IndustryStandardArchitecture的縮寫(xiě)ISA插槽是基于ISA總線(xiàn)(IndustrialStandardArchitecture,工業(yè)標(biāo)準(zhǔn)結(jié)構(gòu)總線(xiàn))的擴(kuò)展插槽,其顏色一般為黑色,比PCI接口插槽要長(zhǎng)些,位于主板的最下端。其工作頻率為8MHz左右,為16位插槽,最大傳輸率16MB/sec,可插接顯卡,聲卡,網(wǎng)卡已及所謂的多功能接口卡等擴(kuò)展插卡。其缺點(diǎn)是CPU資源占用太高,數(shù)據(jù)傳輸帶寬太小,是已經(jīng)被淘汰的插槽接口。

ISA是8/16bit的系統(tǒng)總線(xiàn),最大傳輸速率僅為8MB/s,但允許多個(gè)CPU共享系統(tǒng)資源。由于兼容性好,它在上個(gè)世紀(jì)80年代是最廣泛采用的系統(tǒng)總線(xiàn),不過(guò)它的弱點(diǎn)也是顯而易見(jiàn)的,比如傳輸速率過(guò)低、CPU占用率高、占用硬件中斷資源等。后來(lái)在PC‘98規(guī)范中,就開(kāi)始放棄了ISA總線(xiàn),而Intel從i810芯片組開(kāi)始,也不再提供對(duì)ISA接口的支持。

PCI-Express(peripheral component interconnect express)是一種高速串行計(jì)算機(jī)擴(kuò)展總線(xiàn)標(biāo)準(zhǔn),它原來(lái)的名稱(chēng)為“3GIO”,是由英特爾在2001年提出的,旨在替代舊的PCI,PCI-X和AGP總線(xiàn)標(biāo)準(zhǔn)。PCI總線(xiàn)已成為了計(jì)算機(jī)的一種標(biāo)準(zhǔn)總線(xiàn)。

PCI總線(xiàn)取代了早先的ISA總線(xiàn)。有許多優(yōu)點(diǎn),比如即插即用(Plug and Play)、中斷共享等。所謂即插即用,是指當(dāng)板卡插入系統(tǒng)時(shí),系統(tǒng)會(huì)自動(dòng)對(duì)板卡所需資源進(jìn)行分配,如基地址、中斷號(hào)等,并自動(dòng)尋找相應(yīng)的驅(qū)動(dòng)程序。而不象舊的ISA板卡,需要進(jìn)行復(fù)雜的手動(dòng)配置。實(shí)際的實(shí)現(xiàn)遠(yuǎn)比說(shuō)起來(lái)要復(fù)雜。

在PCI板卡中,有一組寄存器,叫"配置空間"(Configuration Space),用來(lái)存放基地址與內(nèi)存地址,以及中斷等信息。以?xún)?nèi)存地址為例。當(dāng)上電時(shí),板卡從ROM里讀取固定的值放到寄存器中,對(duì)應(yīng)內(nèi)存的地方放置的是需要分配的內(nèi)存字節(jié)數(shù)等信息。

操作系統(tǒng)要根據(jù)這個(gè)信息分配內(nèi)存,并在分配成功后把相應(yīng)的寄存器中填入內(nèi)存的起始地址。這樣就不必手工設(shè)置開(kāi)關(guān)來(lái)分配內(nèi)存或基地址了。對(duì)于中斷的分配也與此類(lèi)似。ISA卡的一個(gè)重要局限在于中斷是獨(dú)占的,而我們知道計(jì)算機(jī)的中斷號(hào)只有16個(gè),系統(tǒng)又用掉了一些,這樣當(dāng)有多塊ISA卡要用中斷時(shí)就會(huì)有問(wèn)題了。PCI總線(xiàn)的中斷共享由硬件與軟件兩部分組成。

硬件上,采用電平觸發(fā)的辦法:中斷信號(hào)在系統(tǒng)一側(cè)用電阻接高,而要產(chǎn)生中斷的板卡上利用三極管的集電極將信號(hào)拉低。這樣不管有幾塊板產(chǎn)生中斷,中斷信號(hào)都是低;而只有當(dāng)所有板卡的中斷都得到處理后,中斷信號(hào)才會(huì)回復(fù)高電平。

軟件上,采用中斷鏈的方法:假設(shè)系統(tǒng)啟動(dòng)時(shí),發(fā)現(xiàn)板卡A用了中斷7,就會(huì)將中斷7對(duì)應(yīng)的內(nèi)存區(qū)指向A卡對(duì)應(yīng)的中斷服務(wù)程序入口ISR_A;然后系統(tǒng)發(fā)現(xiàn)板卡B也用中斷7,這時(shí)就會(huì)將中斷7對(duì)應(yīng)的內(nèi)存區(qū)指向ISR_B,同時(shí)將ISR_B的結(jié)束指向ISR_A。

以此類(lèi)推,就會(huì)形成一個(gè)中斷鏈。而當(dāng)有中斷發(fā)生時(shí),系統(tǒng)跳轉(zhuǎn)到中斷7對(duì)應(yīng)的內(nèi)存,也就是ISR_B。ISR_B就要檢查是不是B卡的中斷,如果是,要處理,并將板卡上的拉低電路放開(kāi);如果不是,則呼叫ISR_A。這樣就完成了中斷的共享。咱們繼續(xù)

值得注意的是,只有Windows 2000以后的操作系統(tǒng)才支持APIC, Linux可以支持但需要定制,缺省安裝并不支持。

BIOS運(yùn)行于實(shí)模式,不支持APIC, APIC只有在保護(hù)模式下才能使用。 (因此8259A)

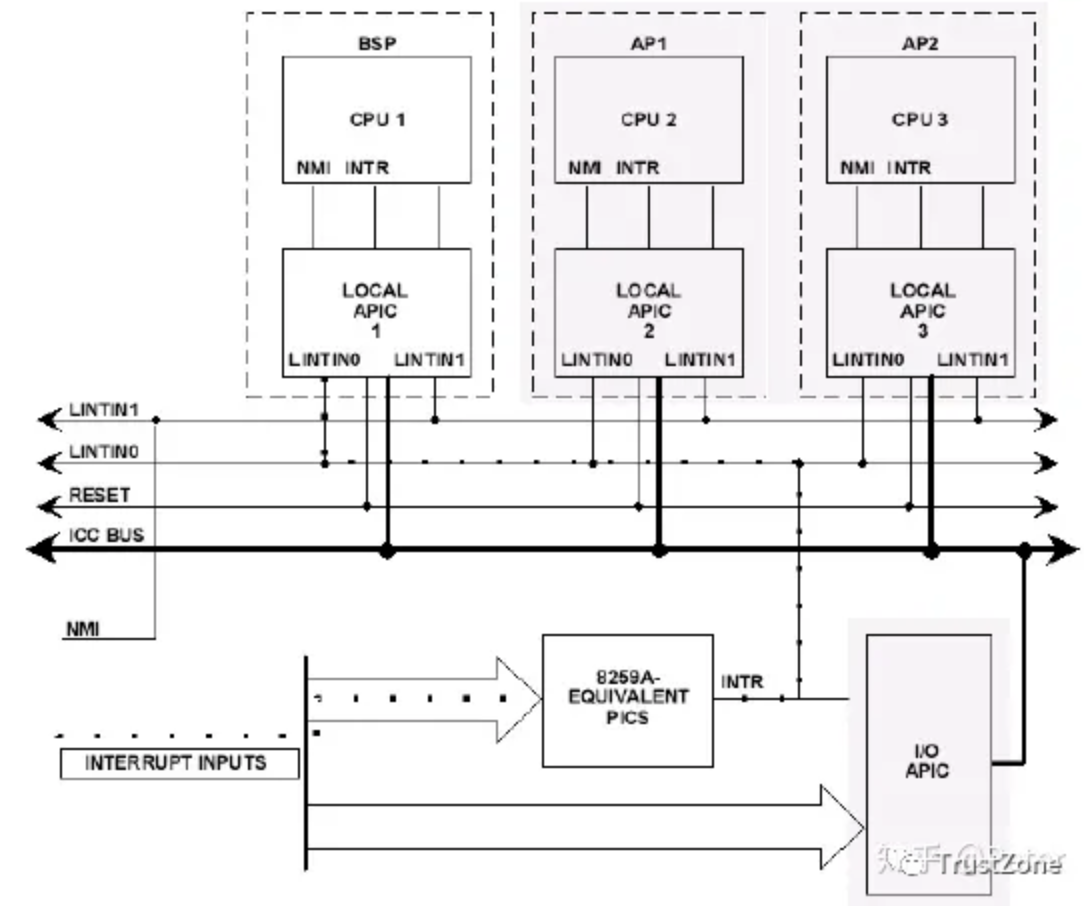

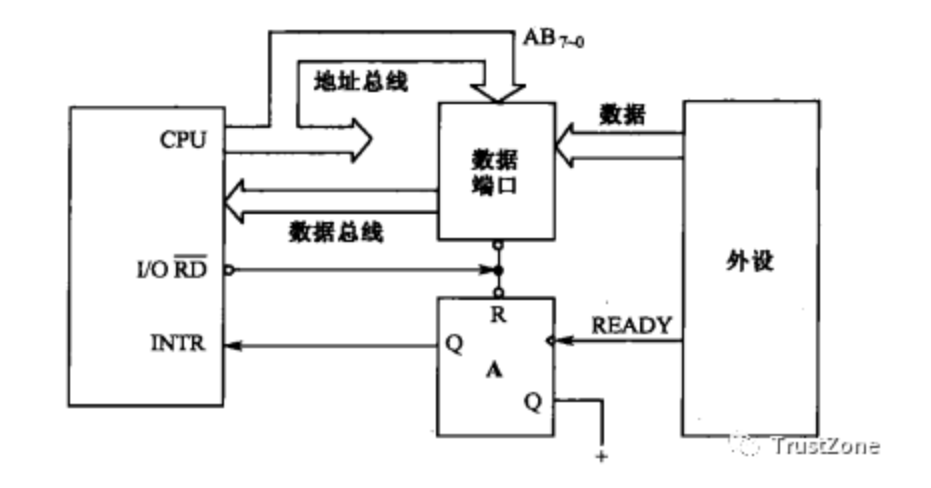

整個(gè)APIC系統(tǒng)可以分為兩大部分:LAPIC(Local APIC)和IO APIC,如圖23所示。

單核或者多核情況下,每個(gè)處理器中都有自己的LAPIC,而IO APIC是作為系統(tǒng)芯片組中一部分,在PCI-to-ISA bridge的LPC控制器內(nèi),系統(tǒng)最多有8個(gè)IO APIC。

LAPIC通過(guò)系統(tǒng)總線(xiàn)接收該處理器產(chǎn)生的本地中斷(例如時(shí)鐘中斷等)及處理器間中斷,并接收外部的中斷消息,如來(lái)自IO APIC的消息等。

IO APIC負(fù)責(zé)接收所有外部的硬件中斷,并翻譯成消息選擇發(fā)給接收中斷的處理器。

APIC功能可以被關(guān)閉。 APIC被關(guān)閉時(shí),由集成在芯片組內(nèi)的8259功能模塊來(lái)處理中斷 , 此時(shí)LAPIC的引腳LINT0連接到INTR, LINT1連接到NMI 。本節(jié)介紹的APIC以Pentium 4和Xeon為主,Pentium采用的APIC有所不同。

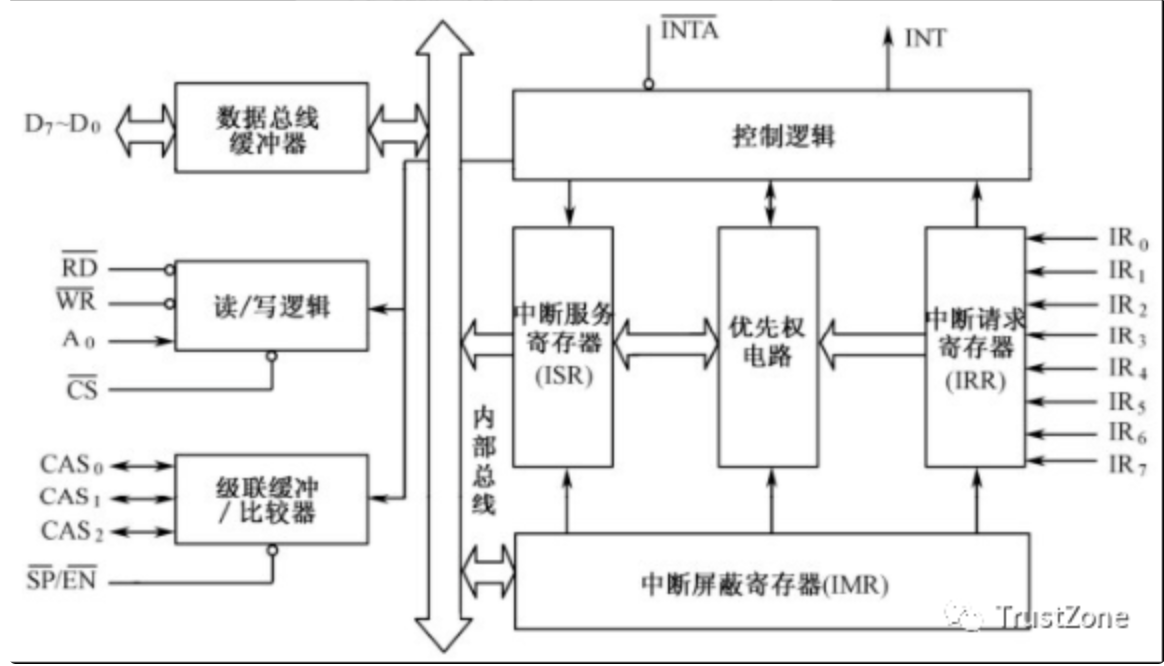

8259A內(nèi)部結(jié)構(gòu)

2 LAPIC

典型地,8259兼容類(lèi)的legacy中斷控制器是在uni-processor(單處理器)系統(tǒng)上使用,已不能適應(yīng)于多處理器環(huán)境,而I/O APIC能適用于multi-porcessor(多處理器)環(huán)境上。

I/O APIC可以發(fā)送中斷消息到指向的logical processor上。I/O APIC屬于芯片組的一部分,現(xiàn)稱(chēng)為PCH(Platform controller Hub),位于PCIto-ISA bridge(南橋芯片)的LPC控制器上。

各芯片組廠商的南橋名稱(chēng)都有所不同,例如英特爾稱(chēng)之為I/O路徑控制器(ICH,IO Controller Hub)或平臺(tái)路徑控制器(PCH)。因此后面看著叫PCH也不需要奇怪哦!!!

I/O APIC也有自己的寄存器,同樣也以?xún)?nèi)存映射形式映射到物理地址空間上。

LAPIC(Local APIC,本地APIC)包含了8259和8254的功能。

Intel 8253/8254是一個(gè)可編程定時(shí)/計(jì)數(shù)器(PIT-Programmable Interval Timer)芯片,用于處理計(jì)算機(jī)中的精確時(shí)間延遲。該芯片提供了 3個(gè)獨(dú)立的16位計(jì)數(shù)器通道。每個(gè)通道可工作在不同的工作方式下, 并且這些工作方式均可以使用軟件來(lái)設(shè)置。對(duì)于PC/AT及其兼容微機(jī)系統(tǒng)采用的是8254芯片。Linux 0.11操作系統(tǒng)只對(duì)通道0進(jìn)行了重新設(shè)置,使得該計(jì)數(shù)器工作在方式3下,并且每間隔10毫秒發(fā)出一個(gè)信號(hào)以產(chǎn)生中斷請(qǐng)求信號(hào)(IRQ0)。這個(gè)間隔定時(shí)產(chǎn)生的中斷請(qǐng)求就是Linux 0.11內(nèi)核工作的脈搏,它用于定時(shí)切換當(dāng)前執(zhí)行的任務(wù)和統(tǒng)計(jì)每個(gè)任務(wù)使用的系統(tǒng)資源量(時(shí)間)。

它能響應(yīng)以下幾種中斷:

- ① 系統(tǒng)中斷:IO APIC送來(lái)的系統(tǒng)中斷請(qǐng)求,由IO APIC交給中斷請(qǐng)求指定的目標(biāo)處理器處理。

- ③ 本地中斷:本地APIC產(chǎn)生的系統(tǒng)中斷請(qǐng)求(計(jì)時(shí)器、LINT0/LINT1、性能監(jiān)控、溫度傳感器、錯(cuò)誤)。本地中斷只能由該CPU處理。

從P6系列處理器開(kāi)始,可以用特殊命令CPUID探測(cè)LAPIC的存在。如執(zhí)行以下命令:

MOV EAX, 1CPUID

返回值在EDX寄存器中,當(dāng)返回值第9位為1時(shí),表示本地APIC存在,否則表示不存在。

下面簡(jiǎn)要介紹LAPIC的相關(guān)機(jī)制。

- (1)中斷發(fā)布方式

本地APIC的中斷發(fā)布方式分為靜態(tài)和動(dòng)態(tài)兩種。

在靜態(tài)方式下,根據(jù)重定向表中的信息,中斷消息無(wú)條件地提交給某一個(gè)、幾個(gè)或全部CPU;

在動(dòng)態(tài)方式下,中斷消息通過(guò)TPR (Task Priority Register)判斷提交給最低優(yōu)先權(quán)的CPU或焦點(diǎn)CPU(已接收或正在處理該中斷)。

如果有多個(gè)CPU都執(zhí)行相同優(yōu)先級(jí)的進(jìn)程,則必須采用仲裁(Arbitration)技術(shù)。

- (2)IA32_APIC_BASE寄存器 在模式專(zhuān)用寄存器(Model Specific Register)中,有一個(gè)IA32_APIC_BASE寄存器,其索引為1BH。CPU通過(guò)它來(lái)配置和控制本地APIC,例如允許、禁止本地APIC及設(shè)置本地APIC寄存器的基地址。IA32_APIC_BASE寄存器的格式如圖24所示。

IA32_APIC_BASE寄存器

- E=1時(shí),啟用本地APIC。

- BSP=1時(shí),此CPU為引導(dǎo)處理器;

- BSP=0時(shí),為應(yīng)用處理器。

在多CPU系統(tǒng)中,只能有一個(gè)引導(dǎo)處理器。

本地APIC寄存器是多個(gè)寄32_APIC_BASE指定,使用4KB存儲(chǔ)器空間。

默認(rèn)情況下,Intel將LAPIC的寄存器都映射到了物理地址0xFEE00000H。

本地APIC寄存器長(zhǎng)度為32位、64位或者256位,所有地址邊界按照16字節(jié)即128位為邊界來(lái)訪(fǎng)問(wèn)。APIC地址映射見(jiàn)表如下

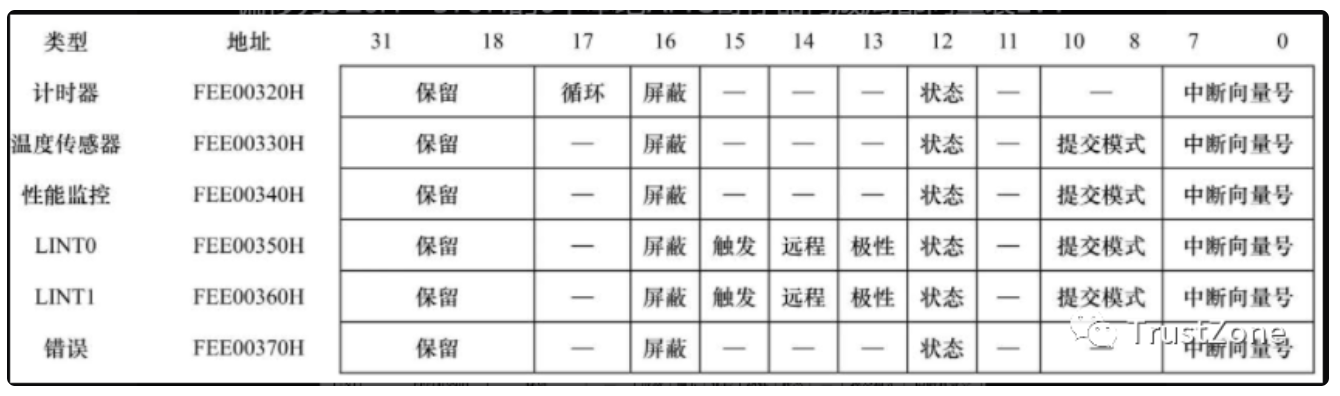

- (3)局部向量表

偏移為320H~370H的6個(gè)本地APIC寄存器構(gòu)成局部向量表LVT(Local Vector Table) ,分別代表6種中斷:

- 計(jì)時(shí)器中斷、

- 溫度傳感器中斷、

- 性能監(jiān)控中斷、

- LINT0中斷、

- LINT1中斷

- 錯(cuò)誤中斷。

LVT中各個(gè)寄存器的格式如圖25所示。

局部向量表LVT

- ① D16屏蔽位等于1時(shí),對(duì)應(yīng)的中斷類(lèi)型被屏蔽。

- ② D15觸發(fā)位等于0時(shí),邊沿觸發(fā);等于1時(shí),電平觸發(fā)。

- ③ D14遠(yuǎn)程位等于1時(shí),本地APIC收到中斷請(qǐng)求。收到中斷結(jié)束命令時(shí),置為0。

- ④ D13極性位等于0時(shí),LINT0/LINT1高電平有效;等于1時(shí),低電平有效。

- ⑤ D12狀態(tài)位等于1時(shí),已經(jīng)向CPU提交了中斷請(qǐng)求,但CPU還沒(méi)有應(yīng)答。

一共有5種提交模式,見(jiàn)表如下。

局部中斷提交模式

當(dāng)提交模式等于000B時(shí),CPU讀取LVT中的低8位作為中斷向量。

- (4)計(jì)時(shí)器中斷

本地APIC中的計(jì)時(shí)器相關(guān)寄存器包括當(dāng)前計(jì)數(shù)寄存器CCR、計(jì)數(shù)初值寄存器CR和除數(shù)寄存器DCR。

給CR寄存器賦值時(shí),初始值裝入CCR, CCR的值按一定頻率遞減,遞減的頻率等于系統(tǒng)總線(xiàn)頻率除以刻度系數(shù)。刻度系數(shù)由DCR確定。CCR的值遞減到0時(shí),向處理器提交計(jì)時(shí)器中斷。

當(dāng)計(jì)時(shí)器采用單次模式(循環(huán)位等于0)時(shí) ,提交計(jì)時(shí)器中斷后,CCR的值一直保持為0,直到向CR寄存器裝入新的初值。采用循環(huán)模式時(shí),提交計(jì)時(shí)器中斷后,CR的值重新到CCR,繼續(xù)遞減。計(jì)數(shù)過(guò)程中若初始計(jì)數(shù)寄存器被重置了,則將使用新的初始計(jì)數(shù)值,重新開(kāi)始計(jì)數(shù)。

- (5)發(fā)布中斷

通過(guò)寫(xiě)入ICR寄存器,CPU可以向自身或者其他CPU發(fā)布處理器間中斷IPI。ICR寄存器為64位,低32位的地址為FEE00300H,高32位的地址為FEE00310H。

ICR的主要功能包括:發(fā)送一個(gè)中斷給另外一個(gè)處理器;允許處理器轉(zhuǎn)發(fā)它收到的一個(gè)中斷,但不對(duì)另一個(gè)處理器的請(qǐng)求提供服務(wù) ;把處理器定向到中斷本身,即執(zhí)行一次自我中斷;傳送特定的IPI,比如啟動(dòng)IPI(SIPI)消息,到其他處理器。

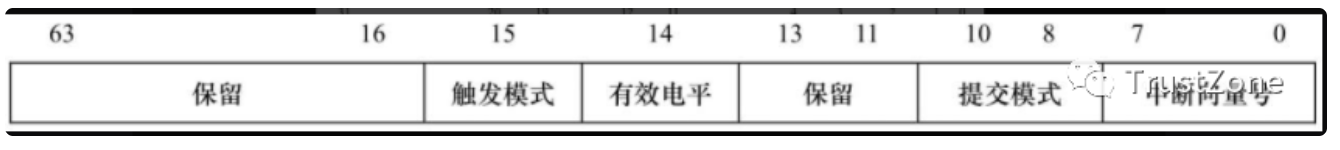

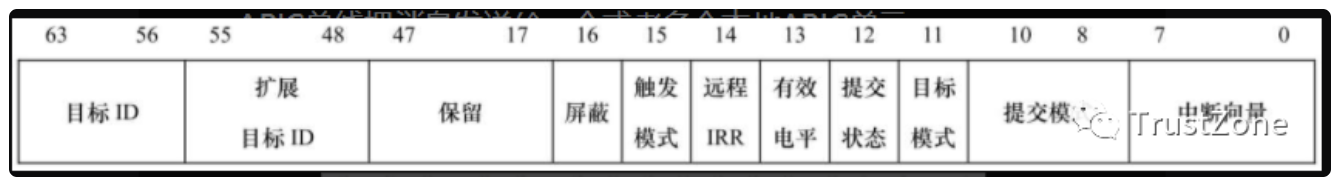

ICR寄存器格式如圖26所示。

ICR寄存器中,D13、D16、D17、D20~D55均保留。其他位含義如下:

- ① D7~D0表示中斷向量號(hào)。

- ② D10~D8表示提交模式:

- a. 000(固定):傳送向量域中指定的中斷到目標(biāo)處理器或者處理器組。

- b. 001(最低優(yōu)先權(quán)):除了把中斷傳送給目的域中指定的目標(biāo)處理器組中的優(yōu)先級(jí)最低的處理器之外,其他同于固定模式。處理器傳送最低優(yōu)先權(quán)IPI的能力是與模型相關(guān)的,BIOS和操作系統(tǒng)軟件應(yīng)該避免它。

- c. 010(SMI):傳送一個(gè)SMI中斷給目標(biāo)處理器或者處理器組。為了與未來(lái)兼容,該向量域應(yīng)該設(shè)成00H。

- d. 011(保留)。e. 100(NMI):傳送一個(gè)NMI中斷給目標(biāo)處理器或者處理器組。忽略向量信息。

- f. 101(INIT):傳送一個(gè)INIT請(qǐng)求給目標(biāo)處理器或者處理器組,使之執(zhí)行一次初始化。作為這個(gè)IPI消息的結(jié)果之一,所有處理器都執(zhí)行一次初始化。

- g. 110(未激活I(lǐng)NIT的電平):發(fā)送一個(gè)同步消息給系統(tǒng)中的所有本地APIC,把它們的仲裁ID設(shè)置成它們的APIC ID。對(duì)于這個(gè)傳送模式,電平標(biāo)志必須設(shè)為0,觸發(fā)模式標(biāo)志設(shè)為1,目標(biāo)指示應(yīng)為10(Pentium 4和Intel Xeon處理器中不支持)。

- ③ D11用來(lái)指定接收目標(biāo)的模式。D11=0時(shí),使用物理目標(biāo)模式;D11=1時(shí),使用邏輯目標(biāo)模式。

- ④ D12提交狀態(tài)是只讀位。等于1時(shí),表示上一次發(fā)送的IPI消息還沒(méi)有被目標(biāo)CPU接收。

- ⑤ D14有效電平位。0表示無(wú)效電平;1表示有效電平。注意,無(wú)效電平可能是高電平或者低電平,有效電平也可能是高電平或者低電平。

- ⑥ D15觸發(fā)模式位。0表示邊沿觸發(fā);1表示電平觸發(fā)。

- ⑦ D19~D18目標(biāo)指示位。等于00時(shí),表示根據(jù)目標(biāo)ID確定發(fā)送目標(biāo);等于01時(shí),發(fā)送給自己;等于10時(shí),發(fā)送給所有CPU;等于11時(shí),發(fā)送給所有CPU(自己除外)。

- ⑧ D64~D56表示消息的目標(biāo)地址(Message Destination Address, MDA)。目標(biāo)地址的表示方式包括兩種:物理目標(biāo)模式和邏輯目標(biāo)模式。 下面介紹這兩種模式。

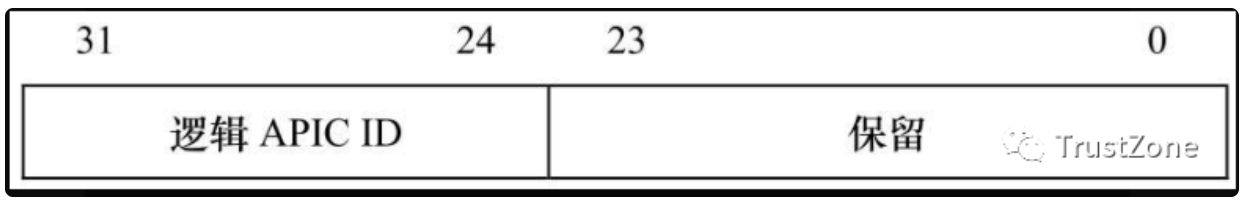

- 平面模式:本地APIC中的邏輯目標(biāo)寄存器(Logic Destination Register, LDR)的高8位保存的是邏輯APIC標(biāo)識(shí),如圖28所示。將邏輯APIC標(biāo)識(shí)與MDA相與,如果得到的結(jié)果有任何一位等于1,那么這個(gè)APIC就接收IPI消息。在平面模式下,由于邏輯APIC標(biāo)識(shí)有8個(gè)二進(jìn)制位,支持最多8個(gè)CPU。

LDR格式

* 集群模式:Pentium CPU支持平面集群模式和層次集群模式,而Pentium 4只支持層次集群模式。在層次集群模式下,在CPU的外部還必須設(shè)置專(zhuān)門(mén)的集群管理設(shè)備,支持最多15個(gè)集群,每個(gè)集群上最多連接4個(gè)APIC,每個(gè)集群使用單獨(dú)的APIC或系統(tǒng)總線(xiàn)。例9.14 假設(shè)三個(gè)CPU的logical模式配置為:CPU 1的LDR值為00000001b, CPU 2的LDR值為00010010b, CPU3的LDR值為00000100b,此時(shí)DFR的model值為0000b。IO APIC發(fā)出一條中斷消息,其Destination Mode為1, Destination field值為00000001b。試分析該中斷消息由哪些CPU接收。解答:三個(gè)LAPIC收到該消息后,CPU1、CPU3通過(guò)Destination field的高4位判斷出該消息目的地為本簇,再將自身Logical APIC ID的低4位與Destination field低4位進(jìn)行位與操作,CPU1與結(jié)果不為0,故最終CPU1接收該中斷消息,CPU2、CPU3丟棄。

* 當(dāng)?shù)?3~56位為FFH時(shí),消息廣播給所有的APIC。

* 對(duì)于Pentium 4和Intel Xeon處理器來(lái)說(shuō),一個(gè)單個(gè)目的(本地APIC ID從00H到FEH)或?qū)λ蠥PIC的廣播(APIC ID是FFH)都可能在物理模式下指定。

* 對(duì)于P6系列和Pentium處理器來(lái)說(shuō),一個(gè)單個(gè)目的是由具有從0H到0EH的本地APIC ID的物理目的傳送模式指定的,允許APIC總線(xiàn)中訪(fǎng)問(wèn)多達(dá)15個(gè)本地APIC。對(duì)所有本地APIC的廣播,是由0FH指定的。

* a.物理目標(biāo)模式。每一個(gè)本地APIC都有唯一的APIC ID。在ICR寄存器的第63~56位中指定一個(gè)APIC ID,消息將發(fā)送給與它相同的另一個(gè)APIC。

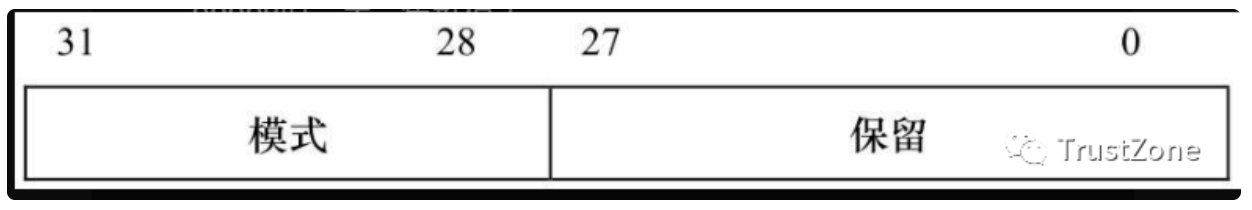

* b.邏輯目標(biāo)模式。使用邏輯目標(biāo)模式發(fā)送IPI時(shí),目標(biāo)APIC可以采用平面模式和集群模式。本地APIC中有一個(gè)目標(biāo)格式寄存器(Destination Format Register, DFR),如圖27所示,它的高4位(第31~28位)等于1111B時(shí),表示平面模式;等于0000B時(shí),表示集群模式。

- (6)處理中斷 本地APIC接收到系統(tǒng)中斷、處理器間中斷、本地中斷后,按照以下流程進(jìn)行處理:

- ① 檢查系統(tǒng)中斷、處理器間中斷消息中的目標(biāo)地址與本地APIC是否匹配,如果不匹配,則忽略此消息。

- ② 檢查中斷消息中的提交模式,如果是NMI、SMI、INIT、ExtINT或者SIPI,那么由這個(gè)CPU直接處理;否則設(shè)置IRR寄存器(共256位)中的相應(yīng)位。

- ③ 當(dāng)有IRR和ISR寄存器中記錄了中斷請(qǐng)求時(shí),按照中斷請(qǐng)求的中斷向量、任務(wù)優(yōu)先權(quán)寄存器TPR、處理器優(yōu)先權(quán)寄存器PPR進(jìn)行優(yōu)先級(jí)判斷,交給某一個(gè)CPU處理。

- ④ 中斷結(jié)束。提交模式為固定時(shí),中斷服務(wù)程序?qū)慙APIC的EOI寄存器,將中斷從ISR寄存器中清除,如果是電平觸發(fā),LAPIC向系統(tǒng)總線(xiàn)發(fā)送一條消息,表示中斷處理結(jié)束。提交模式為NMI、SMI、INIT、ExtINT或者SIPI時(shí),中斷服務(wù)程序不需要寫(xiě)入EOI寄存器。

- (7)中斷請(qǐng)求寄存器IRR和中斷服務(wù)寄存器ISR

中斷請(qǐng)求寄存器IRR共256位,地址為FEE00200H~FEE00270H;中斷服務(wù)寄存器ISR也是256位,地址為FEE00100H~FEE00170H。

如果中斷的提交模式為固定方式,中斷請(qǐng)求寄存器IRR記錄了本地APIC已經(jīng)接收到的,但還沒(méi)有指派給某一個(gè)CPU的中斷。當(dāng)CPU可以處理中斷時(shí),IRR中具有最高優(yōu)先級(jí)的中斷(即中斷向量最大)對(duì)應(yīng)的位被置為0,再將ISR中的對(duì)應(yīng)位置為1。ISR中具有最高優(yōu)先級(jí)的中斷被發(fā)送給CPU進(jìn)行處理。

在處理高優(yōu)先級(jí)的中斷時(shí),如果發(fā)生了低優(yōu)先級(jí)的中斷,該中斷的IRR位置為1。在高優(yōu)先級(jí)的中斷處理完成后,中斷服務(wù)程序?qū)懭隕OI寄存器,清除高優(yōu)先級(jí)中斷的ISR位。這時(shí)低優(yōu)先級(jí)中斷就會(huì)被處理。在處理某個(gè)優(yōu)先級(jí)的中斷時(shí),如果發(fā)生了相同優(yōu)先級(jí)的中斷,該中斷的IRR位置為1。前一個(gè)中斷處理完成后,后面的中斷才會(huì)被處理。在處理某個(gè)優(yōu)先級(jí)的中斷時(shí),如果發(fā)生了更高優(yōu)先級(jí)的中斷,本地APIC可以向CPU發(fā)送中斷,前一個(gè)中斷被暫停,進(jìn)入新的中斷服務(wù)程序。這就是中斷嵌套。

觸發(fā)模式寄存器TMR也是256位。當(dāng)中斷的IRR位置為1時(shí),邊沿觸發(fā)中斷的TMR位清為0,電平觸發(fā)中斷的TMR位置為1。

- (8)優(yōu)先權(quán) 中斷優(yōu)先權(quán)由它的中斷向量號(hào)決定,中斷優(yōu)先權(quán)等于中斷向量號(hào)除以16,即中斷向量號(hào)的高4位,范圍是2~15。注意,中斷向量號(hào)0~31由CPU保留。

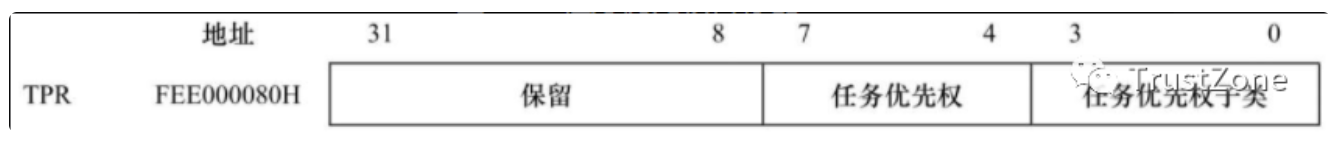

任務(wù)優(yōu)先權(quán)寄存器TPR的地址為FEE00080H,格式如圖29所示。

任務(wù)優(yōu)先權(quán)寄存器TPR

處理器優(yōu)先權(quán)寄存器PPR的地址為FEE000A0H,格式如圖30所示。

處理器優(yōu)先權(quán)寄存器PPR

中斷優(yōu)先權(quán)大于任務(wù)優(yōu)先權(quán)時(shí),中斷才會(huì)被處理。

CPU通過(guò)設(shè)置任務(wù)優(yōu)先權(quán)寄存器TPR,禁止低級(jí)別的中斷。例如,把TPR中的第7~4位(任務(wù)優(yōu)先權(quán))設(shè)為15時(shí),那么所有的外部中斷(除NMI、SMI、INIT、ExtINT等)都會(huì)被屏蔽。而任務(wù)優(yōu)先權(quán)設(shè)為0時(shí),這些外部中斷不被屏蔽。

處理器優(yōu)先權(quán)寄存器不能被程序所修改,是一個(gè)只讀寄存器。 它反映了當(dāng)前CPU正在執(zhí)行的程序的優(yōu)先級(jí)。PPR的值是當(dāng)前正在服務(wù)的中斷向量和TPR二者之間較高的值。

設(shè)ISRV是ISR中被設(shè)置為1的最高優(yōu)先權(quán)的中斷向量,ISR中所有位等于0時(shí),ISRV等于0。PPR按照以下公式來(lái)確定:

IF TPR[7∶∶4] ≥ ISRV[7∶∶4]THEN PPR[7∶∶0]=TPR[7∶∶0]ELSE PPR[7∶∶4]=ISRV[7∶∶4]; PPR[3∶∶0]=0

- (9)消息信號(hào)中斷

PCI 2.2規(guī)范中引入了消息信號(hào)中斷MSI(Message Signaled Interrupts)。PCI設(shè)備可以用兩種方法向CPU發(fā)出中斷請(qǐng)求:

- ①用設(shè)備的一個(gè)引腳發(fā)送中斷請(qǐng)求信號(hào);

- ②用MSI向處理器傳送中斷請(qǐng)求。

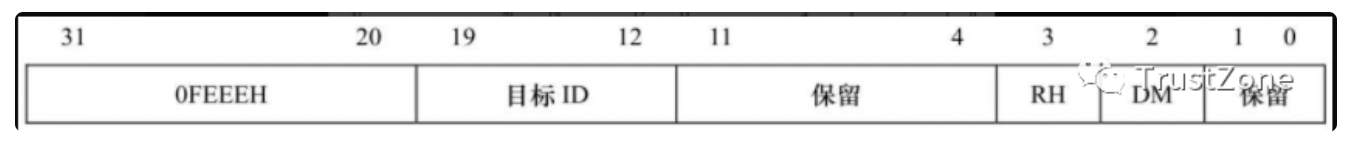

采用MSI向CPU發(fā)送中斷請(qǐng)求時(shí),PCI設(shè)備發(fā)起一個(gè)PCI寫(xiě)操作,向一個(gè)特殊的地址寫(xiě)入一個(gè)特定數(shù)據(jù)。地址的格式如圖9-31所示,數(shù)據(jù)的格式如圖32所示。

MSI地址格式

MSI數(shù)據(jù)格式

在地址中,目標(biāo)ID指定了MSI消息發(fā)送給哪一個(gè)(組)CPU, RH說(shuō)明是否要把消息發(fā)送給一組中具有最低優(yōu)先權(quán)的CPU, DM則指示采用物理目標(biāo)模式或者邏輯目標(biāo)模式。

在數(shù)據(jù)部分,觸發(fā)模式有邊沿觸發(fā)和電平觸發(fā)兩種,后者又分高電平有效和低電平有效。提交模式分為固定、最低優(yōu)先級(jí)、SMI、NMI、INIT、ExtINT等幾種。

3 IO APIC

IO APIC用來(lái)替代傳統(tǒng)的8259中斷控制器,一般集成在ICH芯片組中。

ICH(I/O controller hub意思是“輸入/輸出控制器中心”,負(fù)責(zé)連接PCI總線(xiàn),IDE設(shè)備,I/O設(shè)備等,是英特爾的南橋芯片系列名稱(chēng)。

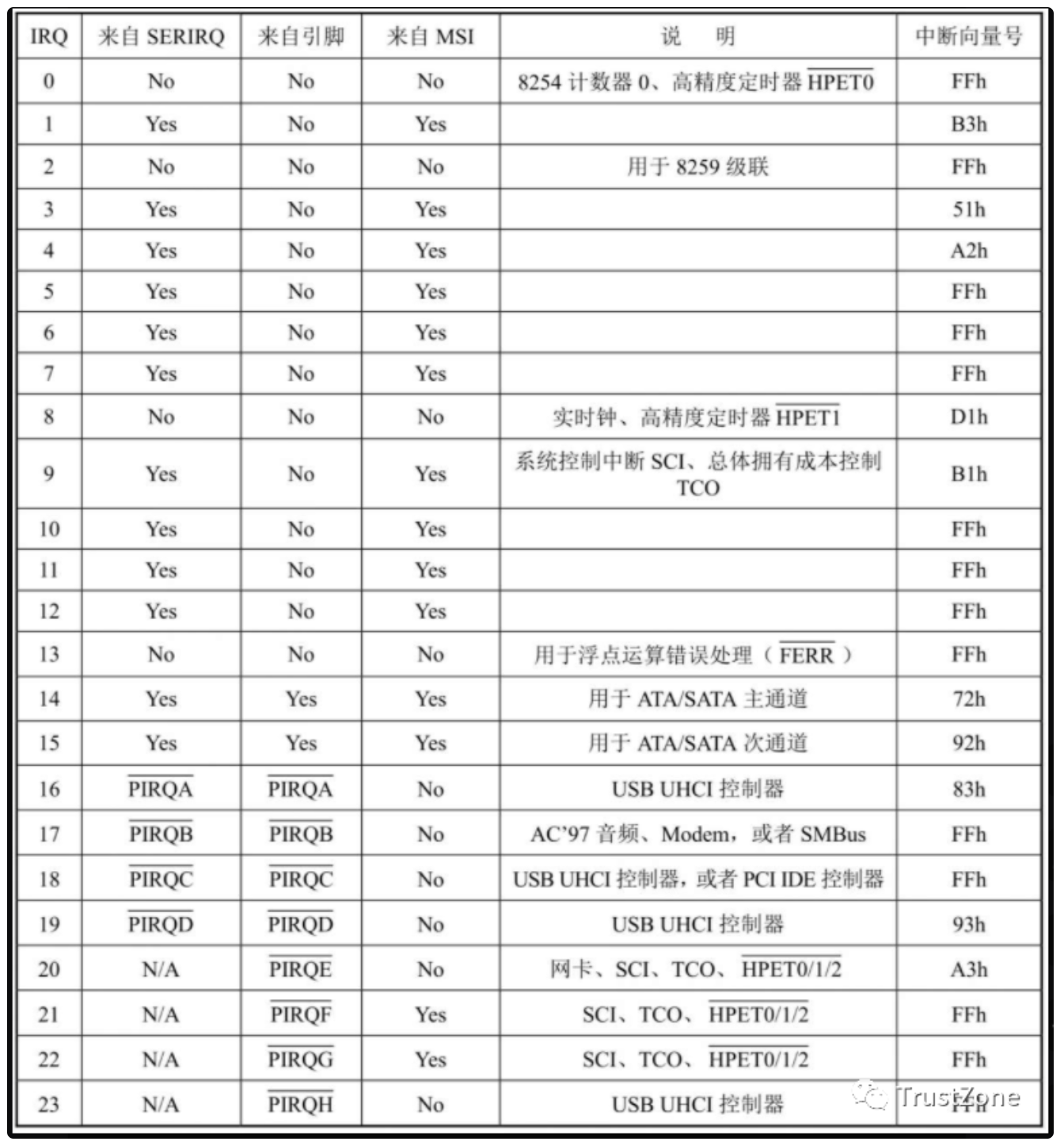

表7中列出了IO APIC管理下每個(gè)中斷源對(duì)應(yīng)的中斷向量。

表七:每個(gè)中斷源對(duì)應(yīng)的中斷向量

和8259相比,IO APIC能支持24個(gè)中斷源,不需要中斷應(yīng)答周期,可以將中斷請(qǐng)求發(fā)送給某一個(gè)指定的CPU。

IO APIC的中斷優(yōu)先權(quán)由中斷向量來(lái)確定,與中斷源(IRQ)無(wú)關(guān)。 (所以軟件編程的時(shí)候這個(gè)中斷向量的設(shè)置很需要注意,也更加體現(xiàn)了APIC的靈活性)

系統(tǒng)中最多可以擁有8個(gè)IO APIC,每一個(gè)IO APIC都分別有自己的輸入編碼,加起來(lái)一臺(tái)PC上會(huì)有上百個(gè)IRQ可供設(shè)備中斷使用。

IO APIC和LAPIC共同起作用,如果系統(tǒng)中沒(méi)有IO APIC,那么LAPIC就沒(méi)有用處,此時(shí)操作系統(tǒng)會(huì)使用8259。Intel系統(tǒng)中常用82093AA芯片來(lái)作為IO APIC。

- (1)IO APIC寄存器地址 Intel系統(tǒng)中,IO APIC默認(rèn)映射到物理地址FEC00000H。IO APIC一共有4個(gè)寄存器地址,見(jiàn)表8。

表八:IO APIC的寄存器

一共有64個(gè)32位內(nèi)部寄存器,其索引為0~63。內(nèi)部寄存器索引見(jiàn)表9。

表九:IO APIC內(nèi)部寄存器

- (2)重定向表

中斷重定向表中的每一項(xiàng)都有可以被單獨(dú)編程,用來(lái)指明中斷向量和優(yōu)先級(jí)、目標(biāo)處理器及選擇處理器的方式。

重定向表中的信息用于把每個(gè)外部IRQ信號(hào)轉(zhuǎn)換為一條消息,然后通過(guò)APIC總線(xiàn)把消息發(fā)送給一個(gè)或者多個(gè)本地APIC單元。

重定向表的格式如圖33所示。

表十:重定向表

目標(biāo)ID確定哪一個(gè)(組)CPU處理這個(gè)中斷。目標(biāo)模式等于0時(shí),即物理目標(biāo)模式,目標(biāo)ID的第59~56位表示某一個(gè)CPU的APIC ID;等于1時(shí),即邏輯目標(biāo)模式,目標(biāo)ID的第53~56位與CPU中的邏輯APIC標(biāo)識(shí)匹配,確定目標(biāo)。

向CPU發(fā)送中斷時(shí),擴(kuò)展目標(biāo)ID(8位)被放置在地址的第11~4位。地址格式如上圖所示。

屏蔽位等于1時(shí),這個(gè)中斷不會(huì)向CPU發(fā)送。觸發(fā)模式分為邊沿觸發(fā)(D15=0)和電平觸發(fā)(D15=1)兩種,后者又分高電平有效(D13=0)和低電平有效(D13=1)。

在電平觸發(fā)時(shí),遠(yuǎn)程IRR位有效。等于1時(shí),表示CPU的本地APIC已接受此中斷,收到本地APIC發(fā)送的EOI后,將此位清0。相對(duì)于本地APIC和CPU核心而言,IO APIC和本地APIC之間的傳遞是遠(yuǎn)程的。

提交狀態(tài)等于1時(shí),表示中斷消息已產(chǎn)生,但還沒(méi)有發(fā)送給本地APIC。提交模式分為固定(000B)、最低優(yōu)先級(jí)(001B)、SMI(010B)、NMI(100B)、INIT (101B)、ExtINT(111B)等幾種。

最低優(yōu)先級(jí)表示把這個(gè)中斷按照目標(biāo)ID提交給PPR最低的CPU。重定向表的第7~0位表示該中斷對(duì)應(yīng)的中斷向量號(hào),在表7中列出了某系統(tǒng)中各個(gè)IRQ對(duì)應(yīng)的中斷向量號(hào)。

以上就是對(duì)x86的中斷有了一個(gè)簡(jiǎn)單的了解,后續(xù)我們接著來(lái)看看ARM的GIC。

這個(gè)名稱(chēng)的由來(lái),是由于繪制架構(gòu)圖時(shí)所派生出來(lái)的稱(chēng)呼,第一次被提到這名詞時(shí)是在1991年采用PCl Local Bus架構(gòu)時(shí)。在Intel,PCl規(guī)格的創(chuàng)始者視PCI總線(xiàn)為整個(gè)PC平臺(tái)架構(gòu)的正中央。北橋芯片將PCl總線(xiàn)主干延伸至北邊,以支持CPU、存儲(chǔ)器或緩存(Cache)、以及其他攸關(guān)性能的功能。反之,南橋芯片將PCI總線(xiàn)主干延伸至南邊,并橋接起比較非攸關(guān)性能的I/O功能,例如磁盤(pán)接口等、音效等。CPU位于架構(gòu)圖的正北方,它透過(guò)較高速的北橋芯片鏈接北邊的系統(tǒng)設(shè)備,而北橋則透過(guò)較慢速的南橋芯片連接南邊的其他系統(tǒng)設(shè)備。雖然現(xiàn)今PC平臺(tái)架構(gòu)已將PCl總線(xiàn)主干取代,換上更快的I/O主干,但“橋”的傳統(tǒng)名稱(chēng)仍然延續(xù)使用。北橋(英語(yǔ):Northbridge)是基于Intel處理器的個(gè)人電腦主板芯片組兩枚芯片中的一枚,北橋用來(lái)處理高速信號(hào),例如中央處理器、存儲(chǔ)器、顯卡(PCI Express接口或AGP接口),還有與南橋之間的通信。北橋芯片位置剛好跟南橋芯片位置相反,它是靠近CPU部分,被散熱片覆蓋的大的那塊芯片,主要功能是負(fù)責(zé)控制、連接和處理CPU與內(nèi)存、與南橋通信。北橋芯片是主板的關(guān)鍵芯片,負(fù)責(zé)管理二級(jí)高速緩存,內(nèi)存的類(lèi)型和最大容量都由它決定,所以一般主板命名都是用北橋芯片的型號(hào)。有一些北橋會(huì)集成內(nèi)置顯示核心(如Intel GMA),也支持AGP或PCl Express接口。集成顯示核心的北橋若偵測(cè)到已安裝的PCle/AGP顯卡,會(huì)停止其GPU功能,但有些北橋可以允許同時(shí)使用集成式顯卡和安裝外加顯卡,作為多顯示輸出。英特爾在第一代Core i7中把存儲(chǔ)器控制器集成到了CPU,北橋的功能只剩下連接高速設(shè)備(如顯卡),此時(shí)Intel的南橋稱(chēng)為IOH (Io Controller Hub)。從LGA 1156、LGA 2011開(kāi)始,Intel處理器集成了北橋(存儲(chǔ)器控制器、高速PCl Express控制器和Intel HDGraphics),主板上只剩下南橋,Intel將其稱(chēng)為平臺(tái)路徑控制器(PCH)。

4、APIC與8259A

APIC全稱(chēng)是Advanced Programmable Interrupt Controller,高級(jí)可編程中斷控制器。

它是在奔騰P54C之后被引入進(jìn)來(lái)的。在現(xiàn)在的計(jì)算機(jī)它通常由兩個(gè)部分組成,分別為L(zhǎng)APIC(Local APIC,本地高級(jí)可編程中斷控制器)和IOAPIC(I/O高級(jí)可編程中斷控制器)。

LAPIC在CPU中,IOAPIC通常位于南橋 。

APIC是在PIC (Programmable Interrupt Controller) 的基礎(chǔ)上發(fā)展而來(lái)的。

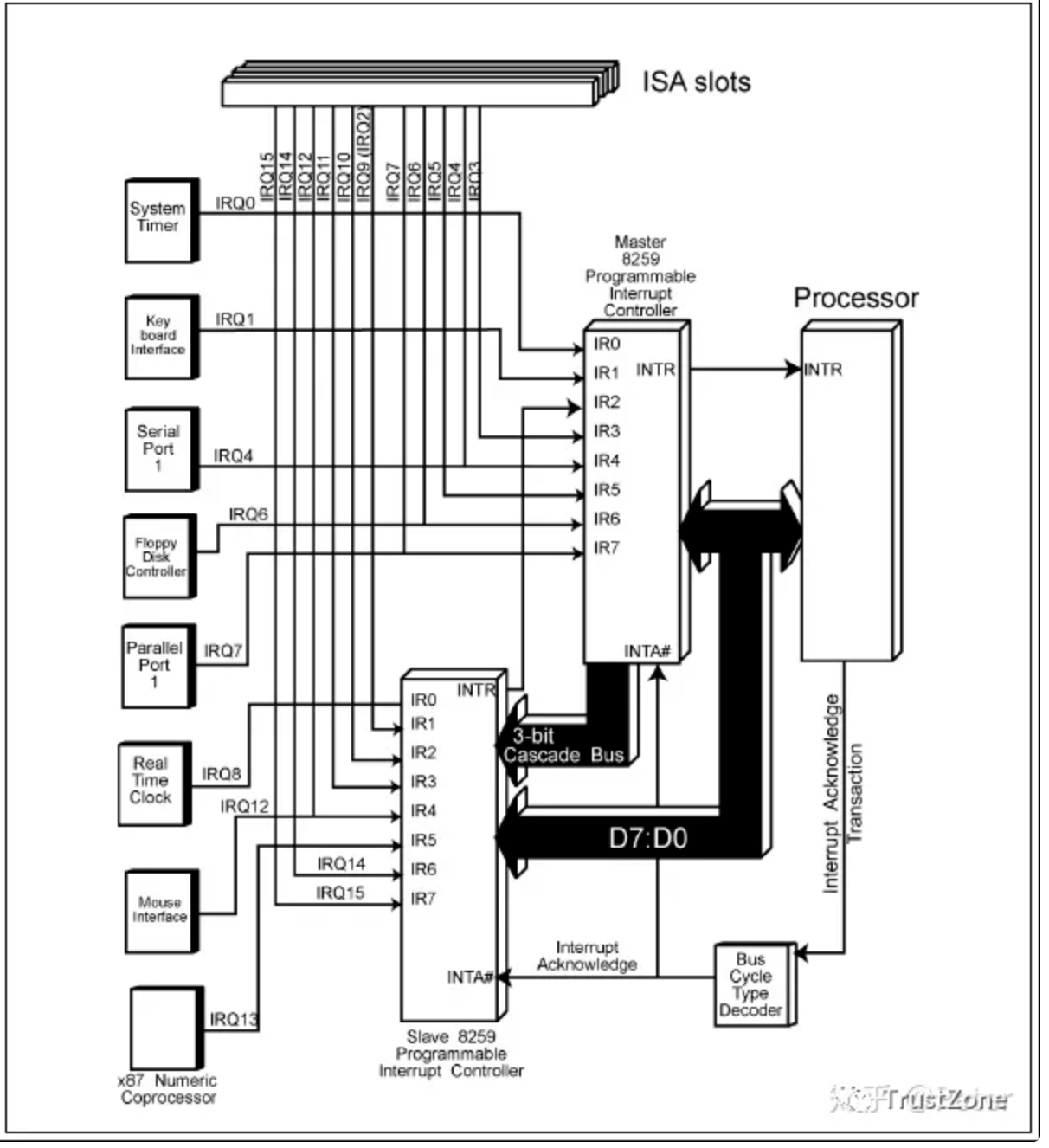

在傳統(tǒng)的單處理器的PC-AT 兼容的機(jī)器,通常使用8259A雙片級(jí)聯(lián)組成Legacy中斷控制器(如下圖所示)。一共可以連接15個(gè)設(shè)備(有一個(gè)管腳被用于串聯(lián)另一片8259)。PIC的優(yōu)先級(jí)規(guī)則比較簡(jiǎn)單,0號(hào)管腳的優(yōu)先級(jí)最高。

PIC可以通過(guò)ICW(Initialization CommandWord)編程設(shè)置起始的Vector號(hào)。

PIC在單個(gè)CPU的環(huán)境下工作的挺好,可是當(dāng)系統(tǒng)越來(lái)越復(fù)雜出現(xiàn)了多個(gè)CPU的情況,它就沒(méi)法很好的工作了。這種情況下所有的中斷都會(huì)丟給主8259連接的那個(gè)CPU,那么這個(gè)CPU就要處理所有的中斷,性能上就會(huì)有影響。在一個(gè)多處理器的系統(tǒng),任何一個(gè)CPU都應(yīng)該能夠響應(yīng)來(lái)自任何設(shè)備的中斷,這種就是所謂的對(duì)稱(chēng)式多重處理(Symmetric Multiprocessing)

IOAPIC: IOAPIC的主要作用是中斷的分發(fā)。最初有一條專(zhuān)門(mén)的APIC總線(xiàn)用于IOAPIC和LAPIC通信,在Pentium4 和Xeon 系列CPU出現(xiàn)后,他們的通信被合并到系統(tǒng)總線(xiàn)中。

Virtual Wire Mode:虛擬接線(xiàn)模式,該模式主要是為了向前兼容,可以理解為就是PIC。在這種模式下,IOAPIC會(huì)把8259A的模擬硬件產(chǎn)生的中斷信號(hào)直接送給BSP。

如上圖所示,每個(gè)CPU/Core中都有一個(gè)LAPIC。相比較于IOAPIC, LAPIC會(huì)更復(fù)雜一些,它不僅能夠處理來(lái)自IOAPIC的中斷消息,它還可以處理IPI(Inter-Processor Interrupt Messages),NMI,SMI和Init消息。

LAPIC 默認(rèn)使用基地址FEE00000h開(kāi)始的4KB空間用來(lái)訪(fǎng)問(wèn)內(nèi)部寄存器,從Pentium Pro開(kāi)始引入一個(gè)APIC_BASE 的MSR,可以用來(lái)設(shè)置基地址在任何4KB對(duì)齊的64GB內(nèi)存地址空間。IRR:LAPIC已經(jīng)收到中斷但是還未提交CPU處理。ISR:CPU已經(jīng)開(kāi)始處理中斷,但是尚未完成。TMR(Trigger Mode Register):中斷的觸發(fā)模式。EOI軟件寫(xiě)入表示中斷處理完成。

-

處理器

+關(guān)注

關(guān)注

68文章

19273瀏覽量

229712 -

溫度傳感器

+關(guān)注

關(guān)注

48文章

2940瀏覽量

156041 -

寄存器

+關(guān)注

關(guān)注

31文章

5342瀏覽量

120274 -

中斷控制器

+關(guān)注

關(guān)注

0文章

59瀏覽量

9455 -

DCR

+關(guān)注

關(guān)注

1文章

54瀏覽量

18821

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

8259A芯片是一種什么類(lèi)型的芯片?從硬件看中斷之8259A

從硬件看什么是中斷?從硬件看中斷之8088

干貨!Android之藍(lán)牙驅(qū)動(dòng)開(kāi)發(fā)經(jīng)驗(yàn)

如何在linux下查看中斷請(qǐng)求記錄

超干貨!Linux中斷響應(yīng)流程

Windows環(huán)境下硬件中斷的性能分析

基于APIC時(shí)鐘的嵌入式Linux內(nèi)核實(shí)時(shí)化研究

一個(gè)關(guān)于Linux中斷的問(wèn)題:硬件處理,初始化和中斷處理

linux中斷處理之IRQ中斷

實(shí)際中斷處理

STM32之FreeRTOS:(一) 中斷配置和臨界段的使用

硬件中斷OB的功能

CPU中斷程序:從硬件看什么是中斷?

干貨!從硬件看中斷之APIC

干貨!從硬件看中斷之APIC

評(píng)論