對于通信、雷達等無線電行業相關的朋友,我相信大家對于窄帶系統的設計,必然是輕車熟路,如數家珍。尤其是圍繞FPGA+AD/DA的數字收發的架構設計,那估計更是心中有筆,信手拈來了。 傳統的FPGA+AD/DA獨立器件搭建的數字系統我就不過多的介紹,今天我主要給大家講講RF-FPGA芯片給整個窄帶系統帶來的諸多優勢,真的是不用不知道,用了都說好!!!

1)高速數字處理

早先的無線電接收系統,利用模擬混頻器和級聯數字下變頻器(DDC)的設計結構,將信號降頻至基帶以供處理,該系統中會涉及到大量硬件(模擬混頻)和電源(模擬域和ASIC/FPGA中的DDC域)。 RF-FPGA的出現,使得DDC可以在RF-FPGA內部的RFADC硬核高速運行,處理的功效要高得多。

2)通過AXI-STEAM接口互聯

國產新一代RF-FPGA集成了RFADC,不需要ADC和FPGA之間的高速JESD204或者LVDS接口。直接通過內部并行接口AXI-STEAM接口互聯,最大500MHz時鐘周期,256位的并行接口。 整個數字接收系統節省了大量的功耗和PCB面積,同時也減小了JESD204的接口的延時。

3)可擴展的硬件設計平臺

在硬件設計方面,數字DDC的使用提供了更高的靈活性。系統設計人員現在可以平臺化ADC和FPGA相關硬件設計,然后只需進行細微的變更,重新配置系統軟件便可適應不同的帶寬,這也是未來軟件無線電的主要方向。 例如,一個無線電系統既可設計為全帶寬射頻直采ADC系統,也可設計為中頻采樣ADC系統。唯一的系統變更將是在RF側,針對IF ADC可能需要增加極少的混頻。 上述絕大部分系統變更都可以在軟件中進行,ADC + FPGA硬件設計可以基本保持不變,FPGA工程師配置ADC以支持新的帶寬。這就形成了一個標準平臺化硬件設計,其可以適用于許多平臺,軟件要求是其唯一變數。

4)通信接收機設計更加靈活

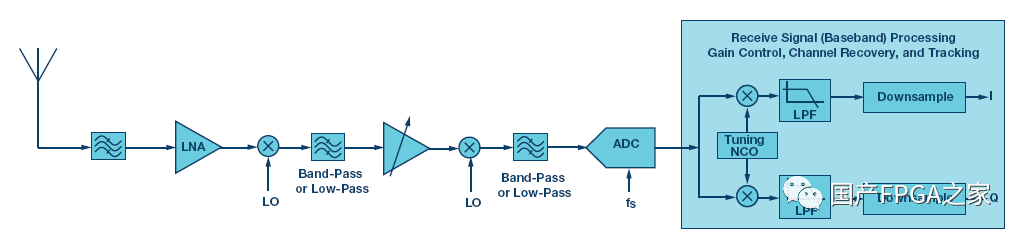

一個非常常見的ADC使用案例是通信接收機系統設計。關于軟件定義無線電(SDR)和采用ADC的通信接收機已有許多文獻,小弟這里就不展開討論。圖1為較早一代無線電接收機的功能框:

圖1-用于無線電的寬帶數字接收機 無線電接收機的一般規格要求ADC的噪聲頻譜密度(NSD)至少為153 dBFS/Hz或更佳。眾所周知,NSD與ADC的SNR存在如下關系: NSD = SNR + 10 log10 (Fs ÷ 2) 其中:NSD為ADC噪聲譜密度、SNR的單位為dBFS、Fs為ADC采樣率

4.1 常規軟件無線電設計

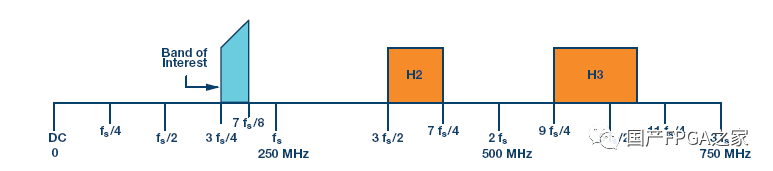

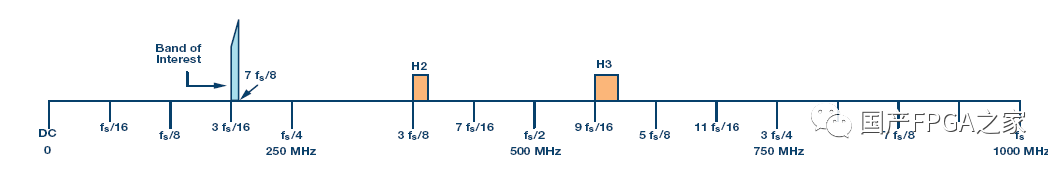

為了正確地對50MHz頻段進行數字化,ADC 將需要至少5倍的采樣帶寬,即至少約250MHz。將這些數值代入上式,ADC達到–153dBFS/Hz NSD要求所需的SNR約為72dBFS。 圖2顯示了利用250MSPS ADC對50MHz頻段有效采樣所采用的頻率規劃,該圖還顯示了二次和三次諧波頻段的位置。

圖2-采用250MSPS ADC的50MHz寬帶無線電的頻率規劃

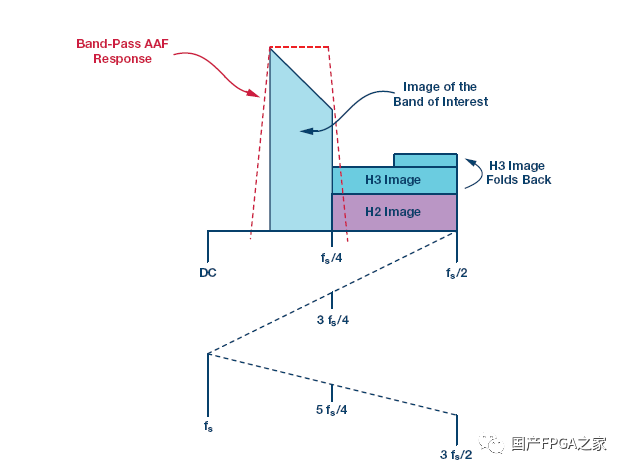

ADC采樣的頻率都會落在ADC的第一奈奎斯特(DC–125MHz)頻段。這種現象稱為混疊,因此這些頻率包括目標頻段、折回或混疊到第一奈奎斯特頻段的二次和三次諧波,如圖3所示,說明如下:

圖3-顯示在第一奈奎斯特區中的可用頻段,含二次和三次諧波

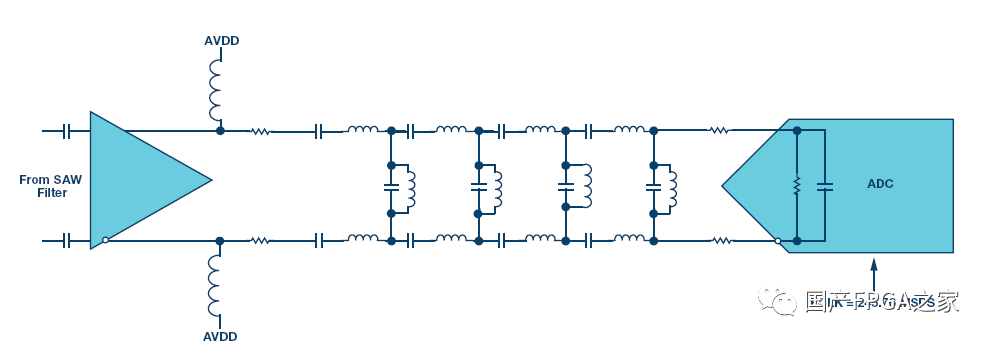

除NSD規格外,GSM、LTE和LTE-A等蜂窩通信標準還對SFDR (無雜散動態范圍)有其它嚴格要求,這給前端設計帶來了很大壓力。對目標頻段中的信號進行采樣時,前端能夠衰減干擾信號。 常規無線電前端設計的SFDR規格,即抗混疊濾波器要求很難達到。滿足SFDR要求的最佳抗混疊濾波器(AAF)解決方案是采用帶通濾波器。 通常,此類帶通濾波器為五階或更高階。一款可以滿足此類應用的SNR (或NSD)和SFDR要求的合適ADC是16位250 MSPS模數轉換器AD9467,采用AD9467的蜂窩無線電應用前端設計將圖4所示:

圖4-包括放大器、抗混疊濾波器和250 MSPS ADC的前端設計

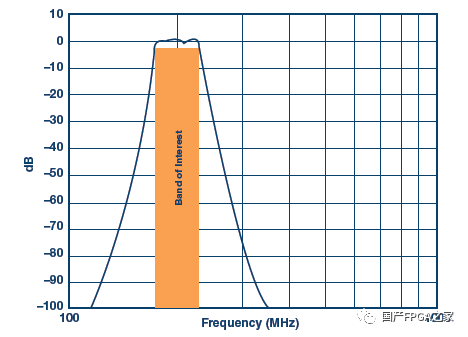

滿足SFDR要求的AAF的頻率響應如圖5所示:

圖5-包括放大器、抗混疊濾波器和250 MSPS ADC的帶通響應

此系統的實現不是不可能,但存在很多設計難題。因為帶通濾波器涉及到大量器件,是最難實現的濾波器之一。而且相關器件的選擇非常重要,任何不匹配都會導致ADC輸出中出現不需要的雜散(SFDR)。 除了非常復雜以外,任何阻抗不匹配都會影響濾波器的增益平坦度。為了優化該濾波器設計以滿足帶通平坦度和阻帶抑制要求,需要做相當多的設計工作。 雖然這種無線電設計的前端實現很復雜,但它確實有效,然而,系統實現因為下列原因而變得復雜:

濾波器設計;

FPGA必須提供專用JESD204B/LVDS端口來捕捉數據,這會使PCB設計復雜化;

FPGA還需要留出一些處理能力來進行數字信號處理。

4.2 RF-FPGA簡化并加速設計

RF-FPGA中RFADC硬核采樣頻率最大能到4.6GHz,對于50MHz帶寬信號,利用過采樣技術,然后抽取平均降低底噪,以改善動態范圍。 對系統設計人員來說,這意味著實現起來很簡單,并可獲得其它靈活性。由于該ADC的采樣頻率(1GHz)是上述例子(250MHz)的4倍,RF采樣ADC奈奎斯特區的頻率規劃要簡單得多,如圖6所示:

圖6-采用1GSPS ADC的50MHz寬帶無線電的頻率規劃

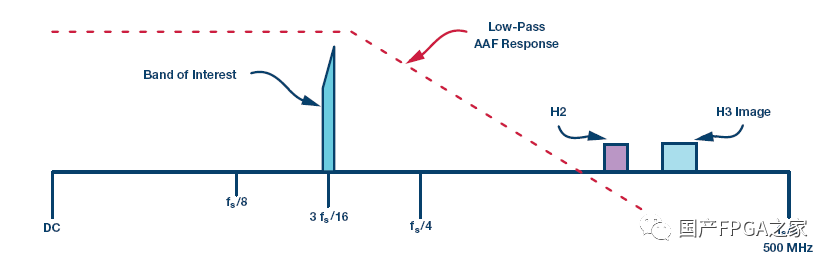

從頻率規劃可知,它實現起來要比圖2所示的設計簡單得多。AAF要求也有所降低,如圖7所示。這種方法的思想是使用簡單的模擬前端設計,而把數字處理模塊留在RF直采ADC內以執行繁重的信號處理。

圖7-1GSPS ADC的AAF

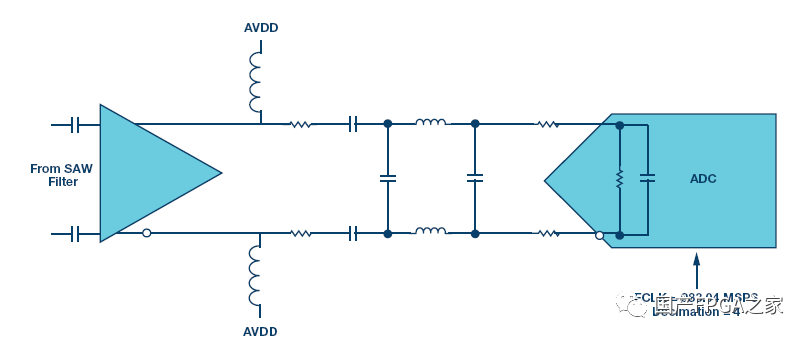

過采樣的好處是將該頻率規劃擴展到整個奈奎斯特區,即比250MSPS奈奎斯特區大4倍的區域。這樣就大大降低了濾波要求,一個簡單的三階低通濾波器就足夠,而無需250MSPS ADC方案所用的帶通濾波器。采用RF采樣ADC的簡化AAF實現方案如圖8所示:

圖8-包括放大器、抗混疊濾波器和1GSPS ADC的前端設計

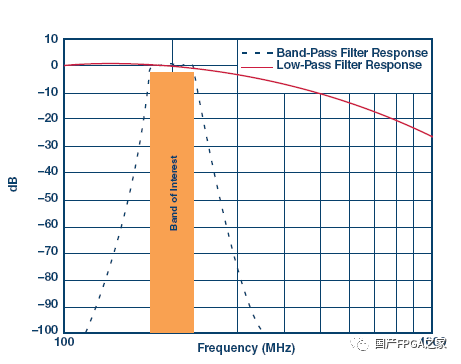

圖9所示為上述系統低通濾波器響應性能,同時顯示了帶通濾波器以作比較。

圖9-250MSPS ADC和1GSPS ADC的AAF比較

從上述AAF對比結果來看,低通濾波器的帶通平坦度更佳,而且就器件不匹配而言,1GSPS ADC系統更容易管理,其阻抗匹配也更容易實現。 此外,由于器件數量更少,系統成本也更低,簡化的前端設計可縮短設計時間。同時每4倍過采樣率時,通過平均還可以獲得6dB的額外處理增益,提高一位有效位數。

戰術總結

隨著RF-FPGA的到來,必然會給傳統的窄帶、寬帶的收發系統設計帶來變革,小弟私以為,對于新技術和新產品的到來,我們要時刻保持謙虛包容的態度,積極地去學習和接納。畢竟身處在這么卷的行業賽道里,不努力學習,可能明天就要到別人的廠子里應聘保安了。

審核編輯:湯梓紅

-

FPGA

+關注

關注

1629文章

21729瀏覽量

603027 -

接口

+關注

關注

33文章

8580瀏覽量

151029 -

adc

+關注

關注

98文章

6496瀏覽量

544477 -

RF

+關注

關注

65文章

3051瀏覽量

166970 -

窄帶系統

+關注

關注

0文章

2瀏覽量

1339

原文標題:窄帶系統設計中,RF-FPGA優勢何在?

文章出處:【微信號:國產FPGA之家,微信公眾號:國產FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

基于全光矢量調制技術的超寬帶光載無線系統及其關鍵技術分析介紹

GPS芯片的關鍵技術是什么

什么是RF MEMS?有哪些關鍵技術與器件?

FPGA+DSP導引頭信號處理中FPGA設計的關鍵技術

FPGA+DSP導引頭信號處理中FPGA設計的關鍵技術

基于國產RF-FPGA寬帶射頻采集卡

數字收發組件的關鍵技術 RF-FPGA芯片在窄帶系統設計中的優勢

數字收發組件的關鍵技術 RF-FPGA芯片在窄帶系統設計中的優勢

評論