PCIe最初被稱為HSI(用于高速互連),并在最終確定其PCI-SIG名稱PCI Express之前,將其名稱更改為3GIO(第三代I / O)。名為阿拉帕霍工作組(AWG)的技術(shù)工作組制定了該標(biāo)準(zhǔn)。對(duì)于初稿,特設(shè)工作組只包括英特爾工程師; 隨后特設(shè)工作組擴(kuò)大到包括行業(yè)伙伴。PCI Express是一項(xiàng)不斷發(fā)展和完善的技術(shù).

“速度得用金錢來換,因此我們?cè)谶~向更高信號(hào)速率的同時(shí),會(huì)看到有多少人愿意為此付出代價(jià),以及他們會(huì)怎么做。”好消息是,PCIe將按照時(shí)程在年底完成0.71版的批準(zhǔn),將提供高達(dá)256GB/s 的速率;這距離16 GT/s速率的4.0版PCIe問世還不到兩年。加速PCIe發(fā)展藍(lán)圖的主要推手是云端運(yùn)算需求;而PCIe以往是每3~4年,甚至是7年會(huì)將數(shù)據(jù)傳輸速率提升一倍。數(shù)據(jù)中心網(wǎng)絡(luò)需要更快的速度以過渡至800Gbit以太網(wǎng)絡(luò),而數(shù)量越來越龐大的深度學(xué)習(xí)加速器,也感覺它們需要更高速度.

淺談PCIe傳輸速率和有效帶寬計(jì)算方式

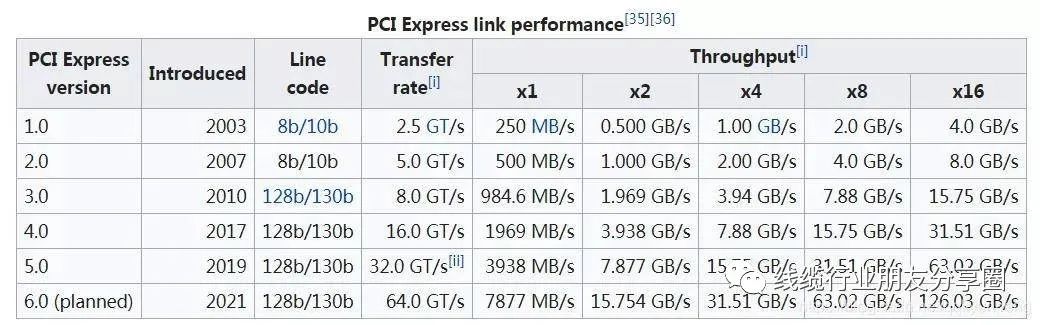

PCIe是串行總線,PCIe1.0的線上比特傳輸速率為2.5Gb/s,物理層使用8/10編碼,即8比特的數(shù)據(jù),實(shí)際在物理線路上是需要傳輸10比特的,因此:

PCIe1.0 x 1的帶寬=(2.5Gb/s )/ 10bit =250MB/s

這是單條Lane的帶寬,有幾條Lane,那么整個(gè)帶寬就是250MB乘以Lane的數(shù)目。

PCIe2.0的線上比特傳輸速率在PCIe1.0的基礎(chǔ)上翻了一倍,為5Gb/s,物理層同樣使用8/10編碼,所以:

PCIe2.0 x 1的帶寬=(5Gb/s )/ 10bit = 500MB/s

同樣,有多少條Lane,帶寬就是500MB/s乘以Lane的數(shù)目。

PCIe3.0的線上比特傳輸速率沒有在PCIe2.0的基礎(chǔ)上翻倍,不是10Gb/s,而是8Gb/s,但物理層使用的是128/130編碼進(jìn)行數(shù)據(jù)傳輸,所以:

PCIe3.0 x 1的帶寬=(8Gb/s)/ 8bit = 1GB/s

同樣,有多少條Lane,帶寬就是1GB/s乘以Lane的數(shù)目。

由于采用了128/130編碼,128比特的數(shù)據(jù),只額外增加了2bit的開銷,有效數(shù)據(jù)傳輸比率增大,雖然線上比特傳輸率沒有翻倍,但有效數(shù)據(jù)帶寬還是在PCIe2.0的基礎(chǔ)上做到翻倍。

這里值得一提的是,上面算出的數(shù)據(jù)帶寬已經(jīng)考慮到8/10或者128/130編碼,因此,大家在算帶寬的時(shí)候,沒有必要再考慮線上編碼的問題了。

和SATA單通道不同,PCIe連接可以通過增加通道數(shù)擴(kuò)展帶寬,彈性十足。通道數(shù)越多,速度越快。不過,通道數(shù)越多,成本越高,占用更多空間,還有就是更耗電。因此,使用多少通道,應(yīng)該在性能和其他因素之間進(jìn)行一個(gè)綜合考慮。

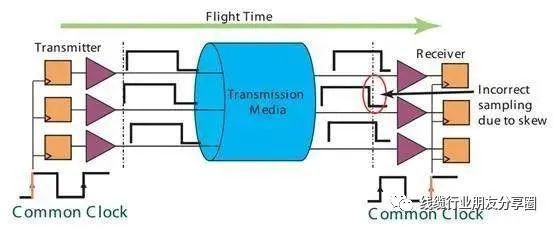

PCIe是從PCI發(fā)展過來的,PCIe的”e”是express的簡(jiǎn)稱,快的意思。PCIe怎么就能比PCI快呢,因?yàn)镻CIe在物理傳輸上,跟PCI有著本質(zhì)的區(qū)別。PCI使用并口傳輸數(shù)據(jù),而PCIe使用的是串口傳輸。PCI并行總線,單個(gè)時(shí)鐘周期可以傳輸32bit或者64bit,怎么就比不了你單個(gè)時(shí)鐘周期傳輸1個(gè)bit數(shù)據(jù)的串行總線呢。在實(shí)際時(shí)鐘頻率比較低的情況下,并口因?yàn)榭梢酝瑫r(shí)傳輸若干比特,速率確實(shí)比串口快。隨著技術(shù)的發(fā)展,數(shù)據(jù)傳輸速率要求越來越快,要求時(shí)鐘頻率也越來越快,但是,并行總線時(shí)鐘頻率不是想快就能快的。如下圖所示:

在發(fā)送端,數(shù)據(jù)在某個(gè)時(shí)鐘沿傳出去(左邊時(shí)鐘第一個(gè)上升沿),在接收端,數(shù)據(jù)在下個(gè)時(shí)鐘沿(右邊時(shí)鐘第二個(gè)上升沿)接收。因此,要在接收端能正確采集到數(shù)據(jù),要求時(shí)鐘的周期必須大于數(shù)據(jù)傳輸?shù)臅r(shí)間(從發(fā)送端到接收端)。受限于數(shù)據(jù)傳輸時(shí)間(該時(shí)間還隨著數(shù)據(jù)線長(zhǎng)度的增加而增加),因此時(shí)鐘頻率不能做得太高。另外,時(shí)鐘信號(hào)在線上傳輸?shù)臅r(shí)候,也會(huì)存在相位偏移(clock skew ),影響接收端的數(shù)據(jù)采集。

PCIe使用串行總線進(jìn)行數(shù)據(jù)傳輸就沒有這些問題。它沒有外部時(shí)鐘信號(hào),它的時(shí)鐘信息通過8/10編碼或者128/130編碼嵌入在數(shù)據(jù)流,接收端可以從數(shù)據(jù)流里面恢復(fù)時(shí)鐘信息,因此,它不受數(shù)據(jù)在線上傳輸時(shí)間的限制,你導(dǎo)線多長(zhǎng)都沒有問題,你數(shù)據(jù)傳輸頻率多快也沒有問題;沒有外部時(shí)鐘信號(hào),自然就沒有所謂的clock skew問題.

淺談PCIe線材結(jié)構(gòu)

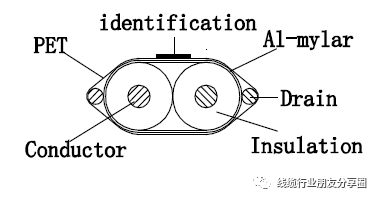

PCIe為串行,通過使用差分信號(hào)傳輸(differential transmission),信號(hào)完整性理論之差分訊號(hào);采用雙通道技術(shù),在傳輸模式上,PCI-Express采用與全雙工通信技術(shù)類似的雙通道傳輸模式,在速度方面,PCI-Express v1.0a 為每個(gè)通道提供了2.5Gb/s的傳輸速率,隨著版本的不同,面向PCI Express擴(kuò)展卡應(yīng)用的線纜組件可提供PCIe X4、X8和X16等規(guī)格,該系列線纜組件包含MiniSAS、SATA、QSFP +和SPF +等高速線纜。PCIE物理層實(shí)現(xiàn)了一對(duì)收發(fā)差分對(duì),可以實(shí)現(xiàn)全雙工的通訊方式,目前主要的PCIE結(jié)構(gòu)主要是SAS結(jié)構(gòu),線材選用CAT A ,B,C ,D,E結(jié)構(gòu),根據(jù)測(cè)試的參數(shù)要求,設(shè)計(jì)符合不同規(guī)范的參數(shù)。

PCIe Spec只是規(guī)定了物理層需要實(shí)現(xiàn)的功能、性能與參數(shù)等,置于如何實(shí)現(xiàn)這些卻并沒有明確的說明。也就是說,廠商可以根據(jù)自己的需要和實(shí)際情況,來設(shè)計(jì)PCIe的物理層結(jié)構(gòu)來保證功能即可!

-

帶寬

+關(guān)注

關(guān)注

3文章

928瀏覽量

40919 -

傳輸

+關(guān)注

關(guān)注

0文章

153瀏覽量

27459 -

PCIe

+關(guān)注

關(guān)注

15文章

1238瀏覽量

82638

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

MINI PCIE連接器插槽傳輸速率的特點(diǎn)

FPI10015 PCIe連接器,連接更穩(wěn)定,滿足高速率傳輸設(shè)備互連需求

PCIe數(shù)據(jù)傳輸協(xié)議詳解

如何選擇適合的PCIe配置

PCIe 4.0與3.0的區(qū)別 PCIe設(shè)備的故障排除方法

pcie 4.0與pcie 5.0的區(qū)別

pcie帶寬對(duì)計(jì)算性能的影響

如何檢查pcie插槽兼容性

pcie接口類型及其應(yīng)用

LORA模塊的數(shù)據(jù)傳輸速率

PCIe 5.0 SerDes 測(cè)試

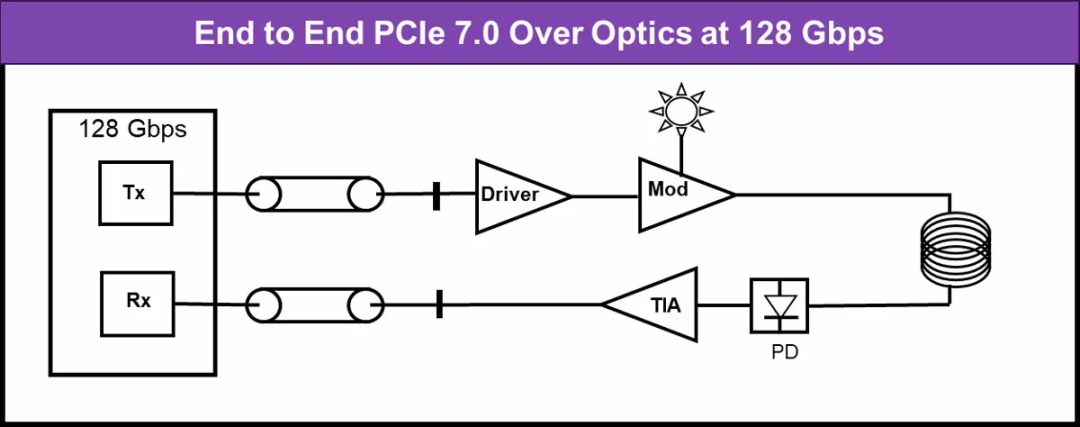

PCIe光傳輸的優(yōu)勢(shì)與挑戰(zhàn)

pcie4.0和pcie3.0接口兼容嗎

三種實(shí)現(xiàn)光模塊更高傳輸速率的技術(shù)

PCIE相關(guān)概念和帶寬計(jì)算方法

PCIe傳輸速率和有效帶寬科普

PCIe傳輸速率和有效帶寬科普

評(píng)論