前情提要

最近看到一個關于上下拉電阻的問題,發現不少人認為上下拉電阻能夠增強驅動能力。隨后跟幾個朋友討論了一下,大家一致認為不存在上下拉電阻增強驅動能力這回事,因為除了OC輸出這類特殊結構外,上下拉電阻就是負載,只會減弱驅動力。但很多經驗肯定不是空穴來風,秉承工程師的鉆研精神,我就試著找找這種說法的來源,問題本身很簡單,思考的過程比較有趣。

二極管邏輯

今天已經很難看到二極管邏輯電路了,其實用性也不算高,不過因為電路簡單,非常適合用來理解基本概念。

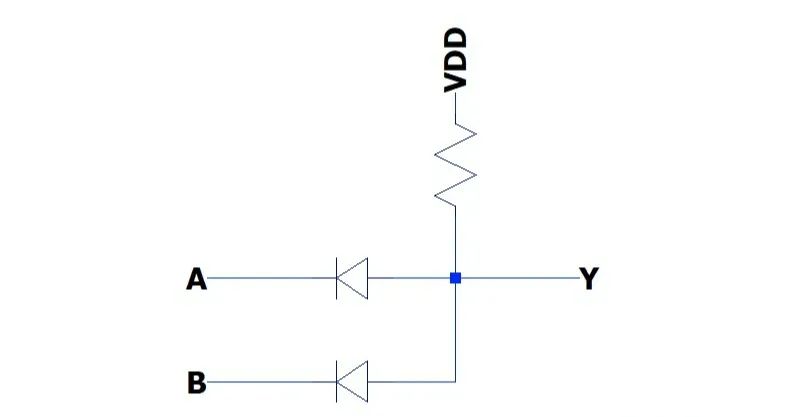

一個最簡單的二極管與門如下圖。與門實現邏輯與操作Y=A&B,即A或者B任意為L的時候,輸出Y為L,只有當A和B都為H時,Y才為H。

基本二極管與門

假設二極管無導通壓降,在這個電路中,二極管充當了單向開關的角色,當A和B等于VDD時,兩根二極管反向截至,Y被電阻上拉到VDD,這是Y就是H;當A或者B任意一端為GND時,二極管導通,因為二極管導通時電阻很小,遠小于上拉電阻,所以Y被拉到了GND,即邏輯L。

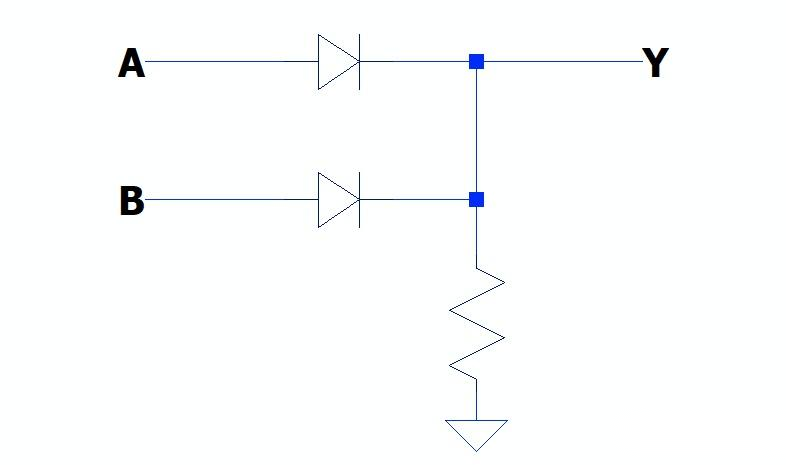

至于二極管或門,只要把二極管轉一下,再把電阻從拉到VDD改成拉到GND就可以了,非常簡單。

基本二極管或門

基本原理

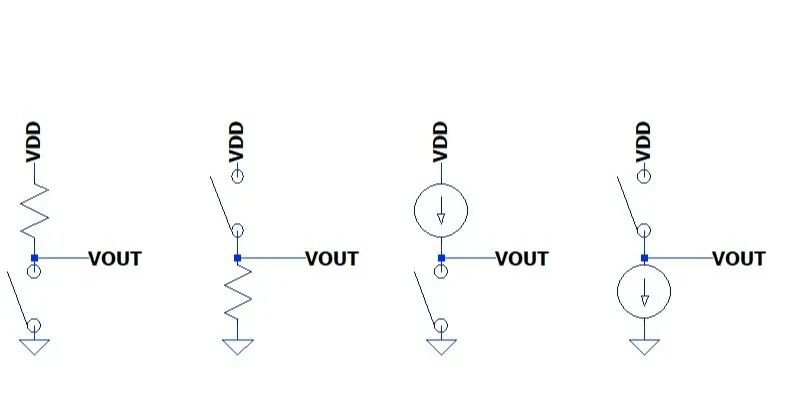

你看,在這么原始的邏輯電路中就已經出現了上下拉電阻,這里面的原理也非常簡單粗暴:利用開關的閉合(電阻為0)和開啟(電阻無窮大)的特性,配合電阻,就可以輕松實現兩種電壓的輸出。這種電路還有一個變形,就是用恒流源取代電阻,一方面集成電路工藝,恒流源比電阻更容易獲得,另一方面恒流源的驅動能力也更好。根據開關和電阻(或恒流源)的相對位置,有以下基本電路:即開關接到GND(L)或開關接到VDD(H)。

幾種開關電路接法

這幾種電路都是由開關的閉合或開啟決定了VOUT是VDD還是GND。開關的相對位置不同,還決定了電路在某一狀態下的驅動能力:開關的導通電阻為0,可視為驅動力無窮大,可是電阻(或恒流源)的驅動能力呢,只有VDD/R(或者恒流I),這就導致了電路在輸出H或L的時候驅動能力不對稱(換一個說法,就是電路在輸出H或者L的時候,輸出阻抗不一樣)。

除了驅動能力的問題,這種單開關加電阻的模式還會帶來靜態功耗的問題,因為只要開關閉合,不管外部有沒有負載,都會消耗電流。

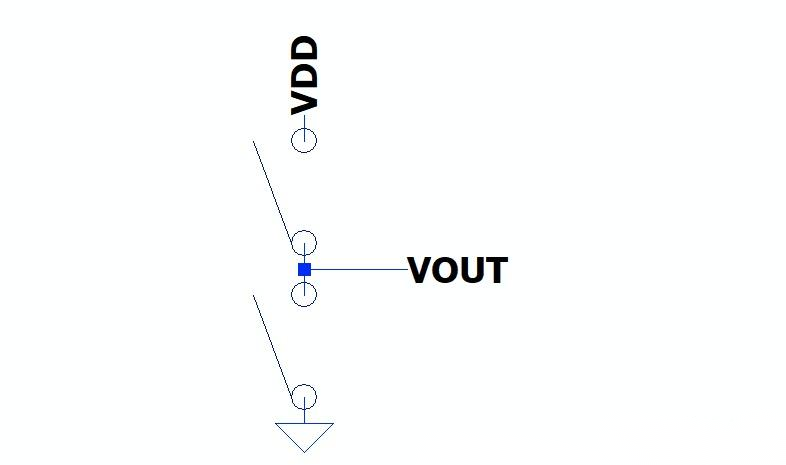

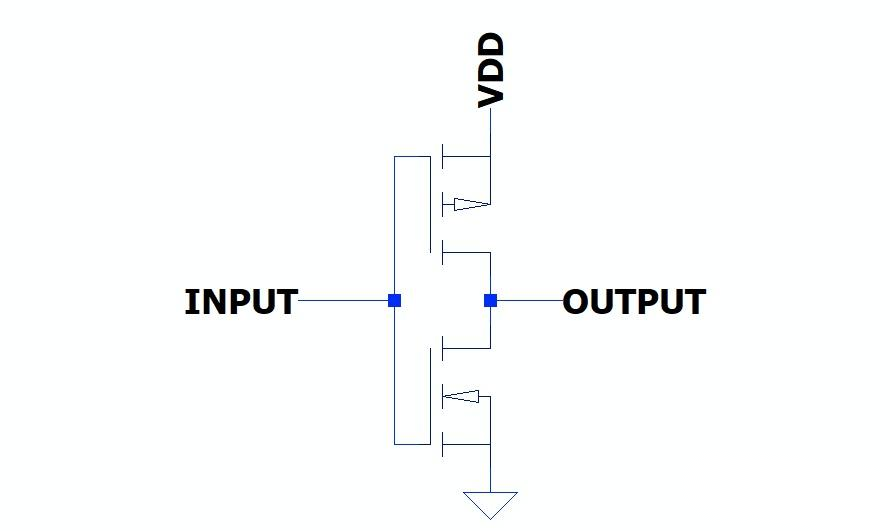

既然開關的驅動力比電阻強,那么能不能把電阻也換成開關?恭喜你,發現了現代CMOS邏輯電路的基本單元:倆互補的開關。這樣不管輸出H還是輸出L,驅動能力都是無窮大!好的,這時候上下拉電阻就不見了。

這樣兩個開關的電路還多出來了一種狀態:當兩個開關都開啟時,VOUT即不是VDD也不是GND,而是一個懸空的狀態(即高阻態,Hi-Z),這時候外部給什么信號它就是什么狀態。這樣又出現了一個新的邏輯門大類:三態邏輯門。

互補開關電路

上下拉電阻增強驅動能力?

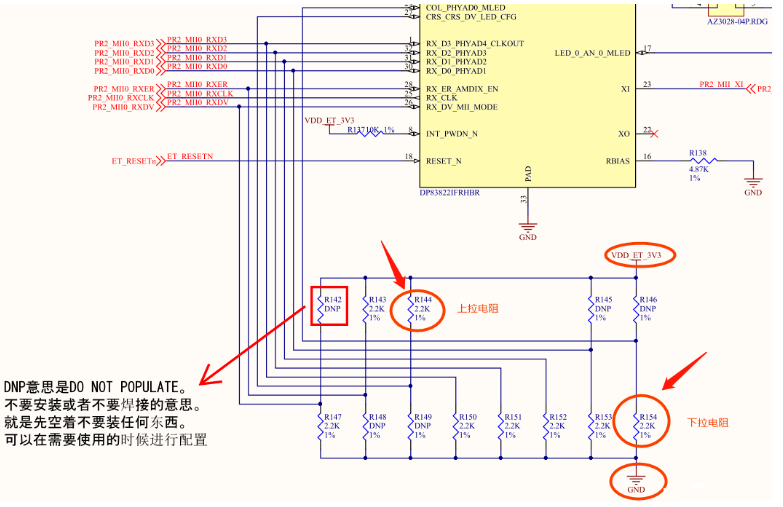

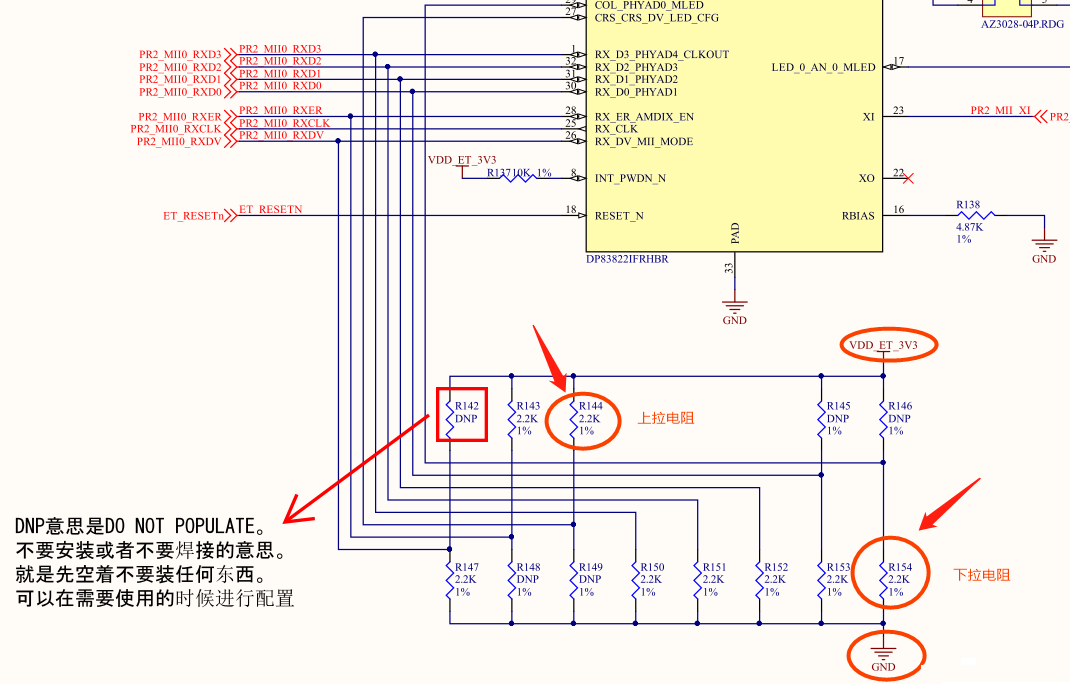

很多經驗不是空穴來風,只是在流傳的過程中丟失了重要的前提條件。上一節也看到了有一些邏輯器件,他們輸出高和輸出低時的驅動能力差別很大。

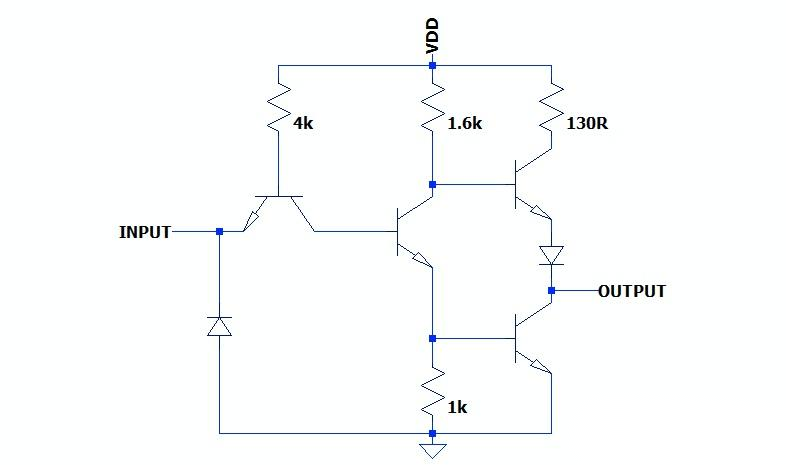

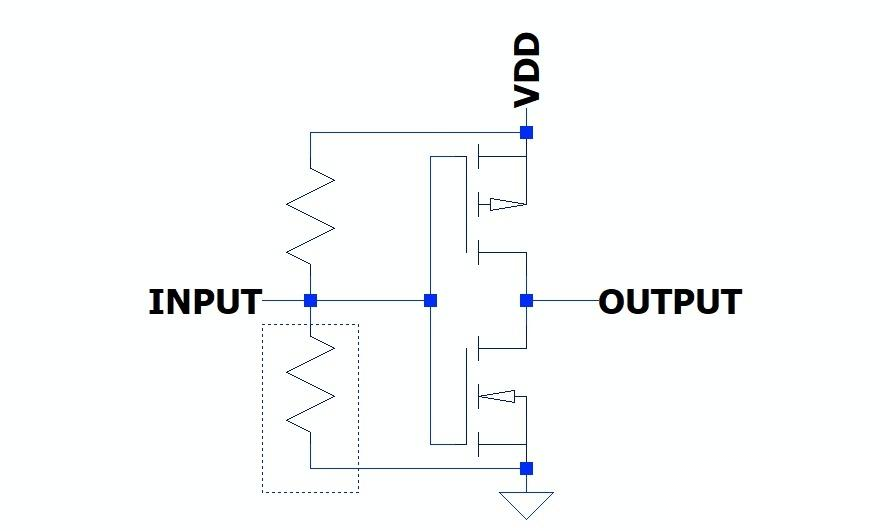

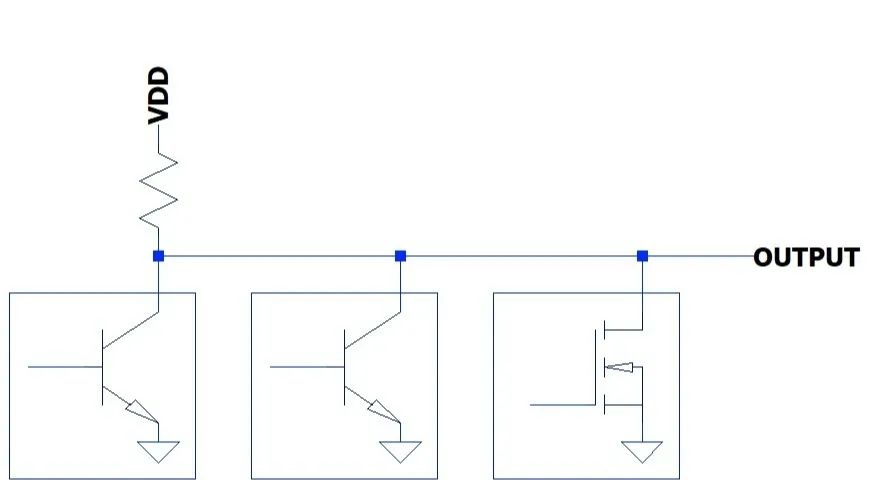

TTL(70xx、74Fxx、74Sxx、74LSxx等)家族的器件就屬于這種類型,如下圖是7404(TTL反相器)的原理圖,由于非對稱的輸出級設計,輸出為高時驅動能力只有0.4mA,而輸出低時居然能輸出16mA的電流(手冊中的輸出電流不是晶體管或者電路本身的極限,而是超過這個電流以后,輸出的電壓可能無法滿足邏輯族的要求)。

7404的簡化電路

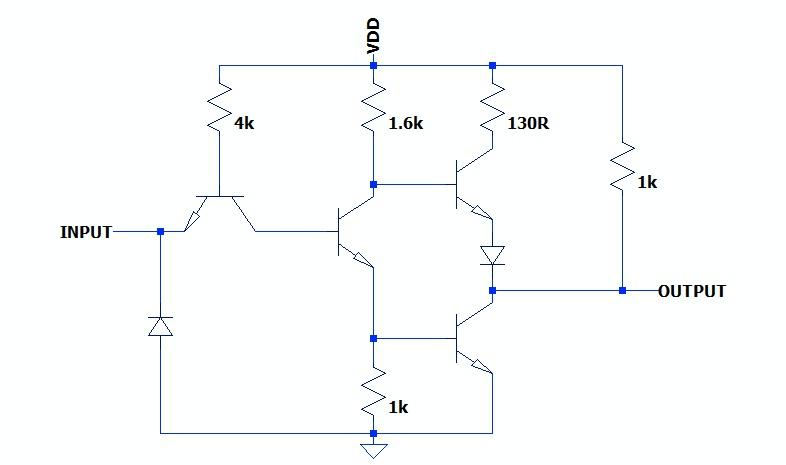

這個時候在輸出端口外加一個上拉電阻,就可等效以增強端口在輸出H時的驅動能力,但代價是端口輸出L時,驅動能力相應地減弱,不過這時候芯片輸出能力足夠強,用這點代價來換取另一個狀態下驅動能力的增強,還是劃算。

帶上拉電阻的7404

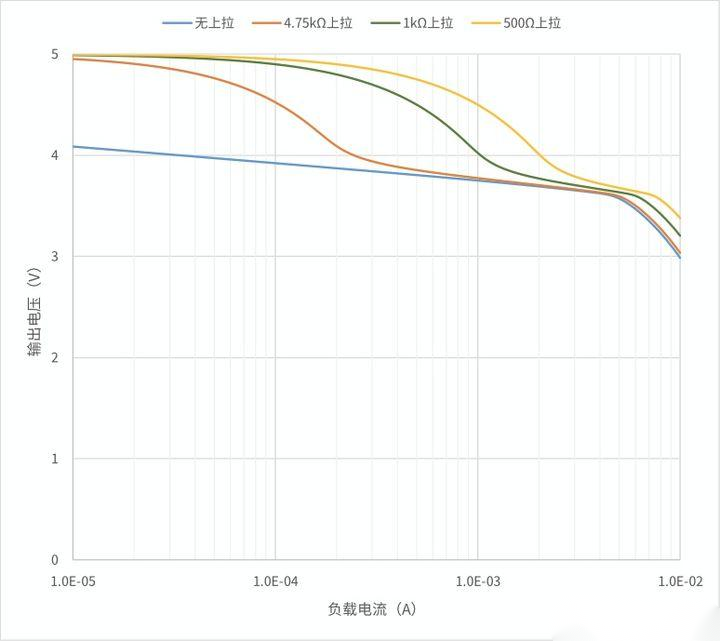

下表是仿真有無上拉電阻時,負載電流與輸出電壓的關系,可以看到上拉電阻確實增強了在一定負載下的輸出電壓,不過當負載電流較大時效果并不明顯,而且邊際效應也很顯著,當上拉電阻減小到一定程度以后,增強效果也不太顯著,而且會大大增加靜態功耗。

帶不同上拉電阻的7404輸出電壓與負載電流的關系

既然非對稱的輸出級有這樣的問題,那為啥不能把這個驅動器設計成上下對稱的呢?

一方面,如果要設計成上下對稱的結構,上管需要用P管,而當時的工藝限制,P管各方面性能都不如N管,速度、功耗和成本都不是很劃算,所以能看到很多上年代的芯片,內部幾乎沒有P管(包括MOS工藝的器件也是)。

另一方面,TTL輸入結構的特點,輸入為H時所需電流很小,而輸入為L所需的輸入電流很大,這樣對輸出L時的驅動能力要求就很高,反而對輸出H時沒有驅動能力要求(TTL輸入懸空時等效為H)。

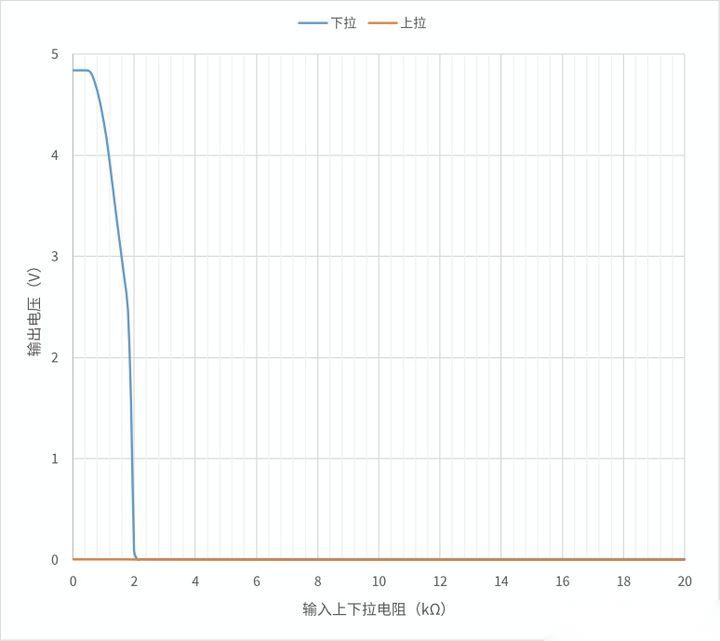

但TTL的這種特點,又會帶來一個比較麻煩的問題:下拉電阻值需要很大才能滿足要求,而下拉電阻太大則會導致輸出高時負載太重以至于無法達到規定電壓,所以TTL要盡量避免使用下拉。

下圖是仿真結果,因為這是一個反相器,所以下拉時輸出高是所期望的,而下拉電阻超過1.8kΩ時已經無法滿足TTL定義的最低高電平標準了;而上拉時,就算上拉電阻達到20kΩ,也絲毫不影響輸出。

TTL上下拉電阻取值與輸出電壓的關系

CMOS電路

相信現在已經沒多少人會在設計時選用TTL家族的器件了,可能多數人都沒接觸過這類器件,最常用的還是CMOS家族(HC、HCT、LVC、CD4000等)。

CMOS家族的東西就比較簡單粗暴,上下對稱的結構,上下管驅動能力也基本一致,這個時候輸出的上下拉電阻對增強驅動能力幾乎沒有幫助不說,還加重了負載,屬于得不償失(其實多數情況下是無關痛癢)。

下圖是基本的CMOS反相器,只需要一對互補的MOS管即可實現(現實中的CMOS反相器一般是三對這種管子級聯出來的,為了提高開環增益)。

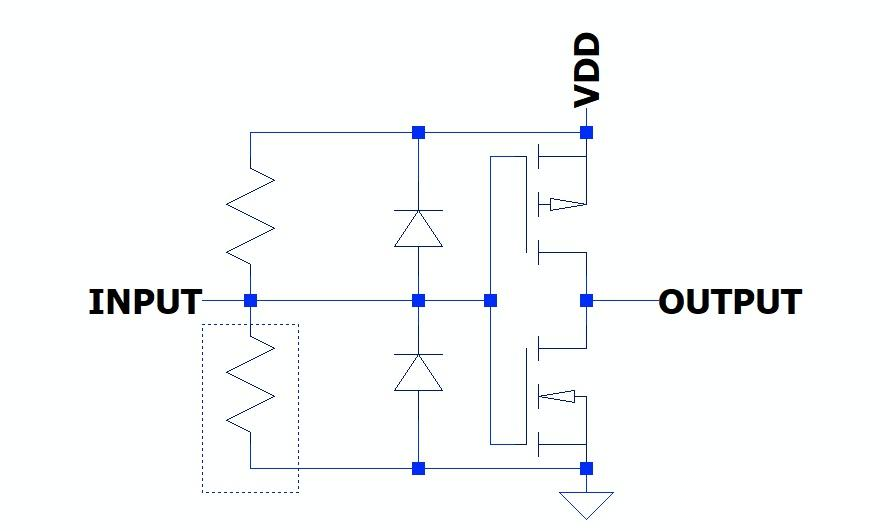

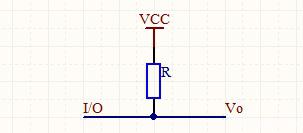

但是CMOS器件的輸入懸空時,不會被拉向任何一個方向,處于一種浮空的狀態,這樣會造成輸出紊亂,不是我們所希望的結果,這種情況下需要在輸入端接入上拉或者下拉電阻給電路提供一個確定的狀態。一般可拔插的對外接口(如JTAG)需要在I/O上加上上下拉電阻,有三態的總線視工作情況也可能需要上下拉,不過大多數的CMOS電路不需要額外的上下拉電阻。

CMOS器件在使用一般要加上下來避免輸入懸空

因為CMOS輸入是電壓控制型,輸入阻抗很高,所以上下拉電阻的值可以很大,理論上用MΩ級別的電阻都沒問題。

不過理論歸理論,工程師得認清現實。現實的CMOS輸入結構,為了保護MOS管的柵極,會在柵極上加入ESD二極管,二極管反向偏置的時候是有漏電流的,還會隨溫度的升高還會指數增長!所以CMOS電路的上下拉電阻一般在100kΩ以下,一些制程比較先進的CPU,I/O口的漏電流或者上下拉電流較大,上下拉電阻一般取在幾kΩ級別。所以設計上下拉電阻前一定要仔細閱讀芯片手冊,查查I/O的輸入電流,看看取什么樣的電阻值才合理。

CMOS輸入有ESD二極管

其他需要上下拉的情況

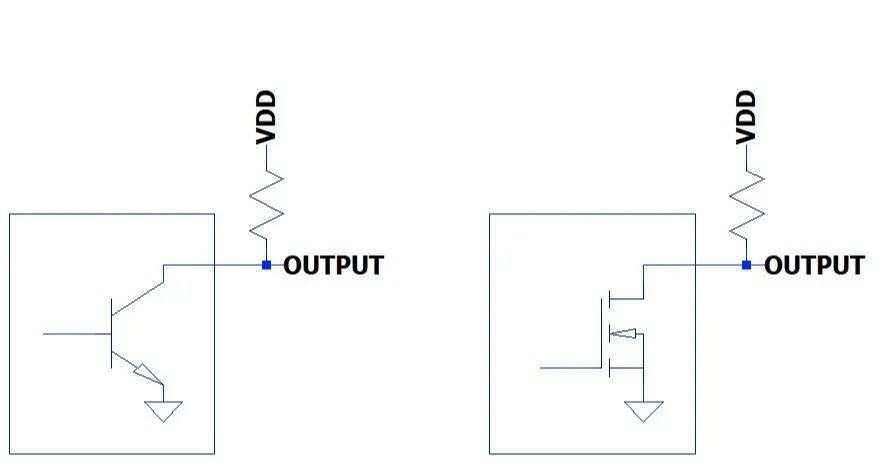

開集(Open-Collector)和開漏(Open-Drain)的輸出結構往往也需要加上拉電阻。OC和OD輸出結構只有下管,所以只能輸出L和高阻(Hi-Z)兩種狀態,而高阻態是難以被電路識別的,所以需要合適的上拉電阻把高阻態轉變為高態。

OC(左)和OD(右)輸出結構

雖然OC和OD輸出結構看起來很復古,使用時也需要外接電阻有點麻煩,但這種結構最大的好處就是可以做線與,也就是多個OC或者OD可以接到一起,只要其中一個輸出L,總線就是L,這在多外設中斷和電源時序控制方面很常用。

OC/OD的線與接法

I2C也是OC/OD結構,這樣很輕松就能在一條數據線上雙向傳輸數據而不需要額外的方向控制信號,而CAN總線則巧妙地利用線與特性來實現總線仲裁。

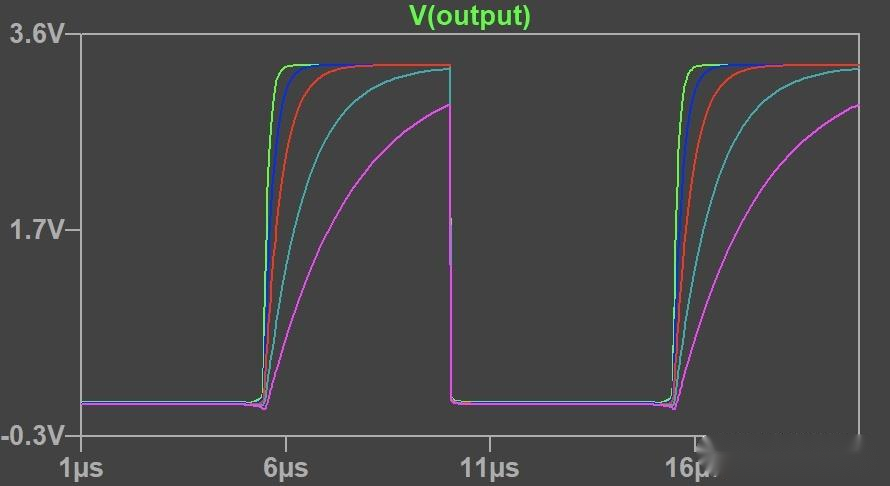

在處理OC或者OD電路的時候,一定要注意評估總線負載電容、上拉電阻與所需速度的關系,負載電容越大,速度越快,所需的上拉電阻要越小。比如I2C總線,如果只掛載了一片從設備,使用4.75kΩ的上拉電阻可能就滿足400kHz的總線要求了,但如果掛了10片從設備呢,1kΩ的上拉電阻也不一定能搞定100kHz的總線速度,這種時候可能得考慮總線負載隔離或者降低總線速度了。

下圖是在200pF負載電容情況下,上拉電阻為500Ω、1kΩ、2kΩ、4.75kΩ和10kΩ下的波形,可以看到上拉電阻越大,對電容充電速度越慢,所以上升沿也越慢,當上拉電阻不合適時上升沿已經嚴重變形,無法保證正常工作。

OC電路不同上拉電阻對波形的影響

冷知識

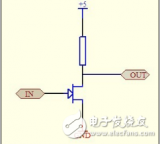

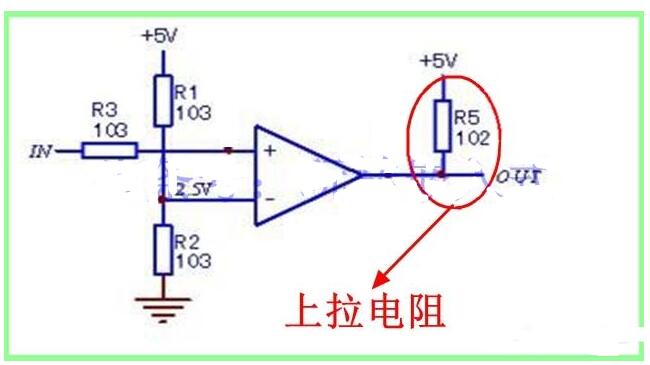

邏輯反相器可以當成放大器來用!不是開玩笑,我還真見過產品上用這種騷操作的,只需要把反相器接成反向放大器就可以了,不過邏輯器件當線性器件用,性能嘛...

邏輯反相器(非門)當成線性放大器用

-

二極管

+關注

關注

147文章

9631瀏覽量

166333 -

開關電路

+關注

關注

58文章

553瀏覽量

66396 -

上拉電阻

+關注

關注

5文章

359瀏覽量

30611 -

恒流源

+關注

關注

16文章

335瀏覽量

56202 -

GND

+關注

關注

2文章

539瀏覽量

38697

原文標題:一顆上拉電阻引發的思考

文章出處:【微信號:gh_a6560e9c41d7,微信公眾號:硬件筆記本】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

一顆上拉電阻引發的思考

一顆上拉電阻引發的思考

評論