作為集創賽(全國大學生集成電路創新創業大賽)和全國大學生FPGA競賽紫光同創賽道官方定制FPGA開發板,紫光同創大學計劃協同育人高校推薦開發板,盤古50K開發板已在100+所高校推廣使用。

這款基于紫光同創Logos系列PGL50H芯片的開發板,全面實現國產化方案,板載資源豐富,高容量、高帶寬,海量外圍接口,功能強大,可實現復雜項目的開發評估,滿足多方位的開發需求。

盤古50K開發板試用體驗

蔡工:紫光同創PGL50H開發板(盤古50K開發板)配套的資料包內容豐富,提供軟件安裝文件,提供詳細的軟件安裝方法文檔,初學者只需很短的時間就可以掌握Pango Design Suite開發平臺,極大增強了學習的信心。

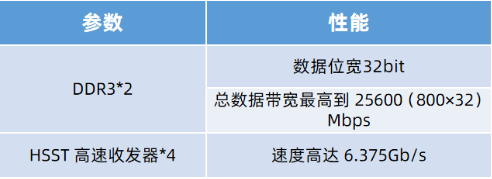

郭工:PGL50H在紫光同創Logos系列中具有不俗的性能表現,邏輯、RAM、IO資源都很充足。其和DDR3之間的數據交互時鐘頻率最高到400MHz,2顆DDR3的數據位寬為32bit,總數據帶寬最高到25600 (800×32)Mbps。同時,PGL50H FPGA 帶有4路HSST高速收發器,每路速度高達6.375Gb/s,非常適合用于光纖通信和PCle數據通信。

馬工:盤古50K開發板將紫光同創FPGA性能發揮到極致,可以進行復雜項目的開發評估,開發板功能強大,用料實足。

盤古50K開發板詳情

1.產品概述

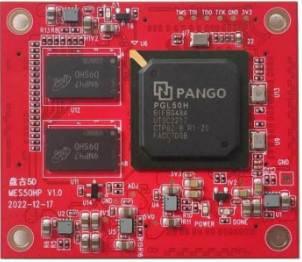

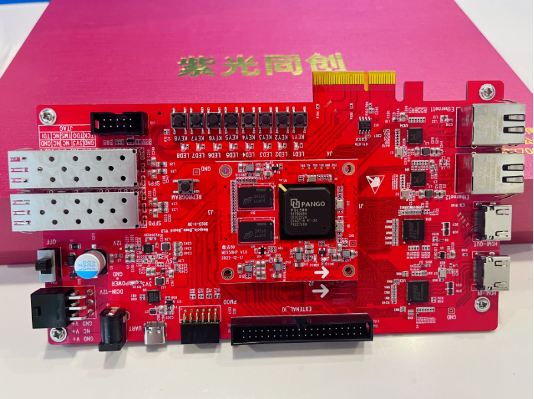

盤古50K開發板(紫光同創Logos系列PGL50H關鍵特性評估板)采用核心板+擴展板的結構,并使用高速板對板連接器進行連接。

核心板由 FPGA+2 顆 DDR3+Flash+電源及復位構成,承擔 FPGA 的最小系統運行及高速數據處理和存儲的功能。FPGA 選用紫光同創 40nm 工藝的 FPGA(logos 系列:PGL50H-6IFBG484)。PGL50H 和 DDR3 之間的數據交互時鐘頻率最高到 400MHz,2 顆 DDR3 的數據位寬為 32bit,總數據帶寬最高 25600(800×32)Mbps,充分滿足高速多路數據存儲的需求。

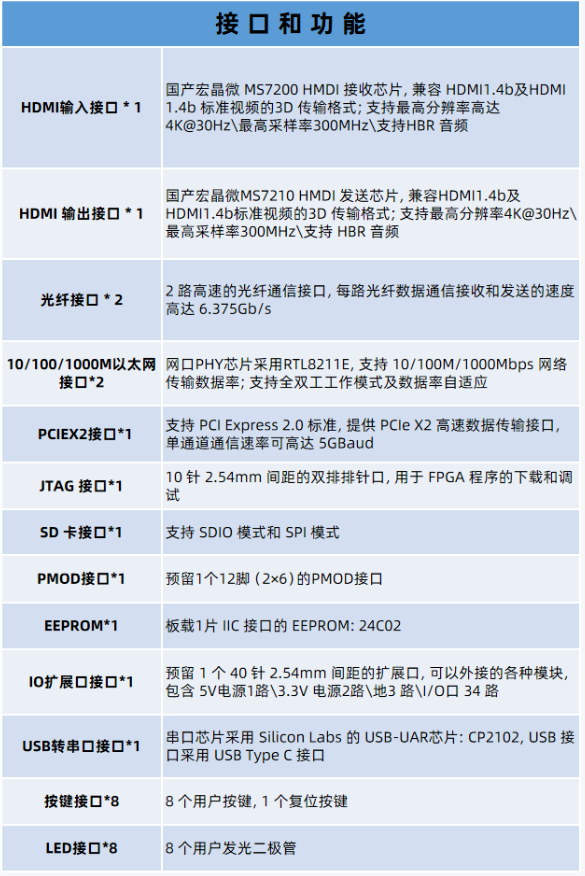

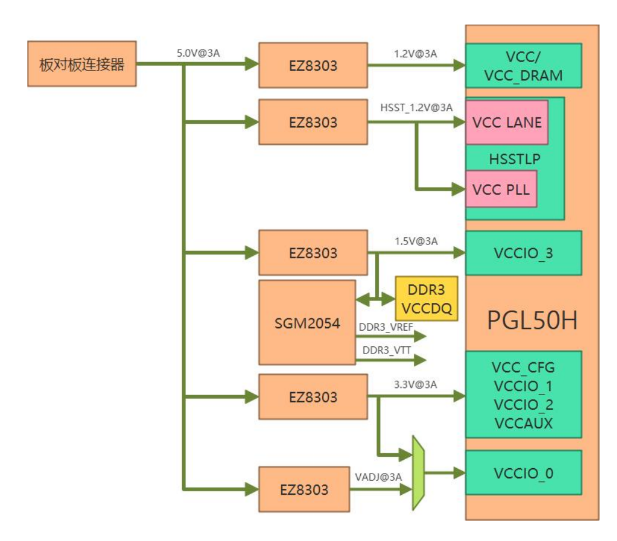

PGL50HFPGA帶有4路HSST高速收發器,每路速度高達 6.375Gb/s,適合用于光纖通信和PCIe數據通信;電源采用多顆 EZ8303(艾諾)產生不同的電源電壓。底板為核心板擴展豐富的外圍接口, 預留 HDMI 收發接口用于圖像驗證及處理;預留的光纖接口、10/100/1000M 以太網接口,PCIE 接口,方便各類高速通信系統驗證;預留一個 40pin 的 IO 擴展連接器,方便用戶在開發平臺基礎上驗證模塊電路功能。

2.系統資源

系統資源豐富,可以充分滿足高速數據的緩存處理需求

海量的外圍接口,可以充分滿足多方位開發需求

盤古50K核心板詳情

盤古50K核心板是基于紫光同創 logos 系列 FPGA(PGL50H-6IFBG484)開發的高性能核心板,具有高數據帶寬、高存儲容量的特點,適用于高速數據通信、處理、采集等方面的應用。

核心板使用2 片MICRON公司的MT41K256M16TW-107:P 這款DDR3芯片,每片DDR容量為 4Gbit,2片DDR芯片組合成 32bit 的數據總線寬度,FPGA和 DDR3 之間的讀寫數據帶寬高達 25Gb,可以滿足高帶寬的數據處理需求。

核心板擴展出195個默認電平標準為3.3V 普通IO口,其中有113個IO電壓標準可調,12個1.5V電平標準的普通IO口,還有4對HSST高速RX/TX差分信號和1對HSST高速接口的參考輸入時鐘。

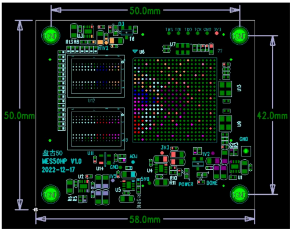

對于需要大量IO的用戶,此核心板是不錯的選擇。FPGA 芯片到接口之間走線做了等長和差分處理。核心板尺寸僅為50*58(mm),非常適合二次開發。

*盤古50K核心板尺寸圖

2.系統資源

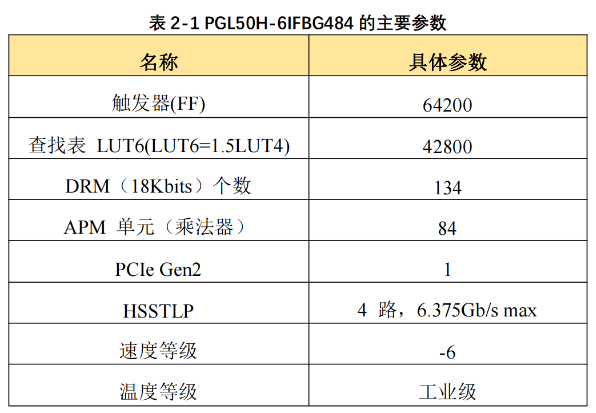

FPGA 型號紫光同創Logos系列PGL50H-6IFBG484速度等級為 6,溫度等級為工業級FBG484 封裝,484個引腳

3.電源參數

盤古50K核心板電壓為 VCCIN,輸入電壓為 5V需通過板對板連接器供電,連接底板時通過底板供電

盤古50K開發板實驗展示

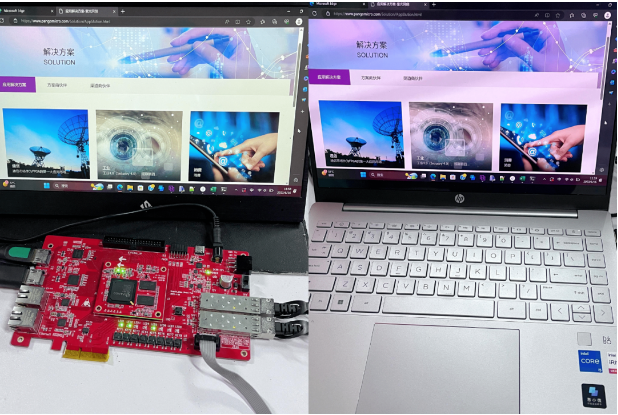

* 攝像頭-HDMI

*視頻光纖環路

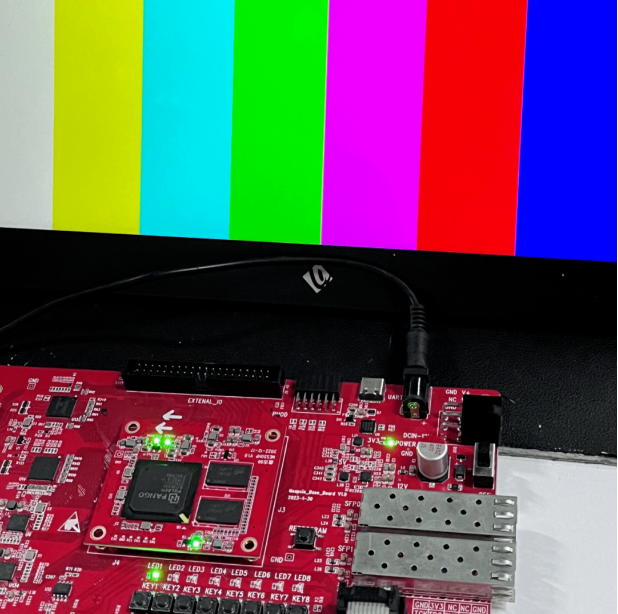

* HDMI輸出

* HDMI視頻環路

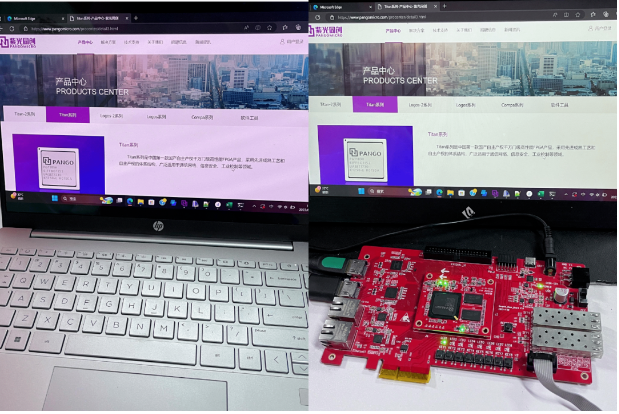

盤古50K開發板產品實拍

審核編輯 黃宇

-

FPGA

+關注

關注

1643文章

21982瀏覽量

614561 -

開發板

+關注

關注

25文章

5563瀏覽量

102688

發布評論請先 登錄

評論