單光子雪崩二極管(SPAD)是各類應用需求量很大的器件,特別是在生物醫學實踐方面。以CMOS技術制備的SPAD憑借其低制造成本、可大規模量產以及與電路的單片集成能力等優勢而備受關注。此外,隨著“摩爾定律”等比例縮微,CMOS-SPAD的優勢在像素分辨率、尺寸及功能等方面愈加突出。因此,諸多研究都在嘗試開發基于先進CMOS技術的SPAD探測器。

據麥姆斯咨詢報道,近日,韓國科學技術研究院(KIST)、瑞士洛桑聯邦理工學院(EPFL)、延世大學(Yonsei University)和格羅方德半導體(GlobalFoundries)新加坡工廠的聯合科研團隊在IEEE Journal of Selected Topics in Quantum Electronics期刊上發表了以“SPAD Developed in 55 nm Bipolar-CMOS-DMOS Technology Achieving Near 90% Peak PDP”為主題的論文。該論文的第一作者為KIST和EPFL的Won-Yong Ha,通訊作者為EPFL的Edoardo Charbon、延世大學的Woo-Young Choi和KIST的Myung-Jae Lee。

這項研究報道了一種利用55 nm雙極型CMOS-DMOS(BCD)技術實現的SPAD。為了在保持擊穿電壓(VB)小于20 V的情況下實現高性能,由p型輕摻雜漏極(PLDD)與高電壓N阱(HVNW)層形成結。此外,SPAD上方的介電層被適當蝕刻,以減少多層反射。該SPAD在光子探測概率(PDP)、暗計數率(DCR)和時間抖動(Timing Jitter)等方面的性能出色,擊穿電壓低至16.1 V。

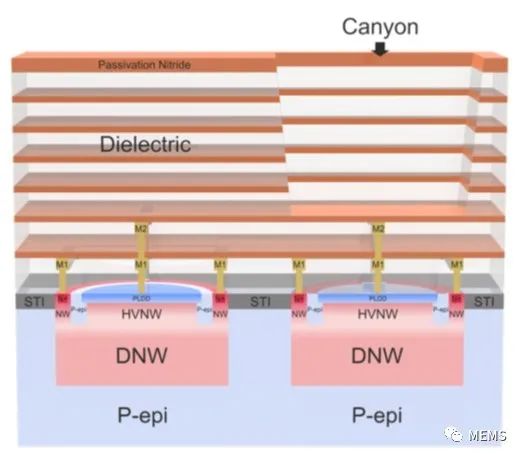

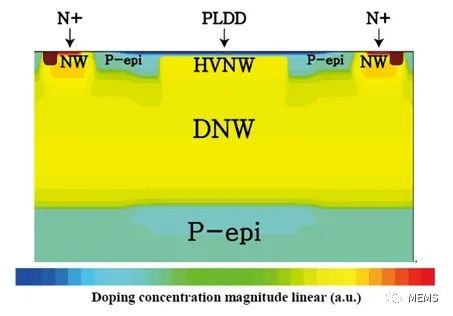

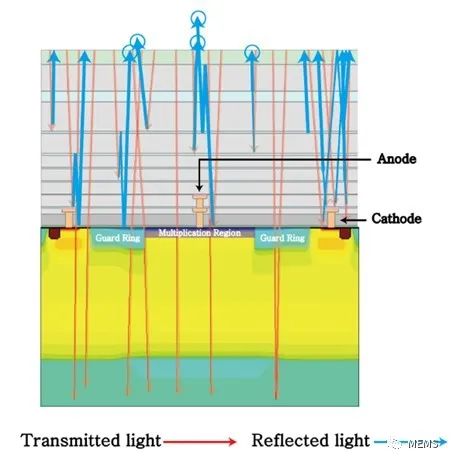

圖1為兩種SPAD結構的截面圖,兩種SPAD具有相同的器件結構,PLDD與HVNW層形成了直徑9 μm的PN結,總直徑達到14.4 μm,如圖2所示。兩層結構均是該技術的標準形式,其優勢主要包括:(i)PLDD產生較少的注入引起的缺陷(implantation-induced defect),從而實現低噪聲SPAD運行;(ii)HVNW利用PLDD層提供了適當的耗盡區,該區域足夠寬,可以防止帶間隧穿,但同時不過分寬,避免擊穿電壓顯著增加。

圖1 BCD-SPAD的橫截面

圖2 BCD-SPAD的摻雜濃度分布圖譜

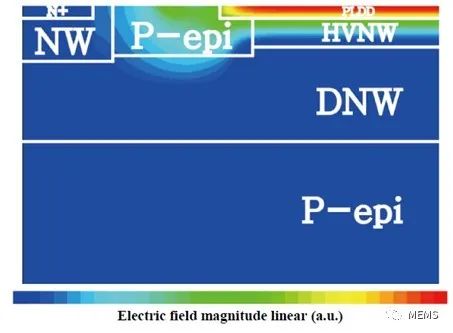

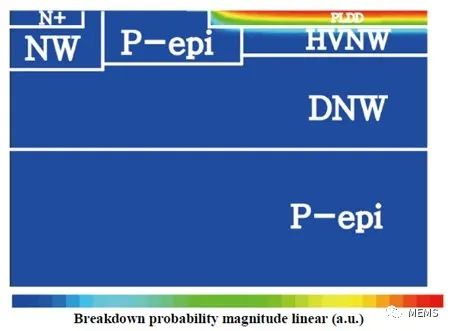

在擊穿電壓(VB)16 V、額外偏置電壓(VE)7 V時,研究人員利用Okuto的雪崩擊穿模型對SPAD進行了TCAD仿真,驗證了SPAD的E場分布,仿真結果如圖3至圖6所示。

圖3 利用TCAD仿真得到BCD-SPAD的電場分布圖譜

圖4 利用TCAD仿真得到BCD-SPAD的擊穿概率分布圖譜

圖5 利用TCAD仿真得到無“峽谷”(canyon)BCD-SPAD的簡化光線追蹤結果

圖6 利用TCAD仿真得到“峽谷”(canyon)BCD-SPAD的簡化光線追蹤結果

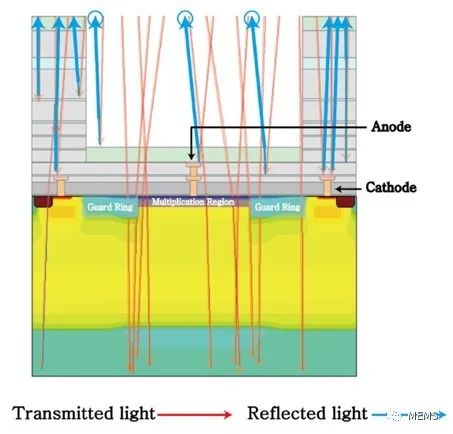

隨后,研究人員對BCD-SPAD的I-V特性、光發射、PDP、DCR以及時間抖動進行了測試,結果如圖7所示。

圖7 BCD-SPAD相關性能測試

綜上所述,這項研究開發并表征了一種利用55 nm BCD技術實現的高性能SPAD。利用BCD技術中的可用層,在低擊穿電壓(VB)下將SPAD結構優化為低噪聲且高效率運行。為了提高其探測效率,研究人員使用“峽谷”(canyon)蝕刻來減少多層反射。當擊穿電壓(VB)為16.1 V,該SPAD在450 nm處峰值PDP為89.4%、DCR為38.2 cps/μm2;當額外偏置電壓(VE)為7 V時,時間抖動為66 ps。研究結果表明,所提出的SPAD在多種生物醫學應用領域具有巨大潛力。

這項研究獲得了韓國科學技術研究院(KIST)合作項目(2E32242)的資助和支持。

審核編輯:劉清

-

探測器

+關注

關注

14文章

2646瀏覽量

73056 -

仿真器

+關注

關注

14文章

1018瀏覽量

83777 -

雪崩二極管

+關注

關注

2文章

54瀏覽量

12848 -

BCD編碼

+關注

關注

0文章

9瀏覽量

6021 -

CMOS技術

+關注

關注

0文章

67瀏覽量

10266

原文標題:利用55 nm BCD技術實現高性能SPAD

文章出處:【微信號:MEMSensor,微信公眾號:MEMS】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

Cortex-A55 處理器到底什么來頭?創龍教儀一文帶您了解

精密脈沖焊接技術的革新:探究高性能精密脈沖焊接電源的應用與實現

臺積電產能爆棚:3nm與5nm工藝供不應求

安森美推出基于BCD工藝技術的Treo平臺

利用微型SPAD系統實現熒光壽命成像+ToF測距

技術巔峰!探秘國內高性能模擬芯片的未來發展

高性能計算集群的能耗優化

基于 GaN 的 MOSFET 如何實現高性能電機逆變器

如何利用55 nm BCD技術實現高性能SPAD呢?

如何利用55 nm BCD技術實現高性能SPAD呢?

評論