小編在本節(jié)完整給出一個(gè)設(shè)計(jì)過程,可利用ISE或Vivado硬件編程軟件實(shí)現(xiàn)。

1 HDL代碼、邏輯電路和器件

- 編寫“HDL代碼”來描述電路功能

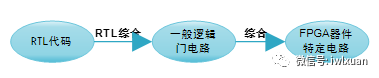

- EDA工具中進(jìn)行“RTL綜合”和“綜合”

“RTL綜合”將HDL代碼轉(zhuǎn)換為邏輯電路

“綜合”這一步將經(jīng)過“RTL綜合”后的門電路映射為FPGA器件的物理結(jié)構(gòu) - “實(shí)現(xiàn)”這一步將對FPGA器件進(jìn)行最終的布局布線

- 綜合實(shí)現(xiàn)的結(jié)果將會(huì)被轉(zhuǎn)換為可以最終運(yùn)行在FPGA器件上的二級制燒錄文件

2 HDL代碼實(shí)例

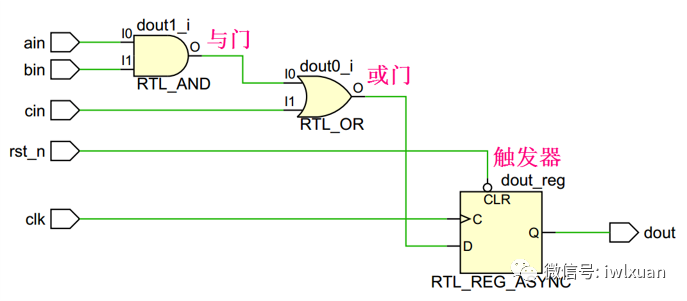

- 在每個(gè)時(shí)鐘clk信號的上升沿,實(shí)現(xiàn)輸出信號dout的值為輸入信號ain、bin和cin的2級門運(yùn)算的結(jié)果

- 這個(gè)門運(yùn)算先是ain和bin“邏輯與”,它們得到的結(jié)果再和cin“邏輯或”

- 輸入復(fù)位信號rst_n為異步復(fù)位信號,任何時(shí)刻這個(gè)信號的下降沿將直接觸發(fā)輸出信號dot取值為0

舉個(gè)栗子

module at7(

clk,rst_n,

ain,bin,cin,dout

);

input clk;

input rst_n;

input ain,bin,cin;

output reg dout;

always @(posedgeclk or negedgerst_n)

if(!rst_n)

dout <= 1'b0;

else

dout <= (ain & bin) | cin;

endmodule

3 RTL綜合

- “RTL綜合”后的邏輯電路原理圖,它很好的以門電路的形式表達(dá)了我們的實(shí)例代碼

- “RTL綜合”門電路和HDL代碼所描述的功能完全一致,大家對比下圖和第2節(jié)的代碼。下圖即是代碼RTL綜合后的布局。

圖1 RTL綜合后的邏輯電路原理圖

4 綜合

- “RTL綜合”是指將HDL代碼轉(zhuǎn)換為邏輯門電路形式來表達(dá)的一個(gè)過程;“綜合”卻是將已經(jīng)用邏輯門關(guān)系表達(dá)的電路進(jìn)一步轉(zhuǎn)換為FPGA器件實(shí)際物理結(jié)構(gòu)相對應(yīng)的電路形式 “綜合”電路中看不到任何的“門”

- “綜合”的結(jié)果是所使用的特定FPGA器件中實(shí)際存在著的物理結(jié)構(gòu),如“輸入緩沖”、“查找表”、“觸發(fā)器”和“輸出緩沖”等

圖2 RTL綜合與綜合的關(guān)系

圖3 綜合后的邏輯電路原理圖

5 實(shí)現(xiàn)

- 在“綜合”給出HDL代碼與實(shí)際FPGA器件的映射關(guān)系后,做具體執(zhí)行的工作

- 如果把“綜合”結(jié)果比喻為電路板設(shè)計(jì)的“原理圖”階段,那么“實(shí)現(xiàn)”這個(gè)步驟就是具體的“布局布線(layot)”階段

圖4 布線圖

6 生成燒錄文件

- 如同電路板的layout完成后要生成gerber,F(xiàn)PGA工具最終也要產(chǎn)生一個(gè)bit文件用于燒錄到FPGA中運(yùn)行了

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報(bào)投訴

-

FPGA

+關(guān)注

關(guān)注

1630文章

21783瀏覽量

605023 -

邏輯電路

+關(guān)注

關(guān)注

13文章

494瀏覽量

42672 -

HDL

+關(guān)注

關(guān)注

8文章

328瀏覽量

47430 -

代碼

+關(guān)注

關(guān)注

30文章

4816瀏覽量

68873 -

Vivado

+關(guān)注

關(guān)注

19文章

815瀏覽量

66769

發(fā)布評論請先 登錄

相關(guān)推薦

如何在FPGA上實(shí)現(xiàn)HDL代碼完成MATLAB轉(zhuǎn)換

如果您正在使用 MATLAB 建模數(shù)字信號處理(DSP)或者視頻和圖像處理算法,并且最終將其用于 FPGA 或 ASIC,本文可能將為你帶來幫助。 從 MATLAB 生成 HDL 代碼 FPG

如何使用Verilog HDL進(jìn)行FPGA設(shè)計(jì)

FPGA設(shè)計(jì)流程是利用EDA開發(fā)軟件和編程工具對FPGA芯片進(jìn)行開發(fā)的過程。FPGA的設(shè)計(jì)流程如上圖所示:包括設(shè)計(jì)定義、代碼

發(fā)表于 04-04 10:29

?2419次閱讀

FPGA設(shè)計(jì)中 Verilog HDL實(shí)現(xiàn)基本的圖像濾波處理仿真

今天給大俠帶來FPGA設(shè)計(jì)中用Verilog HDL實(shí)現(xiàn)基本的圖像濾波處理仿真,話不多說,上貨。

1、用matlab代碼,準(zhǔn)備好把圖片轉(zhuǎn)化成Vivado Simulator識別的

發(fā)表于 05-20 16:44

DCT實(shí)現(xiàn)Verilog HDL的數(shù)字圖像處理源代碼

DCT實(shí)現(xiàn)Verilog HDL的數(shù)字圖像處理源代碼

發(fā)表于 08-11 09:30

基于模型設(shè)計(jì)的HDL代碼自動(dòng)生成技術(shù)綜述

、基于模型設(shè)計(jì)的HDL代碼自動(dòng)生成技術(shù)應(yīng)用需求近年來,現(xiàn)場可編程門陣列(FPGA)被廣泛應(yīng)用于航空航天、汽車、通信、工業(yè)自動(dòng)化、電機(jī)控制、醫(yī)學(xué)成像等嵌入式應(yīng)用領(lǐng)域。傳統(tǒng)的FPGA上的數(shù)

發(fā)表于 06-08 09:29

FPGA雙沿發(fā)送之Verilog HDL實(shí)現(xiàn) 精選資料推薦

1.1 FPGA雙沿發(fā)送之Verilog HDL實(shí)現(xiàn)1.1.1 本節(jié)目錄1)本節(jié)目錄;2)本節(jié)引言;3)FPGA簡介;4)FPGA雙沿發(fā)送之

發(fā)表于 07-26 06:20

FPGA雙沿采樣之Verilog HDL實(shí)現(xiàn) 精選資料分享

1.1 FPGA雙沿采樣之Verilog HDL實(shí)現(xiàn)1.1.1 本節(jié)目錄1)本節(jié)目錄;2)本節(jié)引言;3)FPGA簡介;4)FPGA雙沿采樣之

發(fā)表于 07-26 07:44

基于Verilog HDL語言的FPGA設(shè)計(jì)

采用 Verilog HDL 語言在Altera 公司的FPGA 芯片上實(shí)現(xiàn)了RISC_CPU 的關(guān)鍵部件狀態(tài)控制器的設(shè)計(jì),以及在與其它各種數(shù)字邏輯設(shè)計(jì)方法的比較下,顯示出使用Verilog

發(fā)表于 08-21 10:50

?69次下載

Verilog HDL與VHDL及FPGA的比較分析

Verilog HDL與VHDL及FPGA的比較分析. Verilog HDL優(yōu)點(diǎn):類似C語言,上手容易,靈活。大小寫敏感。在寫激勵(lì)和建模方面有優(yōu)勢。

發(fā)表于 01-11 10:45

?1387次閱讀

MathWorks推出基于MATLAB生成HDL代碼的產(chǎn)品

MathWorks 近日宣布推出 HDL Coder,該產(chǎn)品 支持MATLAB 自動(dòng)生成 HDL 代碼,允許工程師利用廣泛應(yīng)用的 MATLAB 語言實(shí)現(xiàn)

發(fā)表于 03-07 09:27

?2171次閱讀

基本組合邏輯功能雙向管腳的Verilog HDL源代碼

電子發(fā)燒友網(wǎng)核心提示: 本例程是Verilog HDL源代碼:關(guān)于基本組合邏輯功能中雙向管腳的功能實(shí)現(xiàn)源代碼。 Verilog HDL: B

發(fā)表于 10-15 11:28

?1625次閱讀

MathWorks網(wǎng)絡(luò)研討會(huì):高性能FFT的HDL實(shí)現(xiàn)與驗(yàn)證

?Virtex-7 FPGA? 上運(yùn)行進(jìn)行了優(yōu)化)。演示的工作流程從參考 ?MATLAB? 代碼開始,強(qiáng)調(diào)了模型開發(fā)、定點(diǎn)轉(zhuǎn)換、優(yōu)化 ?HDL? 代碼生成以及 ?

發(fā)表于 02-09 02:26

?403次閱讀

System Generator實(shí)現(xiàn)串口通信(一行HDL代碼都不用寫)

一直都在System Generator下做圖像處理相關(guān)的算法,感覺SysGen挺強(qiáng)大的,前幾天突發(fā)奇想,能否直接用SysGen實(shí)現(xiàn)數(shù)據(jù)的通信呢,畢竟一句HDL代碼都不寫對于做FPGA

發(fā)表于 02-10 19:51

?2953次閱讀

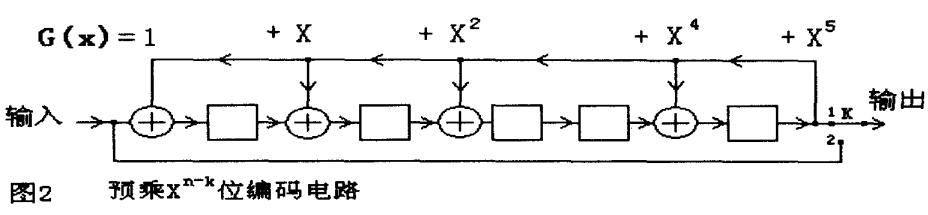

并行CRC電路HDL代碼的快速生成

CRC校驗(yàn)的實(shí)現(xiàn)基于串行位移寄存器,如果要處理并行數(shù)據(jù),需要對電路進(jìn)行改進(jìn)。本文介紹了一種并行CRC電路HDL代碼的快速生成鐘算法,只需要帶入不同的參數(shù),可自動(dòng)生成不同長度以及并行度的并行CRC電路的

發(fā)表于 03-28 09:29

?16次下載

FPGA HDL代碼實(shí)現(xiàn)過程

FPGA HDL代碼實(shí)現(xiàn)過程

評論