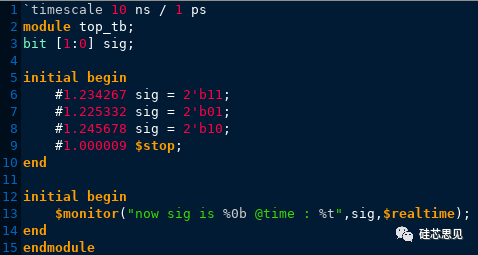

在SystemVerilog中,輸出信息顯示時間時,經常會在輸出信息格式中指定“%t”格式符,一般情況下“%t”輸出的格式都是固定的,但是這樣固定的輸出顯示的時間可能有時會讓用戶看起來感覺比較詫異,例如下面的示例。

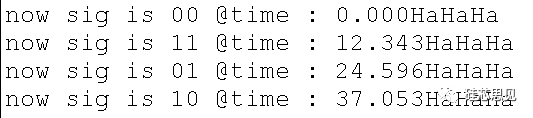

【示例】

【仿真結果】

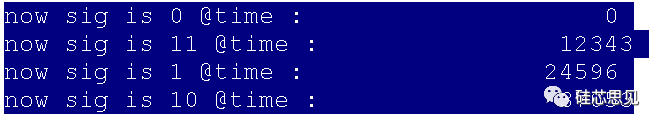

示例中,設置的timescale是“10ns/1ps”,在$monitor中將$realtime返回的時間通過格式符“%t”輸出,但是此時顯示的時間數值很大,并且沒有單位,這可能會讓用戶不知所措,例如在sig為“11”時,此時顯示的時間為12343,但是這個數字的單位是什么,$relatime本身返回的值并不是這里的12343,示例中顯示的結果為什么與$realtime返回值不同呢,這是為什么呢?其實這主要是因為“%t”的輸出格式受了任務$timeformat(注意是任務不是函數與!)的影響,雖然這里沒有顯式的調用$timeformat,但是其默認值還是會影響到“%t”顯示的時間值,即“%t”默認顯示的時間是按照當前module的timescale設置的精度作為單位的,并且默認情況下顯式的時間后是沒有時間單位字符串的,所以此時就可以理解為什么“%t”在sig為“11”時顯示的時間是12343了,這是因為這個此時顯示的數字的單位是1ps。其實在SystemVerilog中,通過$timeformat可以約束“%t”顯示的時間格式,其中具體參數對應關系如下圖。

其中units_number 是 0 到-15 之間的整數值,表示打印的時間值如下表:

| Unit Number | Time Unit | Unit Number | Time Unit |

| 0 | 1 s | -8 | 10 ns |

| -1 | 100 ms | -9 | 1 ns |

| -2 | 10 ms | -10 | 100 ps |

| -3 | 1 ms | -11 | 10 ps |

| -4 | 100 us | -12 | 1 ps |

| -5 | 10 us | -13 | 100 fs |

| -6 | 1 us | -14 | 10 fs |

| -7 | 100 ns | -15 | 1 fs |

precision_number 是在打印時間值時,小數點后保留的位數,其默認值為0。

suffix_string 是在時間值后面打印的后綴字符串,其默認值為空字符串。

MinFieldWidth 是時間值字符串與后綴字符串合起來的這部分字符串的最小長度,若這部分字符串不足這個長度,則在這部分字符串左側補空格,直到總長度達到設置的值,如果總字符串比設置的值大,將按照字符串實際長度輸出,其默認值為20。

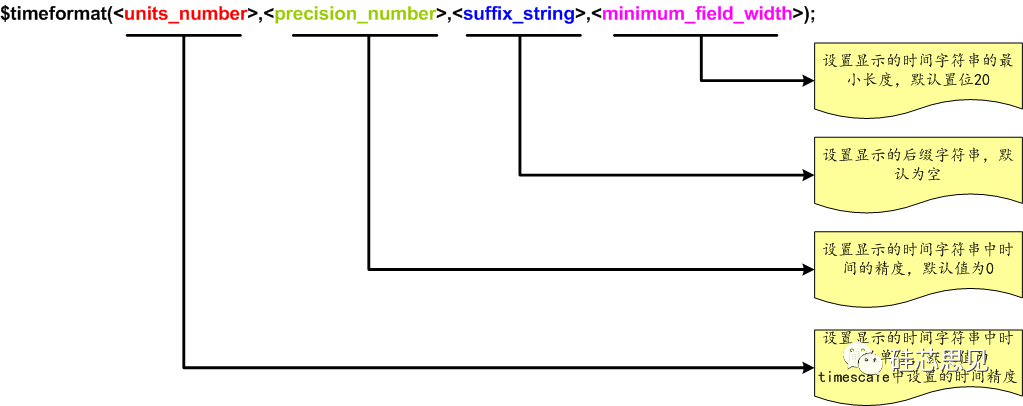

下面我們通過一個示例進一步理解下$timeformat是如何使用的。

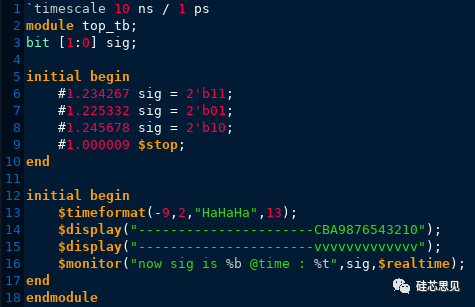

【示例】

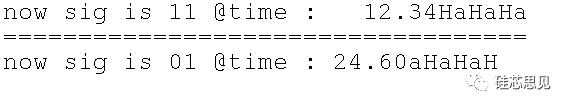

【仿真結果】

示例中,通過$timeformat指定了“%t”輸出時間的格式,“-9”表示要顯示的時間是按照“1ns”為單位得到的,“3”表示顯示的時間中小數部分的位數,“HaHaHa”為時間字符串之后的后綴字符串,這個字符串一般指定為時間的單位,最后一個參數“2”表示“%t”顯示的整個字符串長度的最小值,因為此時的時間字符串和后綴字符串的長度大于設置的最小值,所以此時按照實際字符串長度顯示,當然也可以把這個字符串最小長度的值設置的大于實際字符串長度,如下例。

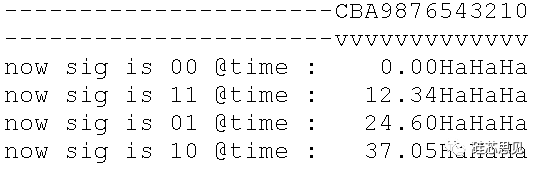

【示例】

【仿真結果】

示例中,通過$timeformat設置了顯示時間字符串的最小長度為13,仿真結果可以看出,實際字符串的長度沒有13個字符串那么長,所以此時字符串按照左對齊,并在字符串左側補空格直到字符船總長度達到$timeformat設置的字符串的最小長度要求為止。另一方面,$timeformat設置了顯示時間保留小數點后的位數為2,所以時間顯示的最終結果保留了2位小數,同時需要注意,此處進行兩位小數保留時會進行四舍五入操作。

通過上述幾個示例,如果我們期望“%t”顯示的時間值與當前仿真時間一致,那么需要給$timeformat設置對應合適的參數或者在輸出時間時在格式字符串中不要指定“%t”,而是直接將其位置空留出來,這樣輸出的數據將完全取決于用戶使用的時間函數

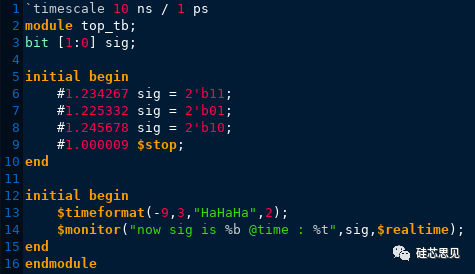

最后,在一個模塊中可以設置多個$timeformat,一個$timeformat生效后會持續到下一個$timeformat,如下例。

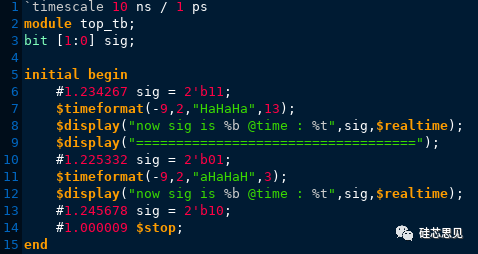

【示例】

【仿真結果】

示例中,通過仿真結果可以看到第7行設置的$timeformat僅影響到了第8行“%t”的顯示,并沒有影響到第12行“%t”的顯示,第7行設置的$timeformat在遇到第11行設置的$timeformat之后就退出了歷史舞臺,所以第12行“%t”顯示的格式按照第11行設置的$timeformat顯示了。

審核編輯:劉清

-

仿真器

+關注

關注

14文章

1019瀏覽量

83815 -

字符串

+關注

關注

1文章

584瀏覽量

20553 -

Verilog語言

+關注

關注

0文章

113瀏覽量

8281

原文標題:SystemVerilog中的$timeformat是干啥的

文章出處:【微信號:處芯積律,微信公眾號:處芯積律】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

SystemVerilog中的$timeformat是做什么的?

SystemVerilog中的$timeformat是做什么的?

評論