近年來,隨著摩爾定律的放緩,多芯片系統(Multi-die)解決方案嶄露頭角,為芯片功能擴展提供了一條制造良率較高的路徑。

多芯片系統是將多個專用功能芯片(或小芯片)封裝為完整的一體。為了實現更高的布線密度和帶寬流量,封裝技術已發展到基于硅中介層(帶有TSV)或硅橋以及最近的重新分配層(RDL)來創建新的高級封裝扇出和高清基板。

多芯片系統還能使產品SKU在性能擴展方面更加靈活,以滿足不同的市場需求,通過在同一產品中混合和匹配各種工藝節點來優化每個功能的工藝節點,加快了上市時間并降低了風險。

但是多芯片系統的設計是一項充滿挑戰的任務,它需要芯片工程師具備多個領域的專業知識和實踐經驗。

多芯片系統成功的關鍵:保證可測試性

多芯片系統成功的關鍵之一是在各種制造和組裝階段保證系統的可測試性,同時確保在實際應用中可靠運行。因為需要采取額外的組裝步驟和更復雜的焊球以及封裝技術,多芯片系統所需的測試和可靠性程序超越了傳統單一的設計。

因此,我們需要先對裸片進行測試,以確保在封裝之前就發現所有有缺陷的芯片。如果在組裝后才檢測到有缺陷的芯片,那整個多芯片系統就要被廢棄,這將嚴重影響成本。

這個測試裸片的過程被稱為“已知良好芯片”(KGD)測試。

實際的組裝過程會因所選擇的封裝技術而有所不同。

例如,“芯片優先(chip-first)”技術是先放置芯片然后在其上構建互連,這種方式無法進行“已知良好封裝”的測試,如果互連出現故障,可能會導致好的芯片被廢棄。

反過來,還有一種“芯片后置(chip-last)”技術,先單獨構建互連,然后將芯片裝配在其頂部,這可以在組裝之前進行封裝預測試,從而降低良好芯片被廢棄的可能性。

多芯片系統可測試性解決方案可以分為幾個方面:

芯片內單個模塊的測試覆蓋率

單個芯片(裸芯片)的測試覆蓋率

封裝系統的測試(芯片到芯片覆蓋率)

訪問裸片中的測試網絡

組裝后對測試網絡的分層訪問

使用UCIe IP確保多芯片系統的可靠性

UCIe作為新的接口標準,讓多芯片系統間的通信更加流暢,使得各個組件之間能夠更有效地交換信息。

作為全球領先的EDA廠商,新思科技提供全面且可擴展的多芯片系統解決方案,包括 EDA 和 IP,用于快速異構集成。為了實現安全可靠的芯片間連接,新思科技提供了完整的 UCIe 控制器、PHY 和驗證 IP 解決方案。

作為 SLM 和測試系列的一部分,新思科技可同時提供完整的UCIe監控、測試和修復 (MTR) 解決方案與STAR分層系統 (SHS) 解決方案。

其中,MTR 解決方案包括用于測量 UCIe 通道信號質量的信號完整性監視器、用于自檢的 BIST 以及用于冗余通道分配的修復邏輯;而SHS解決方案則充當支持行業標準 IEEE 1687、IEEE 1149.1、IEEE 1838 接口的連接結構。這一完整的解決方案能夠在芯片生命周期的所有階段對 UCIe 進行高效且經濟高效的健康監控。

UCIe IP的使用為確保多芯片系統可靠性提供了一種綜合的可測試性解決方案。接下來,我們就來探討一下這種方案的優勢。

UCIe接口的DFT

UCIe接口的設計可測試性(DFT)是在裸芯片測試階段,通過在UCIe IP中實施廣泛的可測試性功能,達到識別并剔除有缺陷的芯片。

這些全面且強大的測試性功能極大地提高了UCIe接口的測試覆蓋率,具體包括:全面覆蓋所有合成數字電路的掃描鏈、專門用于模塊特定的內置自測試(BIST)功能、環回內置自測試 (BIST) 功能,涵蓋直至 IO 引腳的完整信號鏈,以及可編程偽隨機二進制序列(PRBS)和用戶定義的測試模式生成器和檢查器。這還包括錯誤注入功能,它可以精確地模擬并消除錯誤,提高系統的魯棒性。

除了以上的單芯片測試,UCIe接口的設計還覆蓋了組裝后的系統內測試,包括:遠端(芯片到芯片)BIST環回功能,用于測量、分析和修復通道的芯片到芯片鏈接BIST、二維眼圖邊緣分析以及各個通道測試和修復功能。

通過這種方式,UCIe接口的設計可測試性(DFT)解決方案,無論是在單芯片還是在多芯片系統層面,都能夠提供高水平的測試覆蓋范圍,從而確保其可靠性。

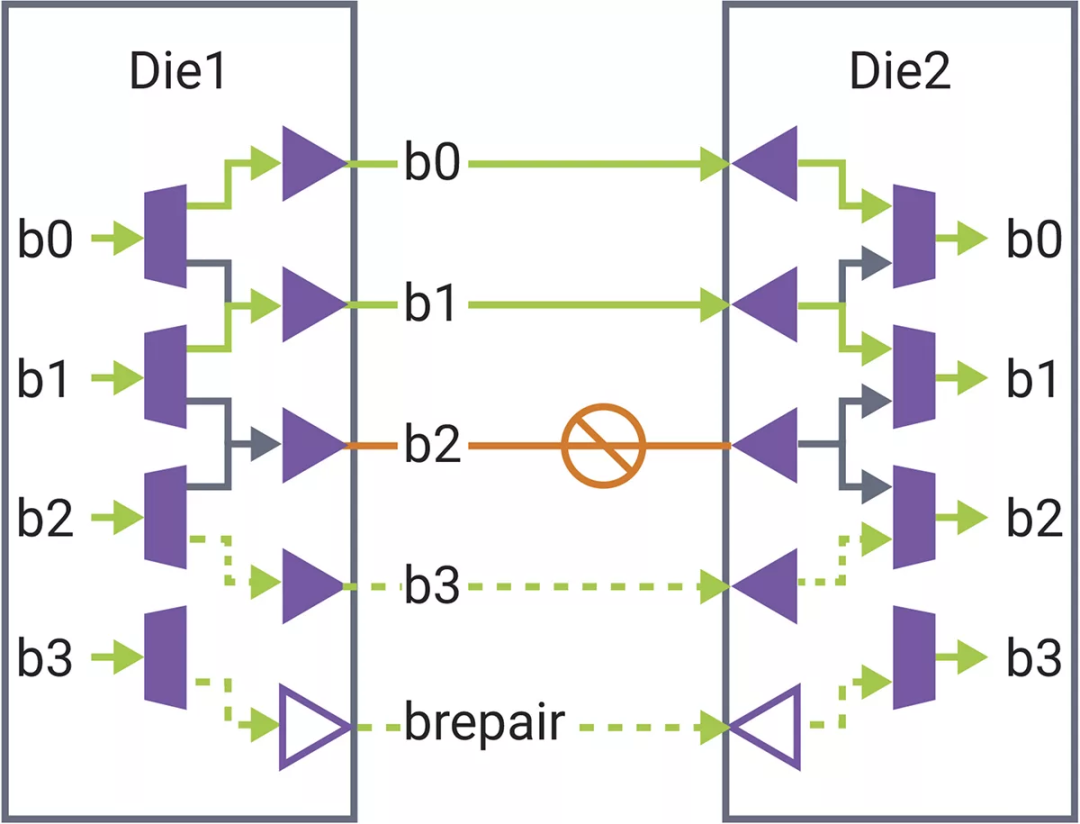

解決高級封裝挑戰:UCIe測試和修復的應用

先進封裝可通過在硅或 RDL 中介層上進行細間距、微凸焊點以實現高密度布線。然而,在組裝過程中,一些微凸焊點連接可能無法很好地形成,甚至可能會損壞。不過,不必擔心,UCIe可以在組裝完成后對這些連接進行測試和修復,以挽回潛在的良率損失。

這些UCIe的測試和修復工作主要是在生產測試和鏈路初始化階段進行的。具體來說,在測試階段,它們會以較低的速度對每一個獨立的鏈路進行缺陷檢查,一旦發現有缺陷的鏈路,就通過將數據重新路由到UCIe標準預定義的備用鏈路來進行修復。

為了滿足高級封裝技術的需求,UCIe每個方向最多可配置8個備用引腳(發送和接收),這為所有功能鏈路的修復提供了可能:

4個備用引腳,用于數據引腳修復,每組32個數據引腳中有2個備用引腳

1個備用引腳,用于時鐘和跟蹤引腳修復

3個備用引腳,分別用于有效引腳、邊帶數據引腳和時鐘數據引腳修復

當芯片間鏈路上沒有數據傳輸時,UCIe就會進行這些測試和修復工作。修復完成并初始化鏈路后,假設鏈路狀態良好,數據可以順利通過。而生成的物理層(PHY)配置(也被稱為PHY修復簽名)則會存儲在鏈路兩端的內部寄存器中。

然而,我們需要注意的是,如果我們在協議級別發現誤碼率 (BER)增加,甚至出現了數據丟失,就說明微凸焊點的特性發生了老化或退化。在這種情況下,預計鏈路將中斷并執行新的測試和修復步驟。

有些應用對芯片間鏈路上的流量連續性有嚴格的要求,針對這些情況,可測試性解決方案在每個UCIe接收器引腳中加入了信號完整性監視器(SIM)。

圖1:使用內置備用鏈接進行鏈接修復

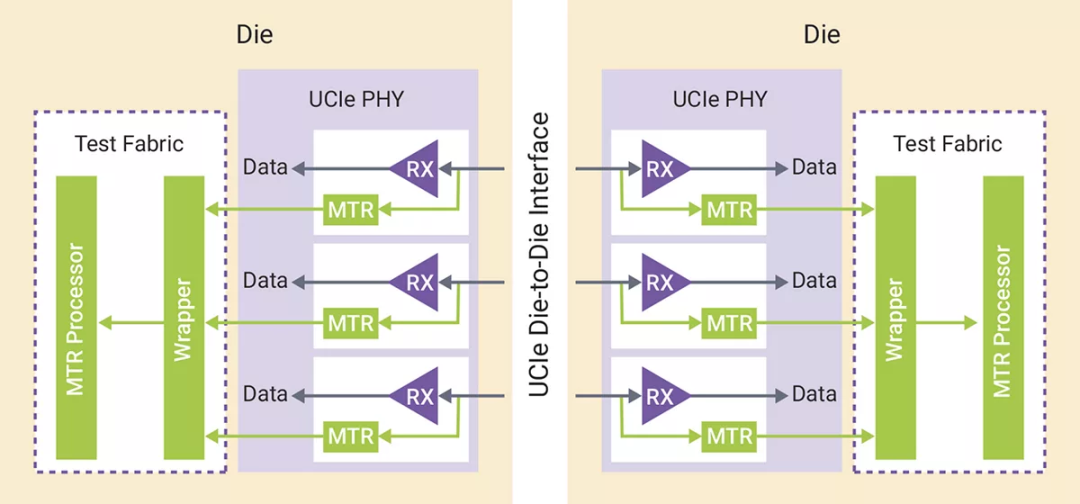

信號完整性監視器與UCIe PHY修復機制的協同作用

信號完整性監視器(簡稱SIM),是一種嵌入在接收器內部的微小模塊。在設備的正常運行過程中,它會不斷檢測接收器引腳接收到的信號,以便發現信號特性的任何變化。這些變化可能會對鏈接的性能產生影響,或者表示鏈接有潛在風險,可能在不久的將來會出現問題。

每個傳感器收集到的數據會被送到接口之外的一個監控、測試和維修(MTR)控制器中進行更深入的分析和處理。當把來自多個UCIe鏈接的數據整合起來時,我們能夠立刻洞察到多芯片系統的運行狀態,并且能夠實施預測性的鏈接維護。

如果通過這一過程預見到某個特定鏈接可能會出現故障,則可以利用UCIe PHY的修復機制將其關閉,并將數據重新指向一個備用鏈接,整個過程甚至都不會中斷數據的傳輸。

圖2:UCIe鏈路的健康監控解決方案

利用UCIe PHY加快喚醒時間

雖然在大多數芯片間接口的案例中(例如在服務器分割或擴展中),數據流量模式在運行期間是穩定的,但在特定情況下,也可能會出現異常。在這種情況下,最好在沒有流量時將接口置于低功耗模式以節省電量。通過避免測試和修復過程并依賴在先前 PHY 初始化期間創建的 UCIe PHY 修復簽名,可以加速鏈路重新初始化。

這個概念可以進一步擴展到芯片完全斷電的情況。在這些情況下,從 PHY 檢索 PHY 修復簽名并將其存儲在片上永久存儲器(閃存的 eFuse)上。存儲器可以存儲多個簽名,涵蓋不同的用例或條件,從而實現額外的用戶靈活性。

使用UCIe加速芯片測試

測試時間是非常寶貴的,通過分層劃分測試策略,同時進行不同芯片的測試,可以加快測試時間。通過分層連接兩個芯片的測試基礎設施,可以將層次結構擴展到多芯片系統中的多個芯片。這種方法允許從主芯片中的單個JTAG(或類似)測試接口訪問多芯片系統中的所有芯片。

通常,將測試向量加載或讀取到芯片中所需時間會成為縮短整體的測試時間的瓶頸。為了克服這一限制,設計人員可以使用現有的高速接口,例如PCI Express (PCIe)或USB等作為測試設備的接口。測試向量和命令針對該接口進行打包,并在生產測試階段在芯片上進行解包。

許多芯片沒有高速接口,但是,在測試期間,可以使用 UCIe 芯片間接口在芯片之間高速傳輸大型測試向量和命令。UCIe芯片間接口將高速 DFT 訪問擴展到整個多芯片系統,而無需增加引腳數量,這對于 IO 和面積有限的芯片尤其重要。

總結

綜上,除了UCIe芯片間接口之外,實現所有這些測試和可靠性增強功能的共同點是可以連接所有內部模塊的測試、修復和監控結構。新思科技提供的UCIe控制器、PHY和驗證IP解決方案,就像一只錨,確保了整個多芯片系統設計過程和最終產品的可靠性和穩定性。它不僅為設計師們提供了一套強大的工具,更打開了一個全新的設計世界,使得他們能夠更好地發揮他們的創新性和創造性。

審核編輯:劉清

-

控制器

+關注

關注

112文章

16332瀏覽量

177812 -

接收機

+關注

關注

8文章

1180瀏覽量

53455 -

PHY

+關注

關注

2文章

301瀏覽量

51732 -

DFT算法

+關注

關注

0文章

27瀏覽量

7535 -

UCIe

+關注

關注

0文章

45瀏覽量

1632

原文標題:UCIe IP :多芯片系統可靠性的新路徑

文章出處:【微信號:wc_ysj,微信公眾號:旺材芯片】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

康謀方案 | 多源相機數據采集與算法集成測試方案

多芯片系統成功的關鍵:保證可測試性

多芯片系統成功的關鍵:保證可測試性

評論