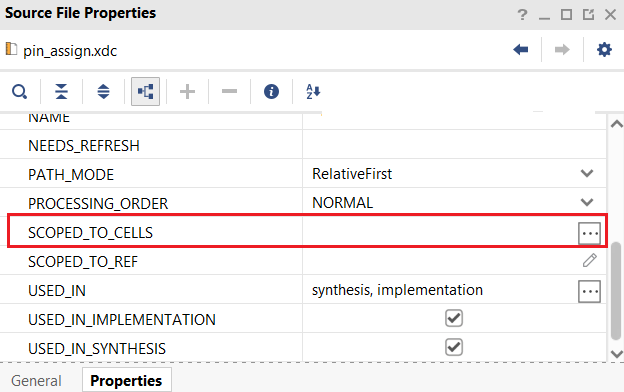

在常規非DFX(DynamicFunction eXchange)的Vivado設計中,我們可能會碰到給某一個指定的模塊添加特定的約束。這時一個簡單的方法就是將這些約束單獨寫在一個.xdc或.tcl文件中,然后將其添加到Vivado工程中,并將該約束文件的屬性SCOPE_TO_CELLS設定為目標模塊。如果該模塊在設計中被多次實例化,不管這些實例化模塊在設計中的層次如何,此時可設置該約束文件的屬性SCOPE_TO_REF,如下圖所示。這里我們就能理解對于一個cell其屬性NAME和REF_NAME的區別:前者是實例化后的名字,后者為引用名(可以理解為Verilog的module name或VHDL的entityname)。另外,需要特別注意的是使用上述方法時,在.xdc或.tcl文件中的約束其施加的對象是以該指定模塊作為頂層的而不是以實際工程的頂層作為頂層。如果采用Non-Project模式,那么可以通過read_xdc讀入約束文件,然后通過set_property命令指定約束文件的屬性SCOPE_TO_CELLS或者SCOPE_TO_REF。

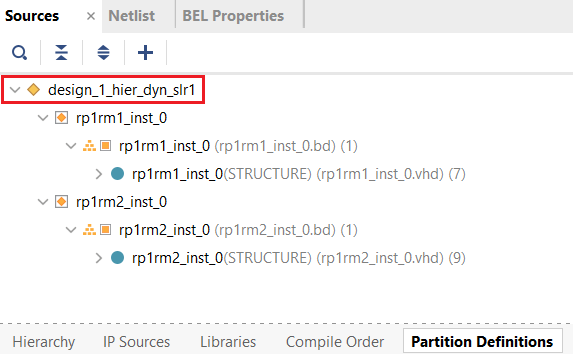

在DFX設計中,我們也會碰到類似的情形,即給同一個RP(Reconfigurable Partition)下的不同RM(Reconfigurable Module)添加不同的約束。這時要考慮幾個因素:同一個RP下不管有幾個RM,在設計中均對應同一個實例化的名字。這意味著不能僅僅通過SCOPE_TO_CELLS將這些約束對應到不同的RM上。另外,每個RM只有在自身對應的configuration上才有效,所以要保證在這個configuration上對應的RM的約束也要有效。從下圖可以看到,當前這個DFX設計中有一個RP,名字為圖中紅色方框所示,該RP下有兩個RM,分別為rp1rm1和rp1rm2。

基于上圖所示DFX設計,現在我們要分別對rp1rm1和rp1rm2添加不同的約束。這里我們先介紹一下DFX設計的約束管理模式。在DFX設計中,約束是按configuration分組的。這是因為不同的configuration對應不同的RM。但不管有幾個configuration,都會有主約束,也就是ParentRun對應的約束,默認在constrs_1下。主約束包括:頂層IO約束(管腳分配/電平設置/input delay/output delay)、全局時鐘周期約束和每個RP的Pblock信息。主約束在運行Parent Run時生效,并在運行結束之后鎖定靜態區時一同被鎖定,因此,后續的ChildRun會直接獲得這些約束信息不需要重寫一遍。默認情況下,Child Run并沒有單獨的ConstraintSet,也就沒有單獨的約束文件。如果要針對RM施加約束,而RM又出現在Child Run,就要建立新的Constraint Set,這需要如下幾個步驟完成。

第一步:創建與指定RM相關的約束,這些約束應放在單獨的.xdc文件中。

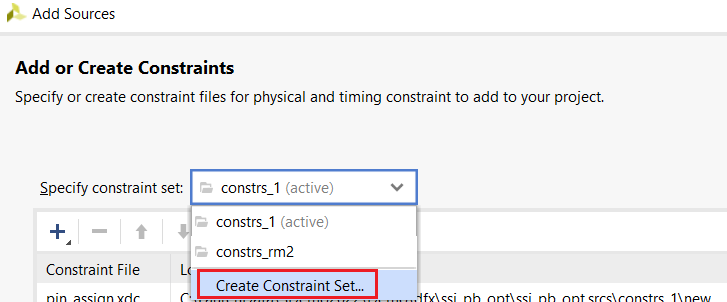

第二步:創建新的Constraint Set,并將第一步創建的約束文件添加到該Constraint Set下。

除了Parent Run之外,有幾個ChildRun,如果這些Child Run里的RM又需要單獨約束,那么就要創建幾個Constraint Set。創建ConstraintSet的方法如下圖所示。

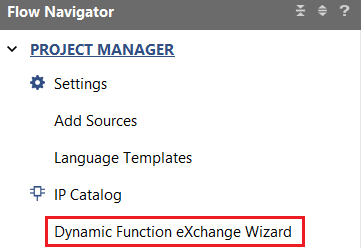

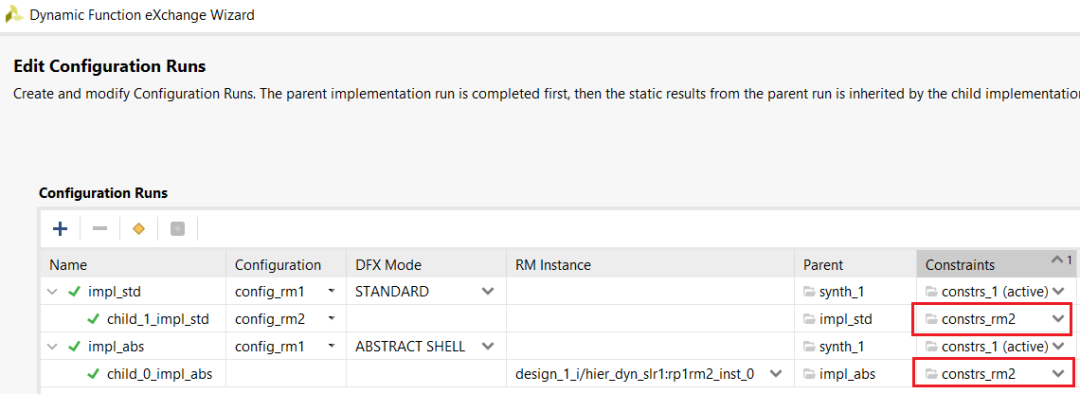

第三步:運行DFX Wizard到EditConfiguration Runs界面,如下圖所示。在對應的Constraints列選擇相應的Constraint Set,如圖中紅色方框所示。

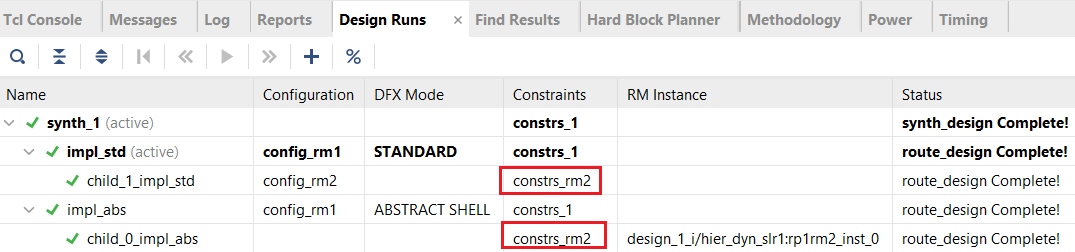

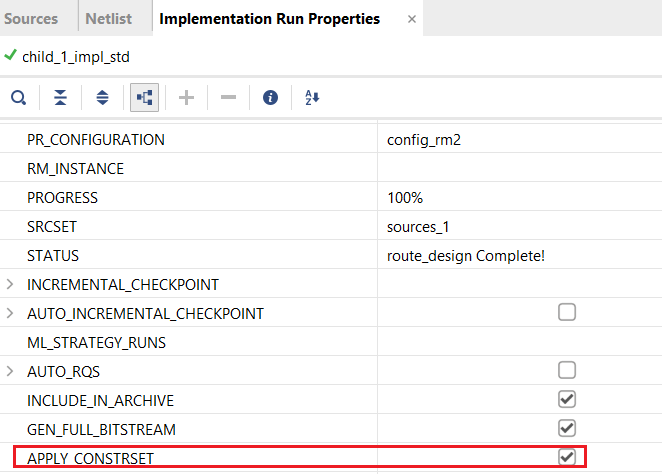

在Design Run窗口中就能看到相應的ChildRun對應的Constraint Set,如下圖中的紅色方框所示。如果沒生效,要確保ChildRun的Property APPLY_CONSTRSET被勾選。

上述過程針對的是Vivado Project模式。在Non-Project模式下,當運行rp1rm2對應的Configuration時,要先打開鎖定靜態區布線信息的dcp(在這個dcp中,RP均為黑盒子),然后加載對rp1rm2OOC綜合生成的dcp,這個過程結束之后即可通過read_xdc讀入針對rp1rm2的約束文件。

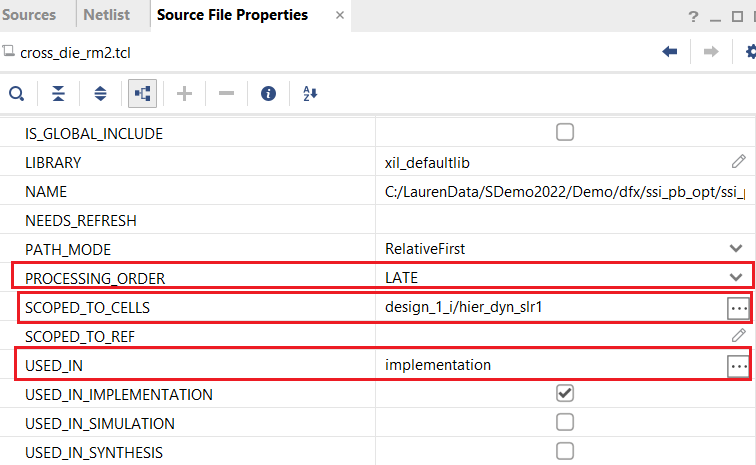

針對RM的約束文件,通常要設定以下幾個屬性:PROCESSING_ORDER,SCOPED_TO_CELLS和USED_IN,如圖中紅色方框所示。

-

文件

+關注

關注

1文章

581瀏覽量

25378 -

命令

+關注

關注

5文章

738瀏覽量

22898 -

約束

+關注

關注

0文章

82瀏覽量

12974 -

Vivado

+關注

關注

19文章

835瀏覽量

68829

發布評論請先 登錄

FPGA主時鐘約束詳解 Vivado添加時序約束方法

怎么才能刪除自動添加的時序約束?

FPGA上設計系統應該添加任何約束嗎?

怎樣給FPGA邏輯電路添加約束標簽呢

FPGA開發之時序約束(周期約束)

混合搜索的含邏輯“與”“或”的RM優化算法

評論