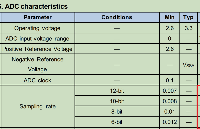

隨著高速模數轉換器 (ADC) 采樣率的提高,ADC 輸出數據中的代碼錯誤(也稱為閃爍代碼)問題也隨之增加。代碼錯誤定義為 ADC 輸出代碼中的錯誤超過定義的閾值。閾值通常定義為誤差超過 ADC 噪聲預期幅度的水平,以便在存在噪聲的情況下可以輕松識別該誤差。

解釋誤差閾值定義的另一種方法是,在給定 ADC 假定的高斯分布噪聲的情況下,誤差幅度發生的概率超過該幅度的預期概率。圖 1 顯示了在 ADC 輸出樣本中發現的示例代碼錯誤。與理想的正弦波擬合相比,錯誤樣本清晰可見,并且遠遠超過圖中其他樣本的噪聲。

圖 1:存在代碼錯誤的 ADC 輸出示例。

ADC 的誤碼率 (CER),有時也稱為字錯誤率 (WER) 或亞穩態錯誤率,定義為每個樣本的平均錯誤數,并通過計算連續錯誤之間的平均樣本數來測量。它通常被定義為一個數量級,例如 10 –12 個 錯誤/樣本。因此,錯誤之間的平均時間取決于轉換器的采樣率。僅當 ADC 以測量 CER 的采樣率運行時,測量的 CER 才是準確的。一般來說,降低采樣率可以將 CER 提高幾個數量級。

讓我們看一下代碼錯誤從何而來,看看為什么采樣率是一個主要因素。

是什么讓 ADC 閃閃發光?

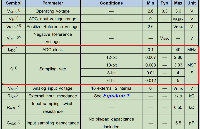

多步 ADC 架構(例如流水線閃存 ADC 或逐次逼近寄存器 (SAR) ADC)分階段將采樣電壓轉換為數字位,每個連續階段都依賴于前一階段的結果。考慮一個基本的流水線閃存高速 ADC,如圖2所示 。這個簡化的 ADC 顯示了兩個轉換級,其中每個連續級都會生成一個數字代碼,可以更精細地估計輸入信號。

所示ADC的操作如下:

第一級對輸入電壓進行采樣,并使用第一級 ADC 將模擬輸入信號粗略地轉換為數字代碼。 此階段的閃存 ADC 的工作原理是使用高速比較器將采樣電壓與由 ADC 的主參考電壓 (V REF ) 生成的靜態參考電壓進行比較。閃存比較器的輸出是代表輸入電壓的溫度計編碼數字樣本。

然后,轉換后的溫度計代碼直接發送到第一級 DAC。該 DAC 輸出模擬電壓,該電壓對應于粗略轉換后的樣本。

從原始輸入電壓中減去第一級 DAC 的輸出就得到量化誤差電壓或殘余電壓 (V RES )。然后將殘留物放大并重新采樣(管道化)以用于第二階段。

第二級 ADC 對 V RES進行量化 ,以獲得原始模擬輸入電壓的更準確(更高分辨率)的估計。

圖 2:流水線閃存 ADC 架構框圖示例。

V RES 創建過程引入了高速決策循環。在一個采樣時鐘周期內,采樣電壓必須由第一級 ADC 轉換為數字代碼。數字代碼必須從第一級 DAC 輸出,從原始輸入電壓中減去,并由第二級重新采樣。高速決策環路會引入代碼錯誤,因為閃存 ADC 中的比較器具有穩定時間,該穩定時間是采樣電壓與 V REF之間的差值的函數 。

更簡單地說,當輸入電壓(V CAP1 )接近比較器的參考電壓(例如7*V REF /8)時,比較器需要更長的時間來穩定。理論上,如果 V CAP1 無限接近比較器的參考電壓,比較器將永遠不會穩定,因為它將在其線性區域中工作。

噪聲會阻止這種情況實際發生,但如果比較器確實需要很長時間才能穩定,則第一級 DAC 可能會使用不正確的數字代碼來輸出量化的模擬電壓。結果是 V RES 與第一級 ADC 的實際數字輸出代碼不匹配。然后,第二級 ADC 轉換錯誤的 V RES ,這會導致代碼錯誤。

文章來源:Embedded

-

轉換器

+關注

關注

27文章

8724瀏覽量

147414 -

數據

+關注

關注

8文章

7080瀏覽量

89175 -

adc

+關注

關注

98文章

6512瀏覽量

545016

發布評論請先 登錄

相關推薦

OpenAI攻克Sora視頻創建錯誤率高難題

PGA300EVM在標定ADC參數時,軟件提示ADC系數計算錯誤,問題出在哪里?

如何評估adc的性能參數

SQL錯誤代碼及解決方案

如何優化adc的采樣率

低α粒子錫膏是如何降低微電子封裝軟錯誤率的?

使用低α粒子錫膏降低微電子封裝的軟錯誤率

量子計算最新突破 微軟與量子計算公司Quantinuum合作實現14000次實驗無錯誤

了解 ADC 代碼錯誤率

了解 ADC 代碼錯誤率

評論