儀表放大器也被稱為INO,正如名字所示,它會放大電平的變化并像其他運放一樣提供一個差分輸出。但和其它普通放大器不同的是,當以完全差分輸入的共模噪聲抑制時,儀表放大器會有著較高的阻抗和不錯的增益。

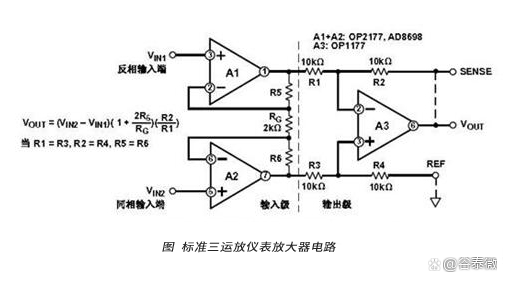

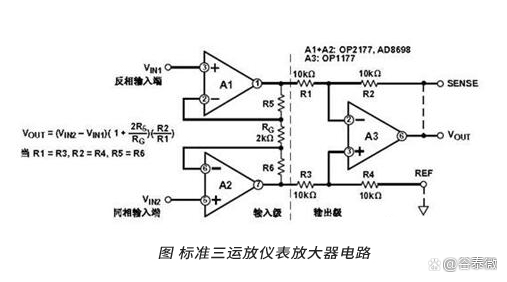

考慮到儀表放大器的IC比普通運放要貴,于是很多工程師就想能否用普通的運放組成儀表放大器?答案是肯定的。使用三個普通運放就可以組成一個儀表放大器。電路如下圖所示:

輸出電壓表達式如圖中所示。

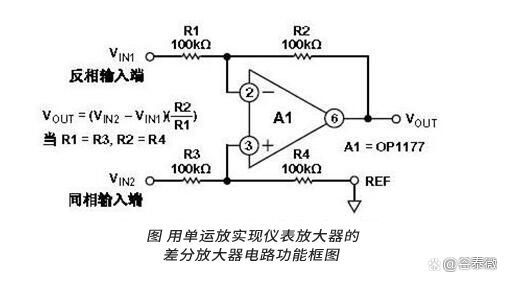

看到這里大家可能會問上述表達式是如何導出的? 為何上述電路可以實現儀表放大器?下面我們就將探討這些問題。在此之前,我們先來看如下我們很熟悉的差分電路:

如果R1 = R3,R2 = R4,則VOUT = (VIN2—VIN1)(R2/R1)

這一電路提供了儀表放大器功能,即放大差分信號的同時抑制共模信號,但它也有些缺陷。首先,同相輸入端和反相輸入端阻抗相當低而且不相等。在這一例子中VIN1反相輸入阻抗等于 100 kΩ,而VIN2同相輸入阻抗等于反相輸入阻抗的兩倍,即200 kΩ。因此,當電壓施加到一個輸入端而另一端接地時,差分電流將會根據輸入端接收的施加電壓而流入。(這種源阻抗的不平衡會降低電路的CMRR。)

另外,這一電路要求電阻對R1 /R2和R3 /R4的比值匹配得非常精密,否則,每個輸入端的增益會有差異,直接影響共模抑制。例如,當增益等于 1 時,所有電阻值必須相等,在這些電阻器中只要有一只電 阻 值 有 0.1% 失 配 , 其CMR便 下 降 到 66 dB(2000:1)。同樣,如果源阻抗有 100 Ω的不平衡將使CMR下降 6 dB。

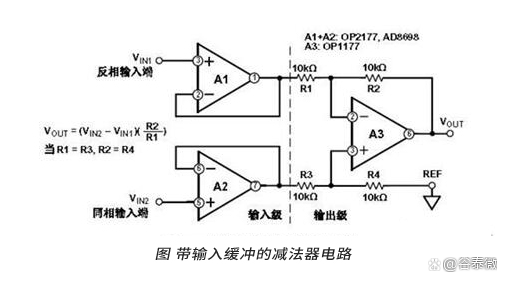

為解決上述問題,我們在運放的正負輸入端都加上電壓跟隨器以提高輸入阻抗。如下圖所示:

以上前置的兩個運放作為電壓跟隨器使用,我們現在改為同相放大器,電路如下所示:

輸出電壓表達式如上圖所示。上圖所示的電路增加增益(A1 和 A2)時,它對差分信號增加相同的增益,也對共模信號增加相同的增益。也就是說,上述電路相對于原電路共模抑制比并沒有增加。

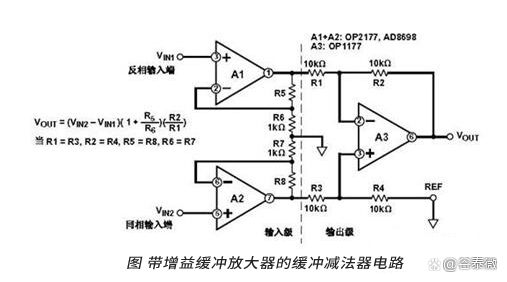

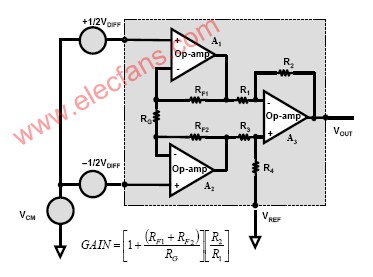

下面,要開始最巧妙的變化了!看電路先:

這種標準的三運放儀表放大器電路是對帶緩沖減法器電路巧妙的改進。像前面的電路一樣,上圖中A1 和A2 運算放大器緩沖輸入電壓。然而,在這種結構中,單個增益電阻器RG連接在兩個輸入緩沖器的求和點之間,取代了帶緩沖減法器電路的R6和R7。由于每個放大器求和點的電壓等于施加在各自正輸入端的電壓,因此,整個差分輸入電壓現在都呈現在RG兩端。因為輸入電壓經過放大后(在A1 和A2的輸出端)的差分電壓呈現在R5,RG和R6這三只電阻上,所以差分增益可以通過僅改變RG進行調整。

這種連接有另外一個優點:一旦這個減法器電路的增益用比率匹配的電阻器設定后,在改變增益時不再對電阻匹配有任何要求。如果R5 = R6,R1= R3和R2 = R4,則VOUT = (VIN2-VIN1)(1+2R5/RG)(R2/R1)由于RG兩端的電壓等于VIN,所以流過RG的電流等于VIN/RG,因此輸入信號將通過A1 和A2 獲得增益并得到放大。然而須注意的是對加到放大器輸入端的共模電壓在RG兩端具有相同的電位,從而不會在RG上產生電流。由于沒有電流流過RG(也就無電流流過R5和R6),放大器A1 和A2 將作為單位增益跟隨器而工作。因此,共模信號將以單位增益通過輸入緩沖器,而差分電壓將按〔1+(2 RF/RG)〕的增益系數被放大。這也就意味著該電路的共模抑制比相比與原來的差分電路增大了〔1+(2 RF/RG)〕倍!

在理論上表明,用戶可以得到所要求的前端增益(由RG來決定),而不增加共模增益和誤差,即差分信號將按增益成比例增加,而共模誤差則不然,所以比率〔增益(差分輸入電壓)/(共模誤差電壓)〕將增大。因此CMR理論上直接與增益成比例增加,這是一個非常有用的特性。

最后,由于結構上的對稱性,輸入放大器的共模誤差,如果它們跟蹤,將被輸出級的減法器消除。這包括諸如共模抑制隨頻率變換的誤差。上述這些特性便是這種三運放結構得到廣泛應用的解釋。

-

電阻器

+關注

關注

21文章

3779瀏覽量

62114 -

緩沖器

+關注

關注

6文章

1921瀏覽量

45473 -

儀表放大器

+關注

關注

17文章

409瀏覽量

71212 -

電壓跟隨器

+關注

關注

10文章

192瀏覽量

32625 -

同相放大器

+關注

關注

0文章

46瀏覽量

8446

發布評論請先 登錄

相關推薦

三運放儀表放大器的放大倍數分析

三運放架構對儀表放大器的制約

能否用普通的運放組成儀表放大器?

能否用普通的運放組成儀表放大器?

評論