Chiplet 使英特爾 PSG 能夠為其 FPGA 添加許多新功能

英特爾可編程解決方案事業部 (PSG) 自 2016 年發布公司首款英特爾 Stratix 10 設備以來,一直依賴小芯片技術來實現其現場可編程門陣列 (FPGA) 。這些 FPGA 使用英特爾的嵌入式多芯片互連橋 (EMIB) 封裝技術將主 FPGA 芯片連接到各種接口和內存小芯片。英特爾繼續使用相同的 EMIB 封裝技術將小芯片集成到其下一代英特爾 Agilex FPGA 中。基于小芯片的設計方法的一項顯著優勢對于英特爾 PSG 尤為重要,即該技術使英特爾能夠快速為其 FPGA 產品系列添加新成員。

Chiplet 使英特爾 PSG 能夠為其 FPGA 添加許多新功能,包括:

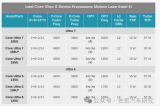

2018 年 2 月:58Gbps PAM4 收發器。

2019 年 8 月:PCIe 4.0 支持。

2019 年 11 月:業界首款擁有超過 1000 萬個邏輯元件的 FPGA。

2022 年 4 月:PCIe 5.0 x16 運行速度為 320 億次傳輸/秒。

2022 年 9 月:直接模擬/數字射頻 (RF) 轉換速度為 640 億次轉換/秒。

2023 年 3 月:116Gbps PAM4 收發器。

2023 年 5 月:PCIe 5.0 和 CXL 硬件支持。

英特爾 PSG 副總裁兼總經理 Deepali Trehan 表示,英特爾 FPGA 中小芯片的功能是客戶決定在其系統設計中使用這些 FPGA 的主要原因。在 FPGA 中使用小芯片使英特爾能夠在其他設備中提供技術先進的功能(例如上面列出的功能)之前,降低開發風險并大大縮短開發時間。

BittWare 就是此類長期客戶之一,該公司開發基于外圍組件互連 Express (PCIe) 總線標準的基于 FPGA 的加速卡。BittWare 開發這些基于英特爾 FPGA 的 PCIe 加速卡已有至少 20 年的歷史。這些 PCIe 卡用于計算加速、網絡和傳感器融合,并在邊緣應用中經常與 Intel Xeon CPU 配合使用,用作高性能數據處理器和輸入/輸出 (I/O) 引擎。

Molex BittWare 業務部門副總裁兼總經理 Craig Petrie 指出,在 FPGA 中使用小芯片可以比其他方式更快地為 FPGA 帶來新的 I/O 功能。組件級的快速上市使得 BittWare 的板級產品也能實現同樣快速的上市時間。Petrie 特別指出,小芯片使 BittWare 能夠快速連續提供具有 PCIe 4.0、PCIe 5.0、Compute Express Link (CXL) 和高速以太網端口的加速卡。

Petrie 表示:“Tiles(小芯片)解決了一個大問題。”他解釋說,如果必須為每個新的 I/O 標準(例如各代 PCIe 和以太網標準)設計新的單片 FPGA,則不可避免地會出現一些細微的變化在FPGA的整體設計上與上一代相比。這些細微的變化需要 BittWare 方面進行設計修訂,而這些修訂將需要額外的設計時間。通過使用小芯片來實現這些 I/O 功能,FPGA 的中心部分(主硅芯片)可以保持不變。因此,小芯片允許英特爾等半導體供應商更快地適應這些新的 I/O 功能,并且無需重新設計主 FPGA 芯片。“這降低了我們的設計風險,”BittWare 的 Petrie 解釋道。

Liquid-Markets-Solutions (LMS) 聯合創始人、總裁兼首席執行官 Seth Friedman 對于基于小芯片的 FPGA 也有類似的看法。他的公司開發了一種名為“überNIC”的網絡接口卡(NIC),該卡最初是為金融市場的高速交易領域開發的。在這個市場中,每一微秒都很重要,因為較慢的交易根本無法獲得與較快的交易那么多的利潤。因此,LMS 開發了一個快速、基于硬件的完整以太網協議棧,并將其體現在其網卡上的 Intel FPGA 中,以滿足金融界的低延遲要求。

而LMS 很快發現,許多其他涉及電信、計算、廣播、研究和學術界的公司也需要同樣快速的 NIC,用于從測試設備到自動視覺系統等應用。云服務提供商、超大規模提供商的數據中心也需要高速 NIC。

Friedman 指出,FPGA 中的小芯片通過 PCIe 5.0 接口端口為他的公司帶來了上市時間優勢,并且將為 CXL 1.1 和 2.0 帶來同樣的優勢。“這一切都歸功于小芯片技術,”弗里德曼解釋道。他還指出了另一個對 LMS 很重要的小芯片優勢:收發器密度。使用基于小芯片的 FPGA 和許多高速以太網收發器,LMS 可以將兩到四倍數量的光纖對插入其 überNIC 之一。

然而,LMS 采用英特爾 FPGA 的目的不僅僅是 I/O 優勢。如上所述,FPGA 中的可編程硬件允許該公司構建高速以太網協議引擎,但 FPGA 中還留有空間來整合對最終客戶具有巨大價值的附加功能。例如,LMS 實現了英特爾的精確時間測量 (PTM) 功能,該功能在英特爾第 4代中找到。一代 Xeon 可擴展 CPU,集成到其 überNIC 卡中。PTM 可以通過獨立的本地時鐘精確協調多個組件之間的事件。這種精確時間功能對于為高速金融交易添加時間戳非常有利,而且在數據流必須具有精確時間戳的情況下也很有用。“傳統的 NIC 無法提供此功能,”弗里德曼說道。該任務需要 FPGA 中提供的可編程硬件。

Bittware 和 LMS 等客戶是促使小芯片保留在英特爾 FPGA 路線圖上的因素之一。目前,英特爾 PSG 的 FPGA 依賴于 EMIB 封裝技術和英特爾開發的稱為高級接口總線 (AIB) 的總線協議,英特爾隨后將其作為開源、免版稅標準貢獻給 CHIPS 聯盟。然而,英特爾 PSG 路線圖超出了目前 EMIB 和 AIB 的使用范圍。

英特爾的 Trehan 表示:“UCIe 對于我們的下一代 FPGA 非常重要。”他指的是目前由 UCI Express 開發的通用 Chiplet Interconnect Express (UCIe) 標準,UCI Express 是英特爾去年 3 月與 Advanced Semiconductor ,包括Engineering Inc. (ASE)、AMD、Arm、Google Cloud、Meta、微軟公司、高通公司、三星和臺積電(TSMC)等公司共同成立的行業聯盟和非營利組織。通過將 UCIe 作為小芯片互連標準,Trehan 設想了一個小芯片市場,由多個代工廠使用不同的半導體工藝節點制造,然后英特爾可以使用該市場來組裝具有更奇特電子功能(包括高功率鎵)的 FPGA 和其他 IC 類型氮化物 (GaN) 驅動器和高速光學 I/O 直接集成到 FPGA 封裝中。

小芯片在高端半導體設備中的使用現已成熟,并以 FPGA 開創的多年實踐經驗為后盾。Chiplet 現在也出現在 CPU 和 GPU 中。TIRIAS Research 認為,小芯片的使用將在這些高端設備中繼續并增長,以添加新特性和新功能、提高性能并延長摩爾定律的壽命,同時滿足客戶的上市時間需求。由全行業聯盟 UCIe 開發的小芯片間接口標準的出現只會加速這一趨勢。與此同時,單片結構仍然是最便宜的封裝替代方案,并將繼續在低成本半導體器件的制造中占據主導地位。

審核編輯:劉清

-

FPGA

+關注

關注

1629文章

21729瀏覽量

602997 -

收發器

+關注

關注

10文章

3424瀏覽量

105961 -

封裝技術

+關注

關注

12文章

548瀏覽量

67981 -

以太網協議棧

+關注

關注

0文章

2瀏覽量

6349 -

chiplet

+關注

關注

6文章

431瀏覽量

12584

原文標題:?英特爾 Chiplet 戰略加速 FPGA 開發

文章出處:【微信號:ICViews,微信公眾號:半導體產業縱橫】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

英特爾推出全新英特爾銳炫B系列顯卡

英特爾考慮出售Altera股權

英特爾推出集成光學計算互聯OCI Chiplet芯片

英特爾CEO:AI時代英特爾動力不減

BittWare提供基于英特爾Agilex? 7 FPGA最新加速板

英特爾率先推出業界高數值孔徑 EUV 光刻系統

英特爾宣布代工虧損70億美元

英特爾旗下FPGA公司Altera正式亮相

英特爾成立全新獨立運營的FPGA公司Altera

英特爾旗下Altera正式獨立運作,FPGA市場將迎來怎樣的巨變?

英特爾vPro讓AI PC造福企業

Chiplet使英特爾PSG能夠為其FPGA添加許多新功能

Chiplet使英特爾PSG能夠為其FPGA添加許多新功能

評論