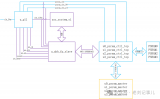

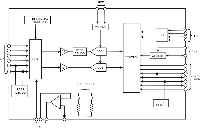

為了控制會(huì)議音箱的同步問題,最簡單的辦法就是采用FPGA芯片來控制多個(gè)音箱時(shí)鐘同步。

在此提一下京微齊力的FPAG HME-HR02PN3Q32,因?yàn)槭窃谑覂?nèi)應(yīng)用,所以HME-HR02PN3Q32的工作溫度(0℃,85℃)完全可以滿足應(yīng)用需求。設(shè)計(jì)中需要多個(gè)IO控制多個(gè)音箱,HME-HR02PN3Q32是QFN32封裝,有25個(gè)獨(dú)立IO,支持可編程總線保持、可編程上拉電阻、可編程下拉電阻、可編程延遲、可編程驅(qū)動(dòng)能力以及可編程slew-rate控制,以及熱插拔的優(yōu)化,同時(shí)還支持支持驅(qū)動(dòng)阻抗匹配(Rs),完全滿足應(yīng)用IO設(shè)計(jì)要求。

HME-HR02PN3Q32集成1個(gè)通用PLL,8個(gè)全局時(shí)鐘,包含4個(gè)主時(shí)鐘及4個(gè)次時(shí)鐘,以及全局和輔助時(shí)鐘網(wǎng)絡(luò)以提供可靠,有效且低偏斜的時(shí)鐘管理與綜合,可以在HqFpga軟件中對(duì)PLL進(jìn)行重配置時(shí)鐘頻率或者相位,可以滿足不同音箱的同步時(shí)鐘需求。另外1-3K邏輯資源,采用LUT4查找表,可高達(dá)98%的資源利用率。

HME-HR02PN3Q32使系統(tǒng)設(shè)計(jì)師在降低成本的同時(shí)又能夠滿足不斷增長的應(yīng)用要求。對(duì)于類似會(huì)議音箱此類的的小型應(yīng)用,HME-HR02PN3Q32無疑是理想的選擇。

注:如涉及作品版權(quán)問題,請(qǐng)聯(lián)系刪除。

-

FPGA

+關(guān)注

關(guān)注

1644文章

21993瀏覽量

615343 -

京微齊力

+關(guān)注

關(guān)注

0文章

30瀏覽量

5897

發(fā)布評(píng)論請(qǐng)先 登錄

京微齊力二十年專注FPGA芯片鑄就卓越

京微齊力HME-P2系列FPGA的pSRAM讀寫例程分析

國芯思辰|同步采樣24位模數(shù)轉(zhuǎn)換器軟硬件替換ADS1174應(yīng)用于關(guān)口表

京微齊力亮相2025慕尼黑上海電子展

微芯Microchip PolarFire? SoC FPGA通過AEC-Q100汽車級(jí)認(rèn)證

國芯思辰| 替代ADC08D1000,模數(shù)轉(zhuǎn)換器SC1281在通信系統(tǒng)中的應(yīng)用

預(yù)告|思爾芯邀您共聚2025玄鐵RISC-V生態(tài)大會(huì)

醫(yī)療環(huán)境穩(wěn)定時(shí)鐘信號(hào)可選擇國芯思辰MEMS振蕩器,替換SiTime

對(duì)外MBA師生走進(jìn)科創(chuàng)企業(yè)京微齊力

京微齊力亮相ICCAD-Expo 2024

基于 FPGA 的會(huì)議系統(tǒng)設(shè)計(jì)

京微齊力亮相2024慕尼黑上海電子展

評(píng)論