MCU 對應用主導地位的挑戰(zhàn)已經(jīng)開始。具有片上固定功能處理子系統(tǒng)的現(xiàn)場可編程邏輯器件(FPGA),也就是片上系統(tǒng) (SoC) FPGA,最近已成為高端處理應用的潛在競爭者。這就提出了一個問題:隨著應用性能要求的不斷提高,SoC FPGA 會成為更廣泛應用中的挑戰(zhàn)者,還是 MCU 會發(fā)展以更好地與 SoC FPGA 競爭?如果您正在考慮一種新設計,那么今天哪種方法最適合您——MCU 還是 SoC FPGA?

本文將快速回顧 SoC FPGA 與 MCU 相比的一些主要優(yōu)勢和劣勢。它還將探討 MCU 中的一些最新創(chuàng)新,這些創(chuàng)新使它們更加靈活并且能夠更好地應對 SoC FPGA 提供的一些關鍵優(yōu)勢。有了這些信息,您將能夠在下一個設計中更好地在 MCU 和 SoC FPGA 之間進行選擇。

SoC FPGA 將新的靈活性與熟悉的處理系統(tǒng)相結合

SoC FPGA 結合了兩個世界的優(yōu)點。首先,SoC FPGA 提供了一個熟悉的處理系統(tǒng)——CPU——來執(zhí)行熟悉的順序處理算法。事實上,許多 SoC FPGA 已經(jīng)融合在普遍的 ARM 處理器架構上,以形成其“固定功能”處理子系統(tǒng)的基礎。這利用了廣泛的 ARM 兼容工具、知識產權內核 (IP 內核) 和支持技術的生態(tài)系統(tǒng),使開發(fā)成為一個非常熟悉的過程。

SoC FPGA 還為順序處理提供了一種靈活的可編程替代方案。可編程結構幾乎可以實現(xiàn)您需要的任何硬件功能,以增強處理子系統(tǒng)中的順序處理能力。可編程結構本質上是并行的,因為多個硬件模塊可以同時運行,或者并行運行,其中邏輯是重復的,或者以流水線方式運行,其中算法被分成多個階段,以便處理重疊。與順序方法相比,這些方法中的任何一種都會產生巨大的吞吐量增益。

當算法的一部分需要高性能時,SoC FPGA 特別有用,該算法可以使用并行或流水線(或組合)技術在硬件中實現(xiàn)。讓我們看一個示例設備,以更好地了解這將如何在實際系統(tǒng)中工作。

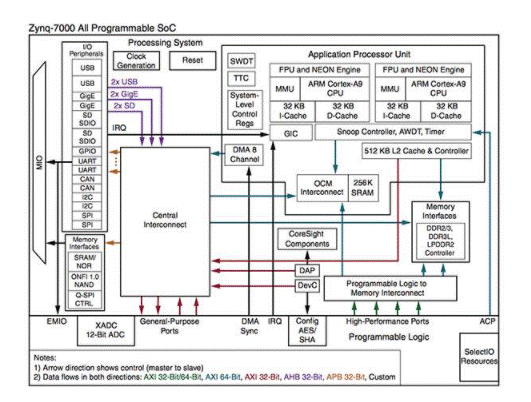

Xilinx Zynq -7000SoC FPGA 框圖如下圖 1 所示。該圖的頂部顯示了片上包含的所有固定功能塊。這些模塊實現(xiàn)了完整的雙核 ARM 處理器應用處理單元以及大量支持互連總線、外設、存儲器和片外接口。可編程邏輯部分顯示在圖表的最底部,可通過各種系統(tǒng)級接口訪問。該組織對 SoC FPGA 的可編程邏輯方面進行了新的改進,因為即使沒有可編程邏輯,固定功能元件也可以全部工作。這意味著處理器系統(tǒng)可以“啟動”然后配置可編程邏輯。以前,非面向 SoC 的方法需要首先配置可編程邏輯,然后處理器才能啟動。

圖 1:Xilinx Zynq SoC FPGA 框圖。(由賽靈思提供)

事實上,代碼開發(fā)人員可以將 SoC 中的可編程邏輯視為一種硬件資源,用于加速在處理器上實現(xiàn)時速度太慢的代碼部分。一名設計團隊成員可能將他們的活動集中在創(chuàng)建程序員要求的硬件加速上,或者程序員可能能夠自己實現(xiàn)硬件。無論哪種方式,算法都成為開發(fā)的重點,具有多種可用的實現(xiàn)選項。

當有多個面向性能的算法同時運行時,SoC 方法似乎效果最好。SoC FPGA 取得重大成功的一個應用領域是復雜的圖像處理。這些算法通常可以流水線化和/或并行化,使其成為 FPGA 加速的良好候選者。如果處理器還需要處理片上和片外的高帶寬流量(可能使用高速串行接口和大型片外緩沖存儲器),那么從處理器卸載低級任務的額外硬件支持也可能會帶來回報大紅利。

對 SoC FPGA 的多核響應

還有其他方法可以為圖像處理等應用程序實現(xiàn)并行和流水線實現(xiàn)。MCU 供應商采用的一種方法是在片上實現(xiàn)多個處理引擎(多核),以允許設計人員分解復雜的算法。當每個處理器的體系結構相同時,可以很容易地采用復雜的算法并將其分解為多個片段,每個片段在不同但功能相同的處理器上執(zhí)行。

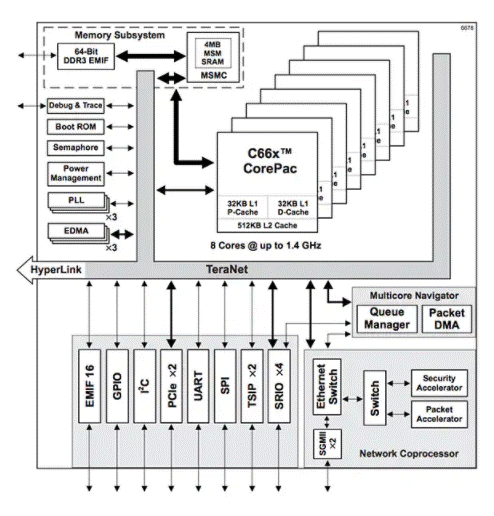

例如,德州儀器(TI)提供TMS320C66x多核定點和浮點數(shù)字信號處理器(DSP),該處理器具有八個 DSP 處理器以及一個網(wǎng)絡協(xié)處理器和一個多核導航器,以使用硬件隊列簡化數(shù)據(jù)傳輸(圖 2 )。DSP 內核為音頻、視頻、分析、工業(yè)自動化和媒體處理等各種復雜算法提供非常高的處理能力。

圖 2:德州儀器多核 DSP 框圖。(德州儀器提供)

多核架構的代碼開發(fā)有點類似于使用 SoC FPGA 時的代碼開發(fā),只是硬件加速是由 DSP 內核而不是可編程結構完成的。當一個核心無法足夠快地實現(xiàn)算法時,只需讓另一個核心來處理它。繼續(xù)這樣做,直到您用完內核或達到您的性能目標。可能需要調整和優(yōu)化以獲得最后一點的功率/性能效率,但一些更高級的工具可以通過提供有助于優(yōu)化過程的性能和功率配置文件來提供幫助。

雙核MCU

多核方法不必僅用于最高性能的應用程序。通常,SoC FPGA 可以在需要優(yōu)化功率和處理能力的性能限制較少的應用中找到。由于可編程結構可用于實現(xiàn)部分算法,因此實現(xiàn)所需的總功率可能大大低于高端 DSP 或多核解決方案。

MCU 制造商也發(fā)現(xiàn)了這一趨勢,并通過將雙核處理器在單個設備上工作來做出回應。在某些情況下,同時使用高性能處理器和低性能處理器。這允許高性能處理器實現(xiàn)算法中更復雜的部分,而性能較低的處理器則可以處理不太復雜的管理任務。與高性能內核相比,性能較低的處理器可以在大部分時間處于活動狀態(tài),使用更少的功率。(請注意,多核系統(tǒng)可以使用類似的方法,只使用動態(tài)達到目標性能水平所需的內核。這實現(xiàn)起來有點復雜,但如果算法需要,最終會非常有效各種性能水平在短時間內變化很大。)

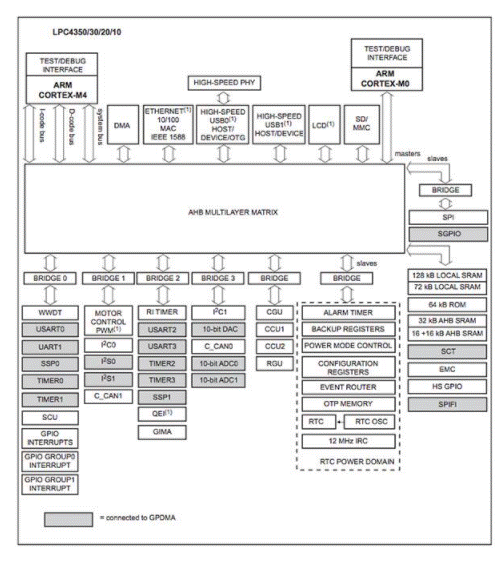

NXP Semiconductors LPC4350是同時利用高性能和低性能處理器的雙核 MCU 的一個示例。如圖 3 所示,其下方有一個 ARM Cortex-M4 和一個 Cortex-M0。M4 用于高性能任務,而 M0 可用于常用管理功能。事實上,M4 子部分甚至可以在不需要時斷電,并在處理請求需要時通電。這種方法適用于只需要定期但需要快速響應處理數(shù)據(jù)的算法。例如,安全攝像機上的圖像處理在圖像變化時可能非常繁重,但在圖像靜止時則不需要。

圖 3:NXP 雙核 MCU 框圖。(恩智浦提供)

即使是低端也是可編程的

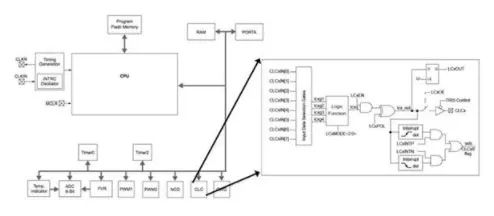

不要以為只有高端和中端 MCU 才會增加新的花樣以提高靈活性。甚至低端 MCU 也在增加可編程功能,這可能不是作為對 SoC FPGA 的回應,而是作為一種將少量外部邏輯“片上”的方式,就像可編程邏輯設備幾十年來一直在做的那樣。Microchip PIC10F320 _添加了可編程邏輯,位于可配置邏輯單元 (CLC) 塊中。圖 4 顯示了 PIC10F320 的框圖以及 CLC 的更詳細視圖。CLC 可以基于器件輸入、內部時鐘、內部外設和寄存器位實現(xiàn)各種簡單的邏輯功能。CLC 甚至可以在低功耗模式下運行,使其成為喚醒事件的便捷來源,從而在不需要 MCU 進行處理時最大程度地節(jié)省功耗。

圖 4:具有可編程邏輯框圖的 Microchip MCU。(由微芯片提供)

CLC 在 PIC10F320 上特別有用,因為它只有幾個引腳。充分利用這些引腳并消除一些外部邏輯可以對電路板空間要求產生很大影響。即使在 PAL 和 CPLD 的早期階段,可編程邏輯的一大優(yōu)勢也是如此。現(xiàn)在隨著低端 MCU 將可編程邏輯放在芯片上,也許我們會在 MCU 旁邊看到更少的低端 PLD。這不就是一個新的轉折嗎!

總之,MCU 和 SoC FPGA 解決了類似的應用問題,并開始爭奪應用主導地位。目前,挑戰(zhàn)主要出現(xiàn)在應用領域的高端,但最近的創(chuàng)新可能會擴大 MCU 和可編程設備之間的應用重疊。

有你想看的精彩 至芯科技FPGA就業(yè)培訓班——助你步入成功之路、8月12號西安中心開課、歡迎咨詢! 基于FPGA協(xié)處理器的算法及總線連接 基于RISC-V加速器實現(xiàn)FPGA CNN異構的控制方案

掃碼加微信邀請您加入FPGA學習交流群

歡迎加入至芯科技FPGA微信學習交流群,這里有一群優(yōu)秀的FPGA工程師、學生、老師、這里FPGA技術交流學習氛圍濃厚、相互分享、相互幫助、叫上小伙伴一起加入吧!

點個在看你最好看

原文標題:SoC FPGA與MCU主要優(yōu)勢和劣勢對比

文章出處:【微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

-

FPGA

+關注

關注

1646文章

22059瀏覽量

619131

原文標題:SoC FPGA與MCU主要優(yōu)勢和劣勢對比

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

評論