SDRAM是現(xiàn)代計算機(jī)中使用的一種主要內(nèi)存類型。它具有高速和大容量的特點(diǎn),能夠滿足高要求的性能和數(shù)據(jù)存儲需求。然而,SDRAM的高速也意味著在設(shè)計中需要嚴(yán)格遵循走線等長規(guī)則。這篇文章將介紹SDRAM走線等長規(guī)則,以及為什么需要遵守這些規(guī)則,以及如何應(yīng)用這些規(guī)則來確保設(shè)計的正確性和可靠性。

一、SDRAM概述

SDRAM是同步動態(tài)隨機(jī)存儲器的縮寫,它是動態(tài)隨機(jī)存儲器(DRAM)的一種。它的寄存器和內(nèi)部電路是與系統(tǒng)時鐘同步的,這意味著處理器和SDRAM之間的通信是高度協(xié)調(diào)的。SDRAM的存儲單元由存儲器芯片和SDRAM控制器共同管理,用于將數(shù)據(jù)存儲在處理器可以訪問的位置。

SDRAM有多種標(biāo)準(zhǔn),包括DDR(Double Data Rate)、DDR2、DDR3和DDR4。每個標(biāo)準(zhǔn)都具有不同的物理規(guī)格和數(shù)據(jù)傳輸速率。DDR4是現(xiàn)代計算機(jī)中使用的最新型號,它具有更高的頻率和更大的容量。

二、SDRAM走線等長規(guī)則簡介

SDRAM設(shè)計中最基本的規(guī)則之一是走線等長規(guī)則,這意味著處理器和SDRAM之間的信號路徑應(yīng)該盡可能的相等。這是因為互聯(lián)線路的長度和信號傳輸速度之間存在密切的關(guān)系。較長的線路意味著較高的延遲和更慢的信號傳輸速度,這可能導(dǎo)致信號在到達(dá)目的地之前過早失效或變形。

如何實現(xiàn)SDRAM走線等長規(guī)則?

首先,需要設(shè)計者進(jìn)行精確的電路布局,確保處理器和SDRAM之間的信號的物理延遲相等。這意味著信號線的長度必須盡可能的相同,并且需要使信號線的路徑盡可能的平直和短。

其次,需要嚴(yán)格控制布線目標(biāo)信噪比。布線時使用低噪聲的電源和地線,同時還需要使用屏蔽和濾波器來降低噪聲和射頻干擾的影響。這些措施有助于保持信噪比和信號完整性,從而確保信號在SDRAM和處理器之間傳輸?shù)那逦蜏?zhǔn)確。

最后,對于DDR4這樣的高帶寬SDRAM,處理器和存儲器模塊之間需要有一個DDRx時鐘總線。設(shè)計時必須使時鐘和信號路線盡可能的短,以確保數(shù)據(jù)的傳輸速率和時序正確。

三、為什么需要遵守SDRAM走線等長規(guī)則?

嚴(yán)格遵守SDRAM走線等長規(guī)則是非常重要的,因為它可以保證信號的準(zhǔn)確性和穩(wěn)定性。違反規(guī)則可能導(dǎo)致信號失真和傳輸錯誤,從而導(dǎo)致系統(tǒng)性能下降或系統(tǒng)崩潰。由于SDRAM是大容量存儲器,它通常用于存儲關(guān)鍵數(shù)據(jù)和代碼。任何數(shù)據(jù)損壞或錯誤都可能導(dǎo)致崩潰或安全漏洞,因此必須保證數(shù)據(jù)的準(zhǔn)確性和可靠性。

另外,符合SDRAM走線等長規(guī)則還可以提高系統(tǒng)的穩(wěn)定性和可靠性。由于SDRAM是高速存儲器,它需要處理大量數(shù)據(jù),并且必須與其他系統(tǒng)組件進(jìn)行高速通信。如果SDRAM走線不平衡或長度不相等,可能會導(dǎo)致數(shù)據(jù)傳輸錯誤,從而破壞系統(tǒng)的完整性。如果數(shù)據(jù)被破壞或丟失,可能需要重新啟動整個系統(tǒng),從而導(dǎo)致時間和資源的浪費(fèi)。

四、結(jié)語

本文介紹了SDRAM走線等長規(guī)則及其重要性。SDRAM是現(xiàn)代計算機(jī)系統(tǒng)中使用的重要內(nèi)存類型之一,因此需要進(jìn)行嚴(yán)格的設(shè)計和布線。精確和符合規(guī)則的布線可以確保SDRAM信號的準(zhǔn)確性和可靠性,保證系統(tǒng)的高性能和穩(wěn)定性。未來,我們需要繼續(xù)探索和發(fā)展SDRAM的技術(shù),以滿足不斷提高的計算機(jī)性能和存儲需求。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

-

處理器

+關(guān)注

關(guān)注

68文章

19259瀏覽量

229652 -

SDRAM

+關(guān)注

關(guān)注

7文章

423瀏覽量

55205 -

存儲器

+關(guān)注

關(guān)注

38文章

7484瀏覽量

163763

發(fā)布評論請先 登錄

相關(guān)推薦

pcb設(shè)計中常見的走線等長要求是什么

1、在做 PCB 設(shè)計時,為了滿足某一組所有信號線的總長度滿足在一個公差范圍內(nèi),通常要使用蛇形走線將總長度較短的信號線繞到與組內(nèi)最長的信號線長度公差范圍內(nèi),這個用蛇形

使用SDRAM外設(shè)的時候,數(shù)據(jù)線、地址線、控制線是單獨(dú)等長還是所有類型的線路一起等長?

請問使用SDRAM外設(shè)的時候,數(shù)據(jù)線、地址線、控制線是單獨(dú)等長還是所有類型的線路一起等長?

LT

發(fā)表于 04-10 06:37

怎么設(shè)置手工不同網(wǎng)絡(luò)等長走線

各位大俠:想請問下,如何在Protel ***中設(shè)置手工不同網(wǎng)絡(luò)之間的等長走線,越詳細(xì)越好!謝謝!

發(fā)表于 09-15 22:44

請問Altium designer中單線等長和差分等長以及保持原間距走線和等間距走線該怎么用?

跪求Altium designer中單線等長和差分等長以及保持原間距走線和等間距走線是怎么使用的

發(fā)表于 09-25 05:35

用allegro使二條時鐘線等長的設(shè)計置

為了使二個SDRAM的時鐘線等長,設(shè)置等長的方法有很多,在這里我們只為了二條時鐘線等長來學(xué)習(xí)如何

發(fā)表于 06-21 11:57

?1534次閱讀

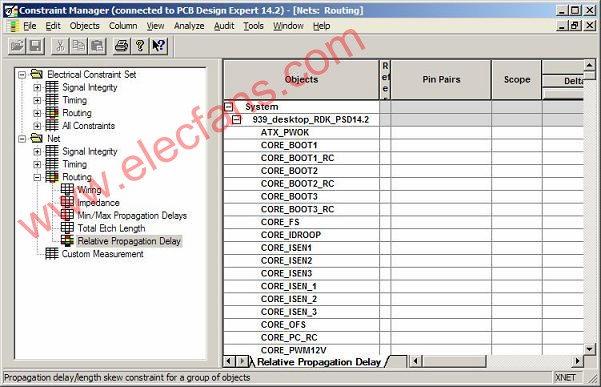

教您在Allegro中設(shè)置走線等長進(jìn)階

對于簡單走線等長在以前文檔中都有涉及這里不再復(fù)述了,下面內(nèi)容將給大家介紹一下有關(guān)Xnet等長的設(shè)置問題, 如現(xiàn)在主板DD

發(fā)表于 06-28 09:38

?2.9w次閱讀

走線高速信號走線的九大規(guī)則

規(guī)則一:高速信號走線屏蔽規(guī)則 如上圖所示: 在高速的PCB設(shè)計中,時鐘等關(guān)鍵的高速信號線,走需要

PCB設(shè)計做等長走線的目的是什么

在PCB設(shè)計中,等長走線主要是針對一些高速的并行總線來講的。 由于這類并行總線往往有多根數(shù)據(jù)信號基于同一個時鐘采樣,每個時鐘周期可能要采樣兩次(DDRSDRAM)甚至4次,而隨著芯片運(yùn)行頻率的提高

PCB設(shè)計中如何實現(xiàn)等長走線

在 PCB 設(shè)計中,等長走線主要是針對一些高速的并行總線來講的。由于這類并行總線往往有多根數(shù)據(jù)信號基于同一個時鐘采樣,每個時鐘周期可能要采樣兩次(DDR SDRAM)甚至 4 次,而隨

sdram走線等長規(guī)則

sdram走線等長規(guī)則

評論