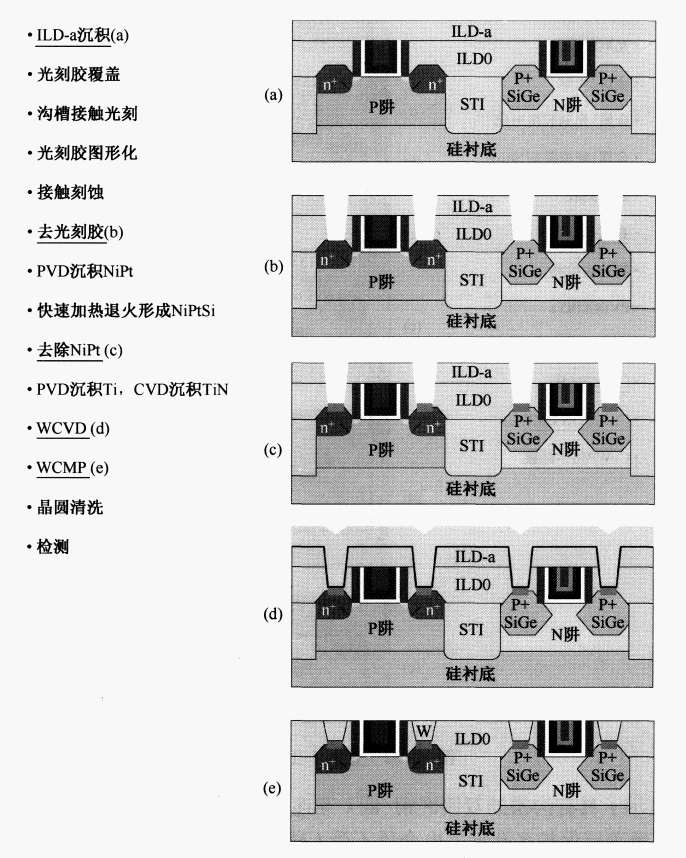

摻雜少量鉑元素的鎳硅化物的穩定性也不盡相同,還與物質的具體結構有關,舉個例子來說,NiPtSi,比NiSi要穩定。

填充了接觸溝槽的鎢被研磨到金屬柵極的同一平面,如下圖e)所示。

由于接觸溝槽只與凸起的源/漏極接觸,所以接觸溝槽深度很淺,這樣使得過刻蝕的控制簡單。

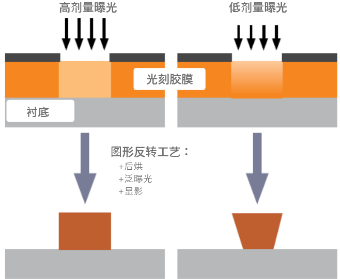

從版圖的角度考慮,代替了圓形和橢圓形接觸孔的溝槽式接觸,簡化了光刻膠圖形化過程。

但是一項技術的改革往往會帶來一些新的問題,比如說,這會在接觸刻蝕中,過刻蝕到STI氧化層而導致W尖刺問題。

由于鎢栓塞的長度顯著縮短,所以栓塞的電阻大大降低(因為電阻的值與長度為正比關系)。

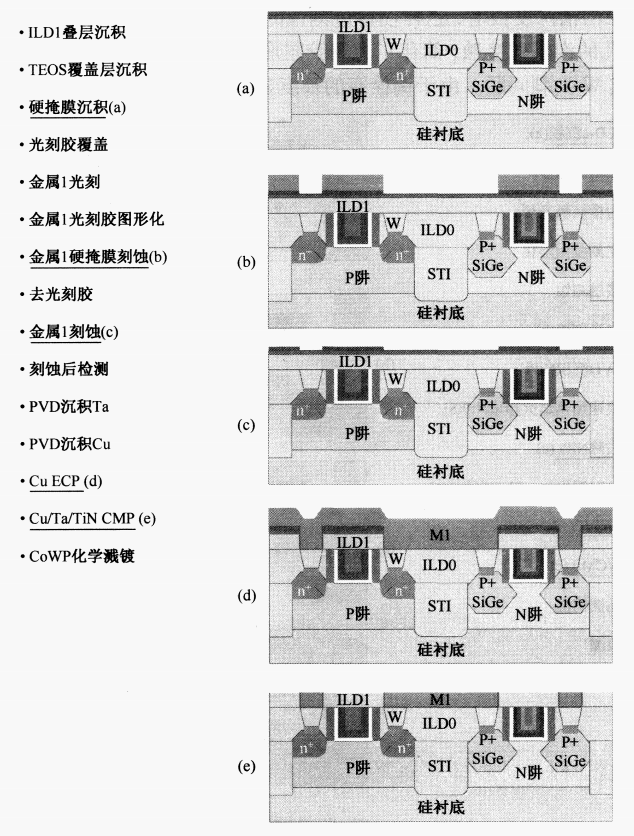

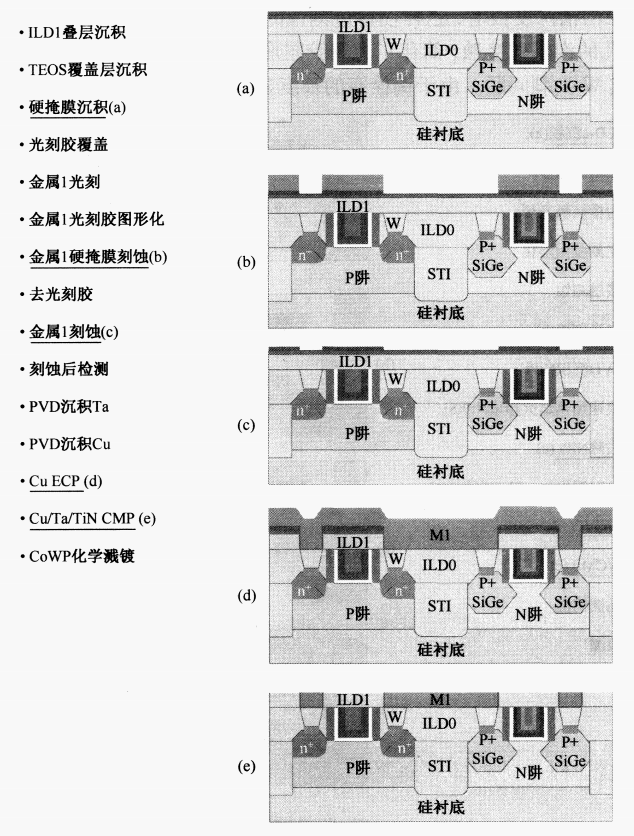

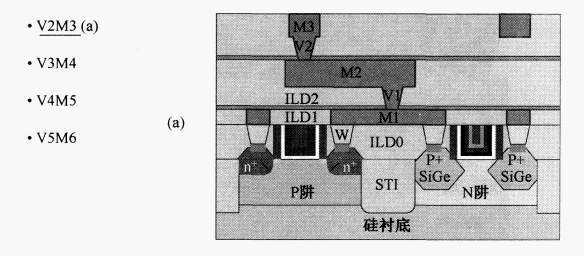

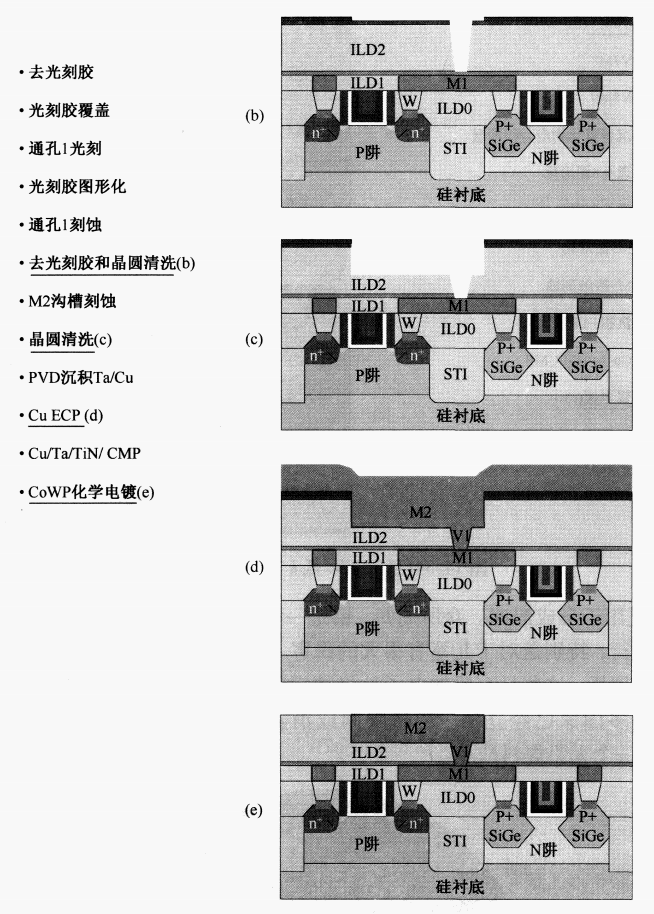

在下面的結構圖中顯示了金屬1(M1)的形成工藝過程。

在這個過程當中,該工藝使用了覆蓋在TEOS上的硬掩膜TiN保護了多孔低h介質不受光刻膠去除工藝過程的損傷。

多孔低k電介質的化值(2.2?2.5)通常比碳硅酸鹽玻璃的么值(CSG,k為2.7~2.9)低。

多孔低k電介質可以通過PECVD摻碳氧化硅電介質形成,通過將摻雜的濃度進行相應的精確控制,可以保證其中含有小于2nm的孔和高達40%的孔隙度。這些是在CVD時通過在氣流中加入致孔劑實現的。

CVD預沉積,可以是三甲基硅烷或四甲基硅烷,致孔劑可以是冰片烯或a-松油烯。

鉭阻擋層和銅籽晶層通過具有金屬離化等離子體PVD工藝獲得。

由于銅的沉積量非常大,所以傳統的方法已經不再適用了,所以大量的銅沉積利用化學電鍍(ECP)工藝。

在經過銅退火工藝后,利用金屬CMP去除不需要的銅、鉭阻擋層和TiN硬掩膜CMP研磨停止于TEOS覆蓋層,這樣可以保護多孔低k電介質不受CMP漿料的污染。

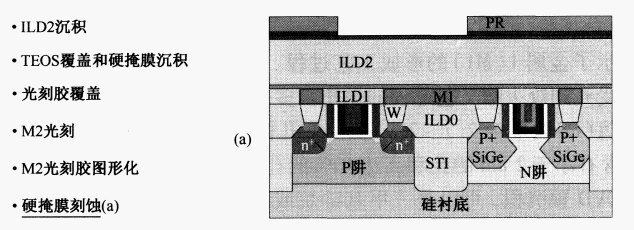

下圖顯示了具有溝槽的雙鑲嵌銅/低k互連工藝。

通常金屬硬掩膜TiN、TEOSPECVD氧化物或TEOS覆蓋層保護多孔低k電介質不受CMP漿料的污染。

因為這樣相當于在多孔低k電介質的外表面加上了幾層的保護膜,今兒產生了一個相對穩定的小環境。

并且在此基礎上,可以利用自對準CoWP化學電鍍的技術來防止銅的擴散并提高電遷移抵抗能力,通過這種技術從而提高了IC芯片的可靠性。

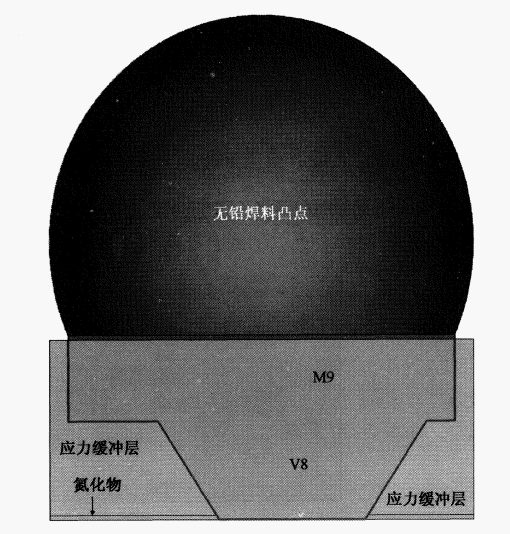

下圖顯示了從M3金屬層(見下圖(a))到M9金屬層(見下圖(c))的銅/低k互連工藝過程。該過程基本上是下圖所示的通孔工藝過程的重復。

鉛(Pb)廣泛用于形成焊球。眾所周知,鉛是一種污染物,可以影響心臟、骨骼、腸、腎和神經系統的正常運行,特別是對于兒童有很大的傷害。

大量使用IC芯片的過時電子儀器形成每年萬噸級的電子垃圾,這些具有鉛的電子垃圾填埋給環境污染帶來潛在風險,因此,像日本、歐洲和中國等許多國家已經立法,嚴格限制或消除鉛在半導體和所有電子行業中的使用。下圖顯示了一個無鉛焊料凸點。

審核編輯:劉清

-

接觸器

+關注

關注

63文章

1197瀏覽量

64469 -

CMP

+關注

關注

6文章

151瀏覽量

26047 -

光刻機

+關注

關注

31文章

1151瀏覽量

47440 -

IC芯片

+關注

關注

8文章

248瀏覽量

26267 -

ICT技術

+關注

關注

0文章

44瀏覽量

10182

原文標題:半導體行業(二百)之ICT技術(十)

文章出處:【微信號:FindRF,微信公眾號:FindRF】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

Futurrex高端光刻膠

光刻膠殘留要怎么解決?

Microchem SU-8光刻膠 2000系列

光刻膠

光刻膠在集成電路制造中的應用

默克推出用于芯片制造的新一代環保光刻膠去除劑

光刻膠的原理和正負光刻膠的主要組分是什么

光刻膠黏度如何測量?光刻膠需要稀釋嗎?

如何簡化光刻膠圖形化過程呢?

如何簡化光刻膠圖形化過程呢?

評論