1、 引言

數字通信時,一般以一定數目的碼元組成一個個“字”或“句”,即組成一個個“幀”進行傳輸,因此幀同步信號的頻率很容易由位同步信號經分頻得出,但每個幀的開頭和末尾時刻卻無法由分頻器的輸出決定。為此,幀同步的任務就是要給出這個“開頭”和“末尾”的時刻。通常提取幀同步信號有兩種方法:一類是在信息流中插入一些特殊的碼組作為每幀的頭尾標記。另一類則不需要加入碼組,而是利用數據碼組本身之間彼此不同的特性實現同步。這里采取第一種方法——連貫式插人法實現幀同步。所謂連貫式插入法就是在每幀開頭插入幀同步碼。所用的幀同步碼為巴克碼,巴克碼是一種具有特殊規律的非周期序列,其局部自相關函數具有尖銳的單峰特性,這些特性正是連貫式插入幀同步碼組的主要要求之一。因此,這里提出幀同步系統的FPGA 設計與實現。

2 、幀同步系統的工作原理

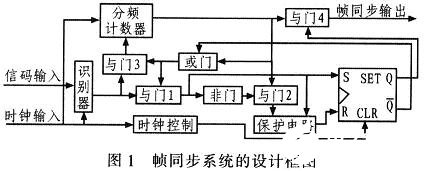

實現幀同步的關鍵是把同步碼從一幀幀數據流中提取出來。本設計的一幀信碼由39位碼元組成。其中的巴克碼為1110010七位碼,數據碼由32位碼元組成。只有當接收端收到一幀信號時,才會輸出同步信號。幀同步系統的設計框圖如圖1所示。

幀同步系統工作狀態分捕捉態和維持態。同步未建立時系統處于捕捉狀態,狀態觸發器Q端為低電平,一旦識別器輸出脈沖,由于Q端為高電平,經或門使與門1輸出”1”,同時經或門使與門3輸出也為”1”,對分頻計數器模塊清零。與門1一路輸出至觸發器的S端,Q端變為高電平,與門4打開,幀同步輸出脈沖。系統由捕捉態轉為維持態,幀同步建立。

當幀同步建立后,系統處于維持態。假如此時分頻器輸出幀同步脈沖,而識別器卻沒有輸出,這可能是系統真的失去同步,也可能是偶然干擾引起的,因此在電路中加入一個保護電路。該保護電路也是一個分頻計數器,只有在連續若干次接收不到幀同步信號時,系統才會認為同步狀態丟失,由于丟失同步的概率很小,因此這里系統設置分頻計數器值為5,也就是說連續5幀接收不到幀同步信號,系統才認為丟失同步狀態。當然分頻值可設置其他值,但該值越大,同步維持態下漏識別概率也越大。與門1的一路輸出置5分頻器的使能端,使之開始計數,當計數滿時會輸出一個脈沖使狀態觸發器置零,從而無幀同步信號輸出,同步電路又進入捕捉態。

3 、幀同步電路功能模塊的建模與實現

3.1 巴克碼識別模塊

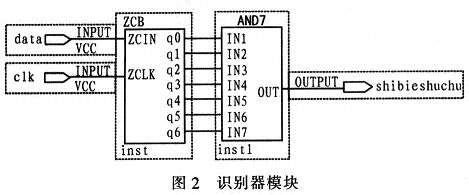

該模塊的功能主要是把幀同步碼巴克碼從數據流中識別出來。識別器模塊如圖2所示。

圖2中第1部分模塊ZCB主要完成串并轉換和移位功能,由7個D觸發器和3個非門實現。第2部分模塊AND7作用:只有當巴克碼1110010準確輸人時,識別器的輸出才會為”1”。因為輸出的巴克碼識別信號將直接影響后續同步保護電路,因此準確地輸出巴克碼,才能避免產生假同步現象。AND7可簡潔準確識別巴克碼。圖3為巴克碼識別模塊仿真圖,其中,bakeshibie為識別器的輸出;fenpin39為39分頻計數器的輸出端;zin為輸入的數據;zclk為時鐘信號。

幀同步系統的工作原理及如何基于FPGA實現其設計

3.2 分頻計數器模塊

本設計采用2個帶清零的分頻計數器,分別為39分頻計數器和5分頻計數器。其中,39分頻計數器可滿足7位巴克碼+4字節數據的要求。當39分頻器輸出一個脈沖時,識別器也應輸出一個脈沖,只要其相位對應輸出,就能提取出幀同步信號。

39分頻計數器的仿真圖如圖4所示,其中clk為時鐘信號端;clr為時鐘清零端;output為輸出端。

幀同步系統的工作原理及如何基于FPGA實現其設計

3.3 同步保護模塊

系統進入維持態時就需要同步保護電路保護幀同步信號。這部分電路由時鐘控制模塊、基本RS觸發器模塊和5分頻計數器組成,其中,時鐘控制模塊和基本RS觸發器模塊的主要功能是狀態轉換和控制輸出幀同步脈沖。對于RS觸發器值得注意的是:如果R=0和 S=“0后同時發生由0至1的變化”,則輸出端Q和Q都要由1向0轉換,Q和Q端輸出就會為任意態,這就是冒險競爭現象。當產生冒險競爭后,由于觸發器的輸出為任意態,就會導致整個系統的輸出為任意態。解決方法是在系統中加入時鐘控制模塊控制觸發器的復位端,確保不出現任意狀態,使系統工作狀態穩定。5分頻器在識別器模塊無輸出時,這可能是系統真正失步也可能是偶爾干擾所致,只有連續5次這種情況系統才會真正認為失步。保護模塊仿真圖如圖5所示,其中, zhengout為幀同步輸出信號;clk為時鐘信號;data為輸入的信碼;q為RS觸發器的Q端;fenpin39為39分頻計數器的輸出端。

幀同步系統的工作原理及如何基于FPGA實現其設計

4、 幀同步系統頂層文件設計

所謂頂層文件設計就是把所涉及到的各個模塊放在一起,形成一個便于閱讀的圖形方式,在編譯各個模塊時,如果設計沒有錯誤。系統就會創建一個代表該模塊的符號文件,可以被高層設計所調用。本設計中各模塊通過VHDL語言進行設計,在 QuartusⅡ開發軟件下編譯通過。采用Altera公司Cvclone系列的EP1C12Q240C8器件,并且幀同步電路僅用到該器件不到1%的邏輯單元。頂層設計圖形如圖6所示。圖6中,ZCB和AND7(七輸入與門)為巴克碼識別器;CLKCONTR為時鐘控制器;FENPIN5為5分頻器計數器;FENPIN39為39分頻器計數器;RS_CLK為RS觸發器。

幀同步系統的工作原理及如何基于FPGA實現其設計

實驗結果分析:在Quartus II環境下,時鐘clk的周期為200μs,當時鐘周期設定的值很小時,比如納秒級別,系統則極易出現冒險競爭現象,因此要將時鐘周期的值設定的大一些。data為輸入的數據流,為了便于仿真,只在數據流中加入3組巴克碼。bakeshibie為巴克碼識別器的輸出,當巴克碼出現后,觸發器的Q端變為高電平,系統進入維持態,此時5分頻計數器開始計數,若在未計滿5次時再次出現巴克碼,則5分頻計數器重新開始計數,若計滿5次仍未出現巴克碼,則系統徹底丟失同步狀態,Q端變為低電平,系統進入捕捉態。總體設計時序仿真圖如圖7所示。由于此幀同步系統要應用在DPSK解調中,所以幀同步系統仿真的時鐘頻率要與DPSK解調的時鐘頻率一致。仿真時要注意碼元的傳輸方向即巴克碼是高位先發送還是低位先發送,這將影響到仿真質量。

幀同步系統的工作原理及如何基于FPGA實現其設計

5、 結論

詳細闡述各模塊功能,實現方法及仿真圖形,系統對幀同步碼(巴克碼)作出嚴格限制,即系統只有在嚴格收到幀同步碼后才會有幀同步信號輸出,提高系統的可靠性。保護電路設計有效降低漏同步和假同步的概率,時鐘控制的RS觸發器保證了同步系統狀態的正確轉換。同步系統各項技術指標均符合要求,工作正確可靠,有較高使用價值。

有你想看的精彩 至芯科技FPGA就業培訓班——助你步入成功之路、8月12號西安中心開課、歡迎咨詢! 基于FPGA的CNN加速項目案例解析 基于FPGA協處理器的算法及總線連接

掃碼加微信邀請您加入FPGA學習交流群

歡迎加入至芯科技FPGA微信學習交流群,這里有一群優秀的FPGA工程師、學生、老師、這里FPGA技術交流學習氛圍濃厚、相互分享、相互幫助、叫上小伙伴一起加入吧!

點個在看你最好看

原文標題:幀同步系統的工作原理及如何基于FPGA實現其設計

文章出處:【微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

-

FPGA

+關注

關注

1629文章

21748瀏覽量

603866

原文標題:幀同步系統的工作原理及如何基于FPGA實現其設計

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

永磁同步電機的工作原理 永磁同步電機與異步電機的區別

永磁同步電機工作原理是什么?它有什么優勢?

旋轉變壓器的工作原理和作用

同步降壓轉換器的工作原理和作用

交流永磁同步電機工作原理及結構

直流伺服系統的結構與工作原理

同步磁阻電動機的工作原理與結構特點

同步計數器的主要類型和工作原理

基于 FPGA 的光纖混沌加密系統

GPS衛星同步時鐘的工作原理及應用場景介紹

幀同步系統的工作原理及如何基于FPGA實現其設計

幀同步系統的工作原理及如何基于FPGA實現其設計

評論