本節(jié)開始簡單介紹后端流程。后面會(huì)以實(shí)際例程說明后端的基本操作。

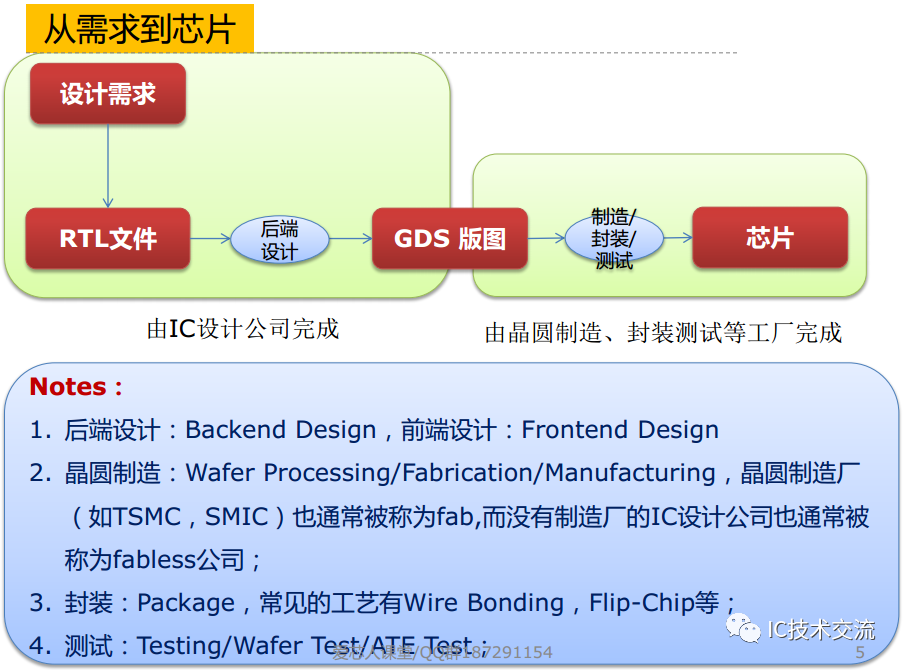

簡單來說后端就是將RTL變?yōu)镚DS版圖,再交由晶圓廠(TSMC臺(tái)積電和SMIC中芯國際)生產(chǎn)制造。大多數(shù)IC設(shè)計(jì)公司都是fabless公司,做到GDS這一步就OK。

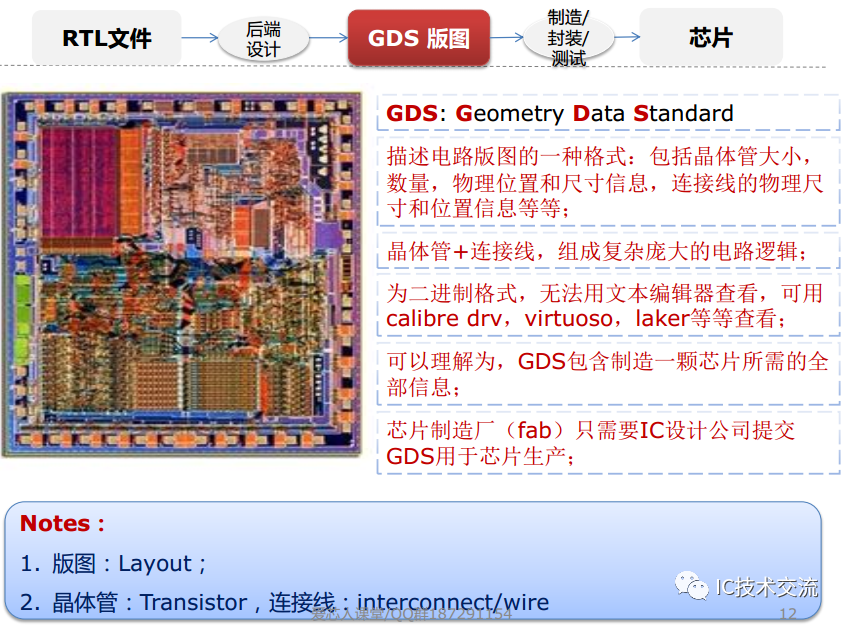

GDS:Geometry Data Standard。它是描述電路版圖的一種格式:包括晶體管大小,數(shù)量,物理位置和尺寸信息,連接線的物理尺寸和位置信息等等。晶體管+連接線組成龐大的電路邏輯。一般GDS可通過calibre,virtuoso,laker等查看。

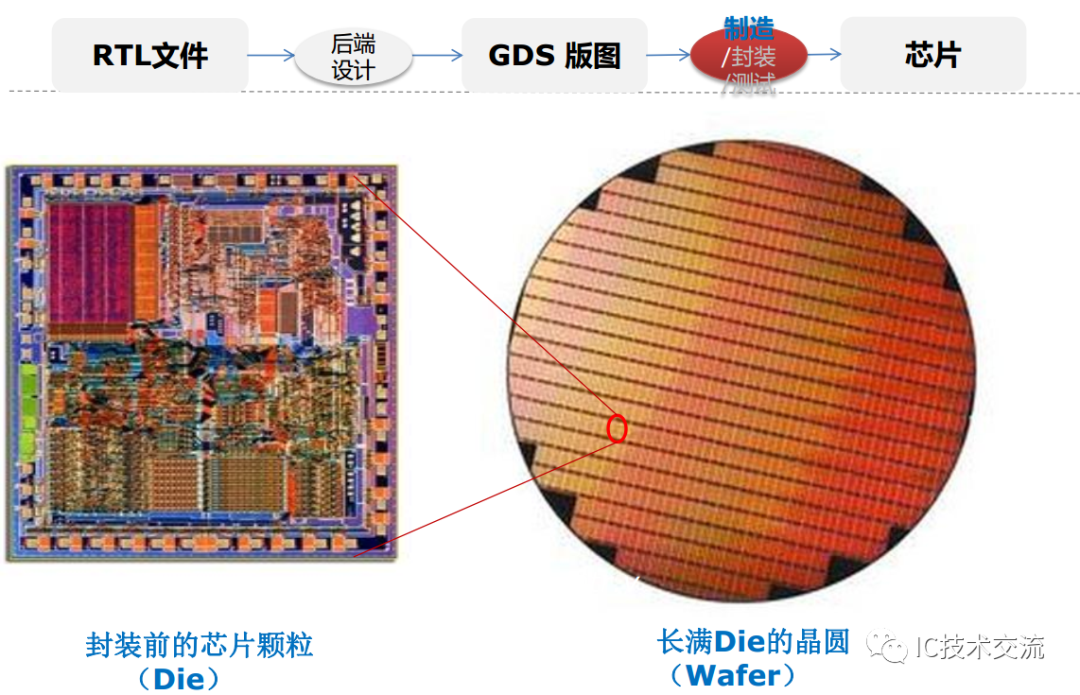

GDS交由晶圓廠后,在一片wafer上切割成多個(gè)小塊,每塊為一個(gè)Die,就是芯片的最小核心。

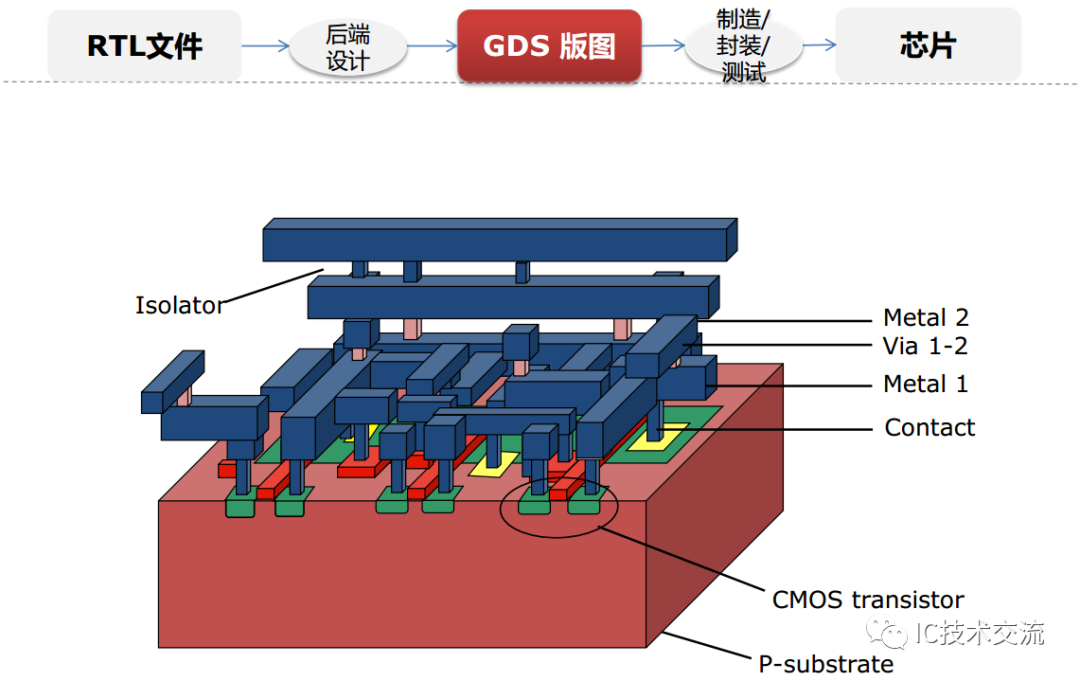

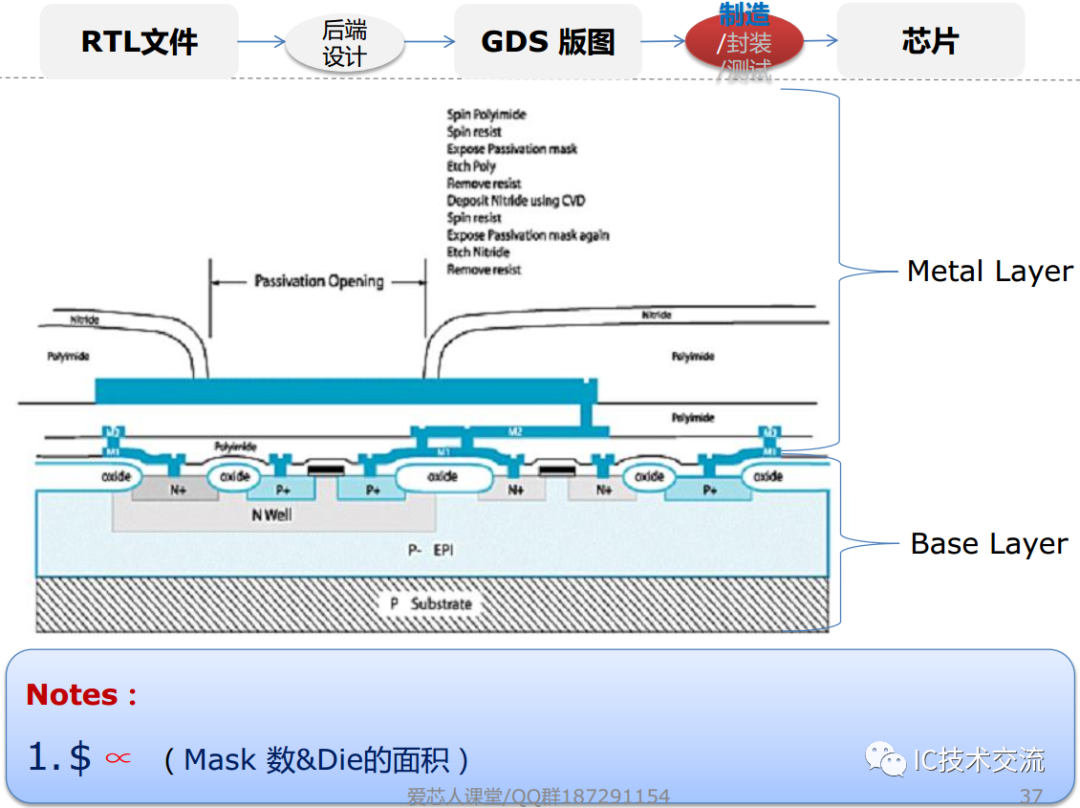

真實(shí)的芯片結(jié)構(gòu)如下圖所示。最底層是晶體管結(jié)構(gòu),晶體管接口和連接線的接觸部分叫Contact。Contact上面是Metal金屬層,金屬層就是連接線,密密麻麻的晶體管很多,因此連線分了好幾層才能走通,一層的連接線要穿到其它層就需要打過孔(Via),就像搭積木一樣實(shí)現(xiàn)整個(gè)電路。每層連線之間都插有Isolator隔離。

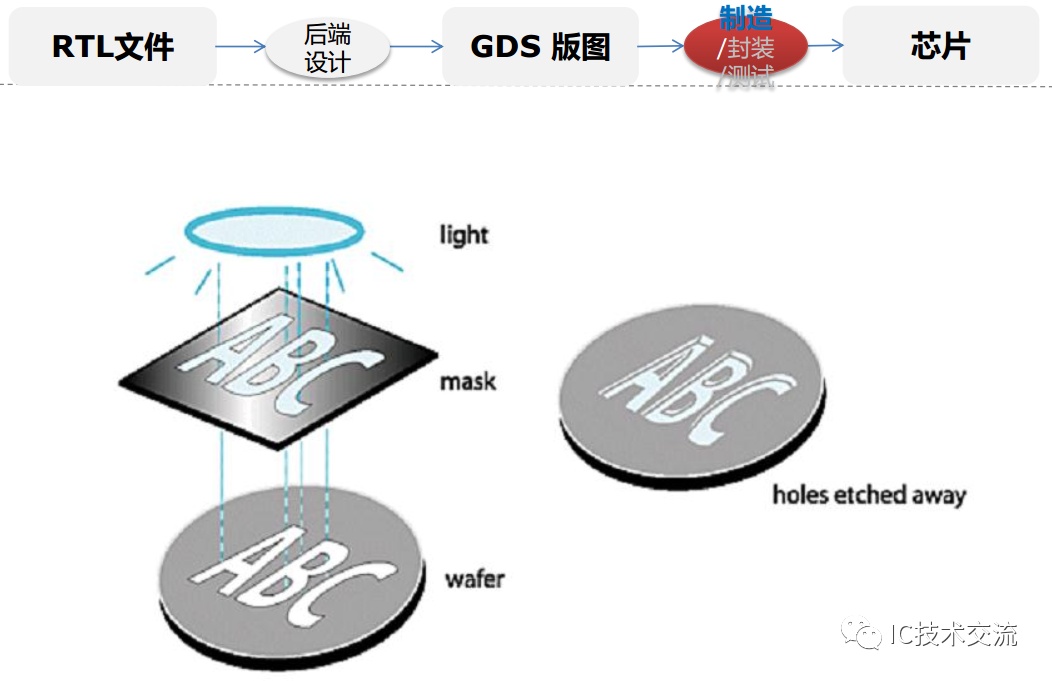

至于電路的具體制作過程如下所示。特殊頻譜的光可以蝕刻電路,通過掩膜(mask),照射在wafer上,wafer涂有光刻膠,被照射的地方被腐蝕,剩下的部分形成電路。

流片成本很高,絕大部分是Mask(掩膜)的費(fèi)用,Die面積XMask數(shù)就是主要的流片成本。

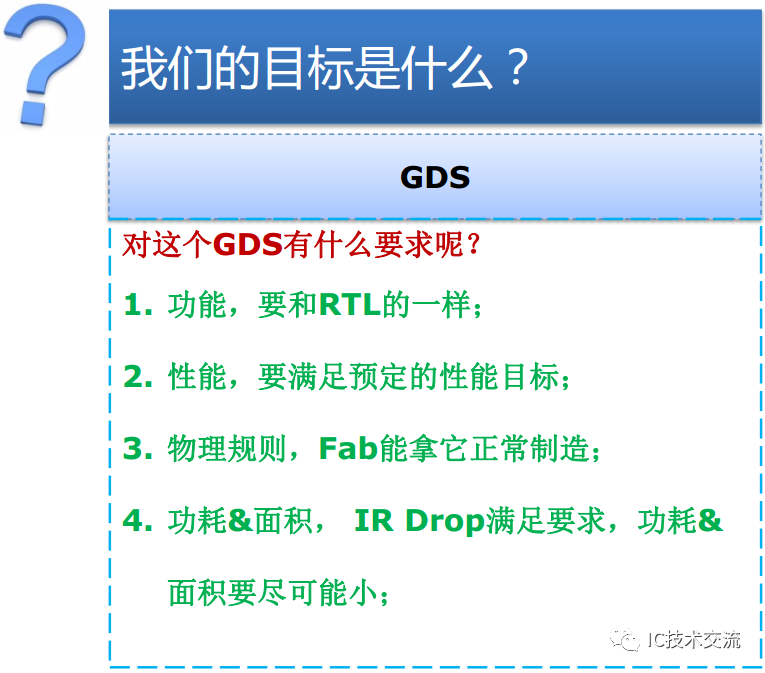

從RTL到GDS版圖,要遵守以下要求,符合要求的GDS才能拿去流片

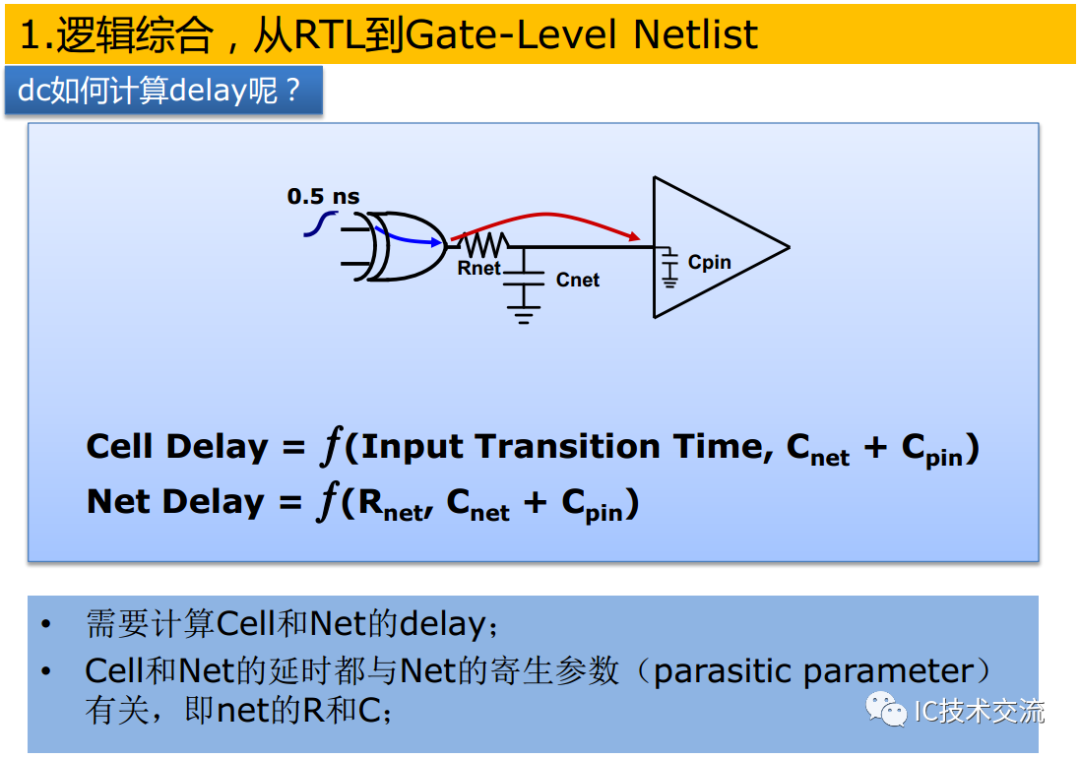

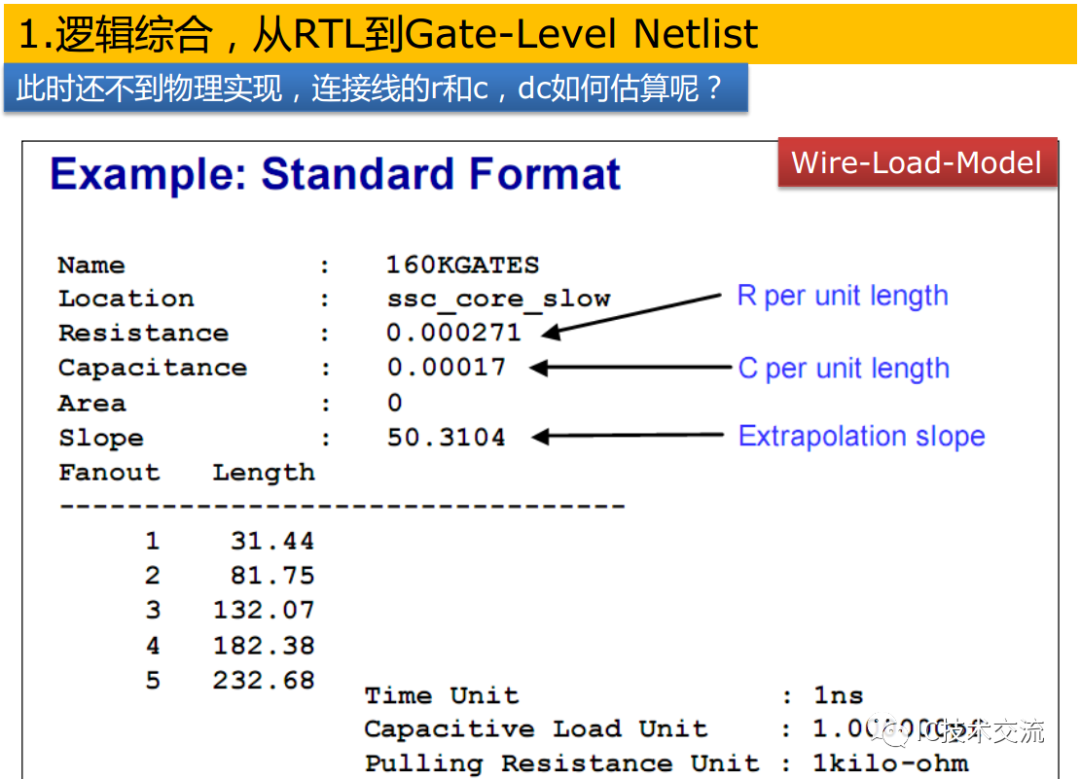

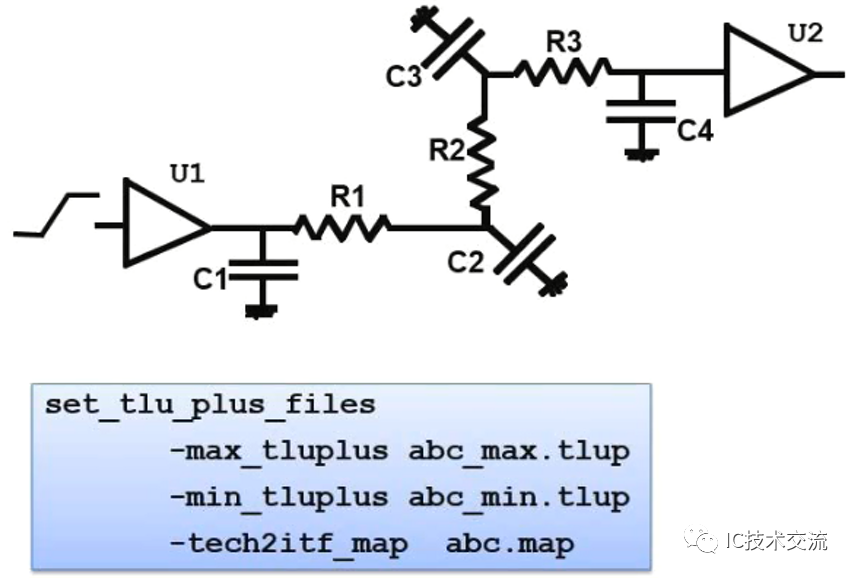

后端第一步是將RTL+SDC約束轉(zhuǎn)換為網(wǎng)表,該步驟通過綜合實(shí)現(xiàn)。通常工具會(huì)先將RTL轉(zhuǎn)換為GTECH格式,然后再將GTECH轉(zhuǎn)換為工藝庫中的標(biāo)準(zhǔn)單元。整體來看是分兩步走。轉(zhuǎn)換為門級網(wǎng)表的過程中,綜合工具會(huì)對RTL進(jìn)行修改和優(yōu)化,這些修改記錄保存在svf文件。svf文件在后面的FM形式驗(yàn)證中會(huì)被使用。轉(zhuǎn)換后的Netlist要滿足設(shè)置的約束(包括時(shí)序,面積,功耗)。此外邏輯綜合要滿足sdc約束下的setup timing,不需要理會(huì)hold timing。常用的工具有synopsys的Design Compiler和cadence的RTL Compiler。邏輯綜合涉及時(shí)序問題,延遲計(jì)算使用線負(fù)載模型(RC寄生參數(shù))因?yàn)榫C合還沒有涉及到布局布線,因此timing通常是不準(zhǔn)的。下圖給出了delay延遲的計(jì)算。

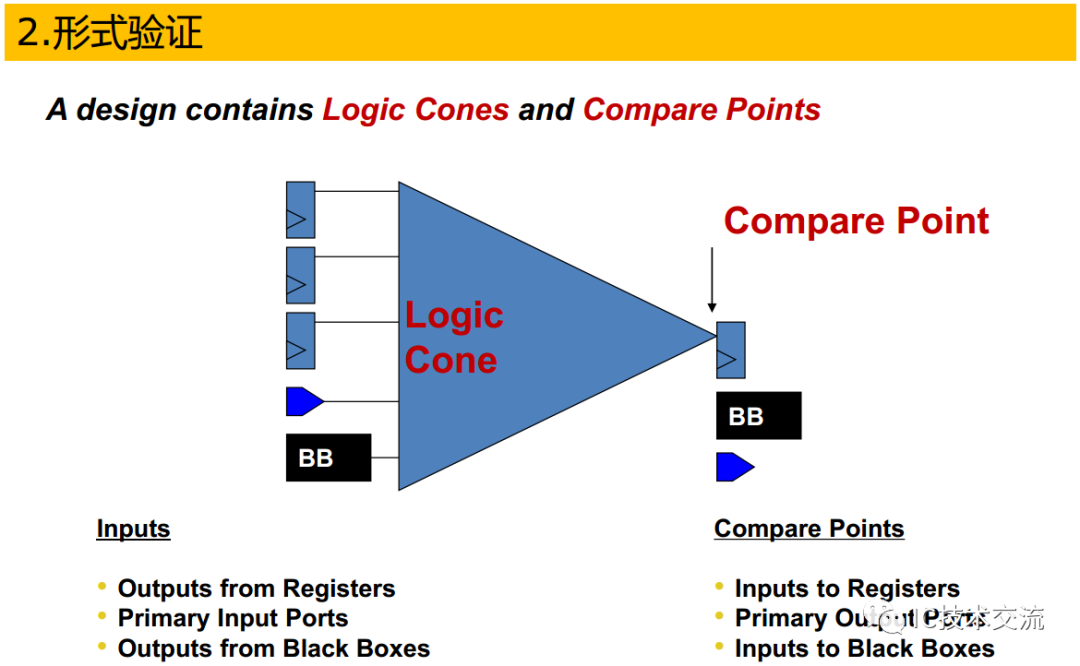

線延遲的計(jì)算通過長度衡量,長度越長RC值越大,扇出能力越弱。綜合工具吐出Netlist網(wǎng)表后,需要進(jìn)行FM形式驗(yàn)證,比對RTL和網(wǎng)表在功能上是否等價(jià),常用的工具有synopsys的formality(fm)和Cadence的Conforml(lec)

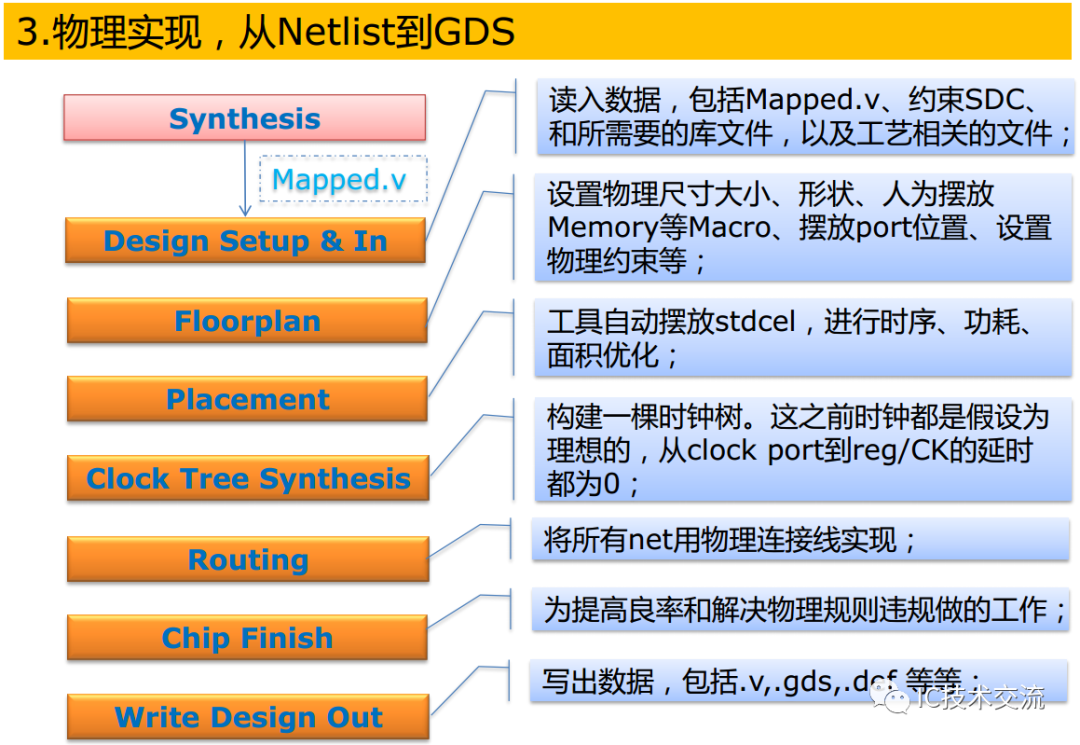

如果FM通過了,那么下一步進(jìn)行物理實(shí)現(xiàn):從Netlist到GDS。通常需要經(jīng)過以下步驟:

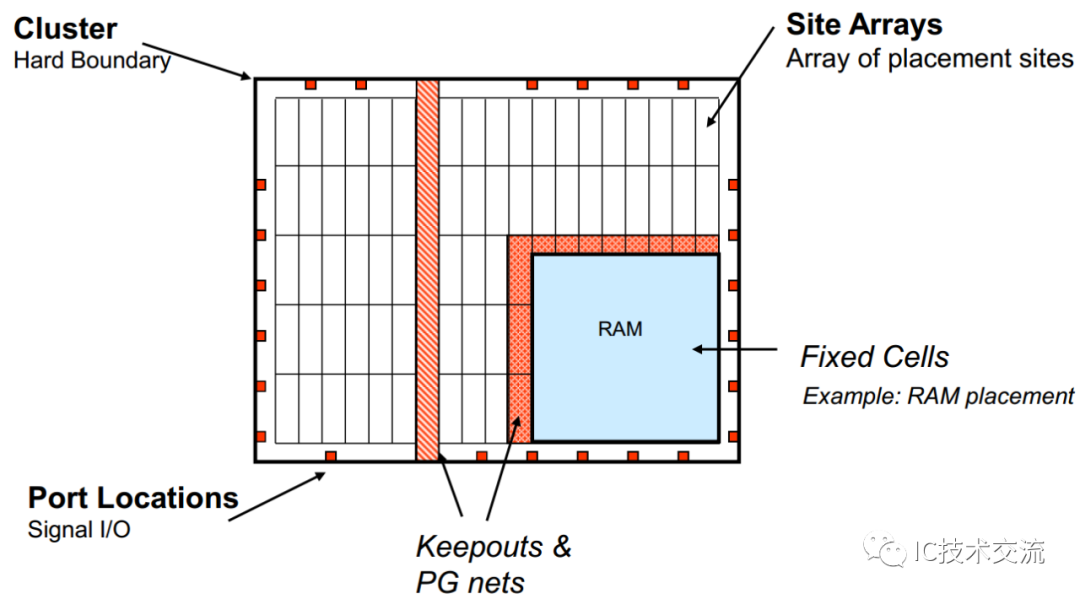

綜合之后網(wǎng)表和約束已經(jīng)有了,下一步進(jìn)行ICC布局布線。Design Setup & In步驟中讀入相關(guān)的網(wǎng)表、SDC和所需的工藝庫文件。Floorplan步驟設(shè)置尺寸大小,擺放port位置,設(shè)置物理約束。Placement步驟中由工具自動(dòng)擺放stdcel,進(jìn)行時(shí)序、功耗、面積優(yōu)化。Clock Tree Synthesis構(gòu)建時(shí)鐘樹,這之前時(shí)鐘都是假設(shè)為理想的,從clock port到reg/CK的延時(shí)都為0。對于時(shí)序分析而言,時(shí)鐘樹長出來之前所有的Timing問題其實(shí)都不準(zhǔn)的,hold無需關(guān)注,setup需留有余量,因?yàn)椴季植季€的影響,時(shí)序會(huì)再次變化。Routing步驟中將所有net用物理連接線實(shí)現(xiàn)。Chip Finish步驟中為提高良率和解決物理規(guī)則違規(guī)對芯片做一些特殊處理。Write Design Out將所需的文件導(dǎo)出。

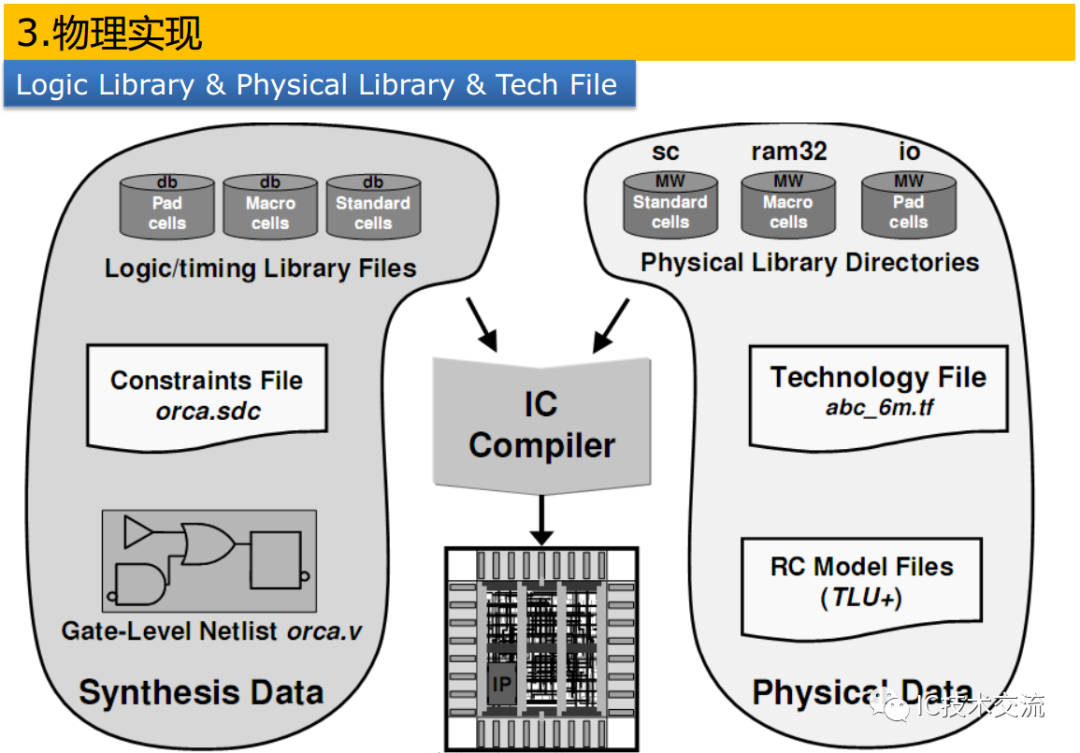

上圖中給出ICC執(zhí)行所需的兩類文件:

1、一類是DC綜合時(shí)的文件,包括library的db文件、sdc約束文件、綜合后的網(wǎng)表文件;

2、一類是物理數(shù)據(jù)文件,包括library中db文件對應(yīng)的Milkyway文件,技術(shù)文件(abc_6m.tf),RC模型文件(TLU+)用于提取寄生參數(shù)計(jì)算線延遲。

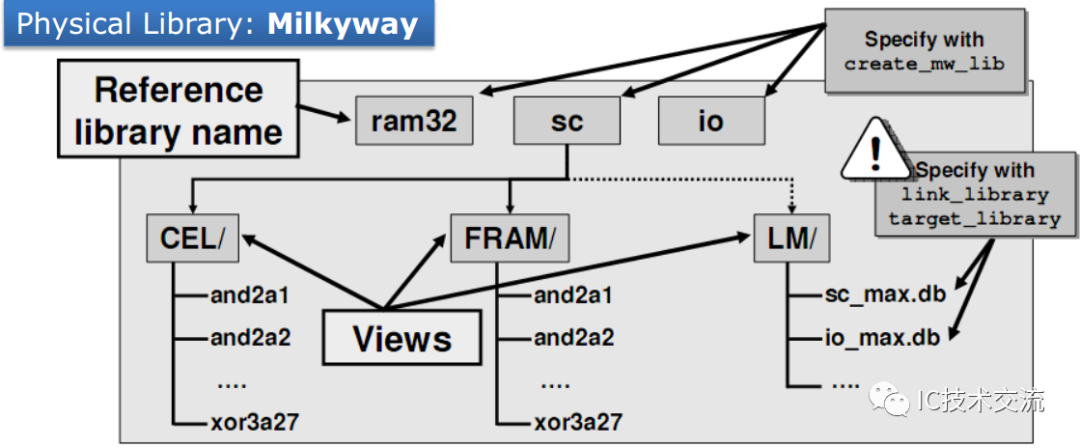

這里我們首先說下物理庫,ICC中所有物理庫都以Milkway的格式存在包括stdcell、memory等物理庫,也包括設(shè)計(jì)本身。以stdcell為例,一般包含三類:CEL、FRAM和LM。其中CEL和FRAM是View信息,CEL包括所有的物理信息,F(xiàn)RAM只包含pin的位置和形狀以及routing blocage。PnR過程中,ICC只會(huì)把FRAM View讀進(jìn)memory,CEL View數(shù)據(jù)量太大,CEL View只在最后寫GDS時(shí)用。Routing blockage是繞線阻礙物,就是給某些金屬加上blockage屬性,讓工具走線時(shí)不通過該區(qū)域,避免route時(shí)把連線伸進(jìn)去,造成短路;

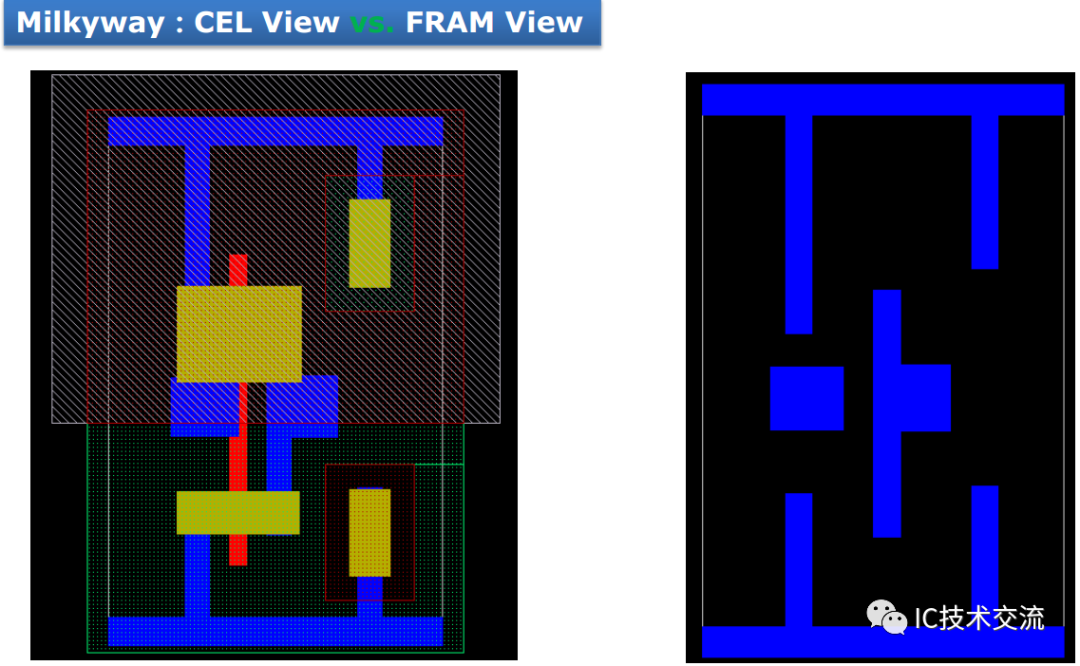

上圖左側(cè)為INV的CEL View,右側(cè)為INV的FRAM View。從圖中可看出FRAM中信息量確實(shí)很少。

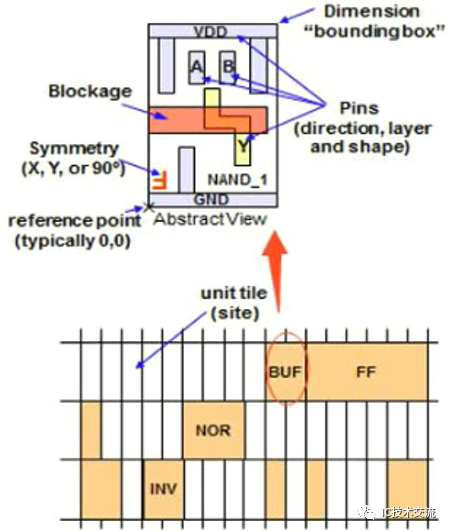

一個(gè)FRAM View中包含Pin的方向、位于哪一層、形狀。左下角是cell的參考點(diǎn),坐標(biāo)為(0,0)自動(dòng)布局時(shí)會(huì)被使用。還有中間的Blockage區(qū)域(避免走線)。通常一個(gè)cell放在Row中的一個(gè)site上,cell的高度和Row的高度是相同的,這些都在tf文件中有定義。VDD位于頂層,GND位于最下面,這些和row的線對齊。

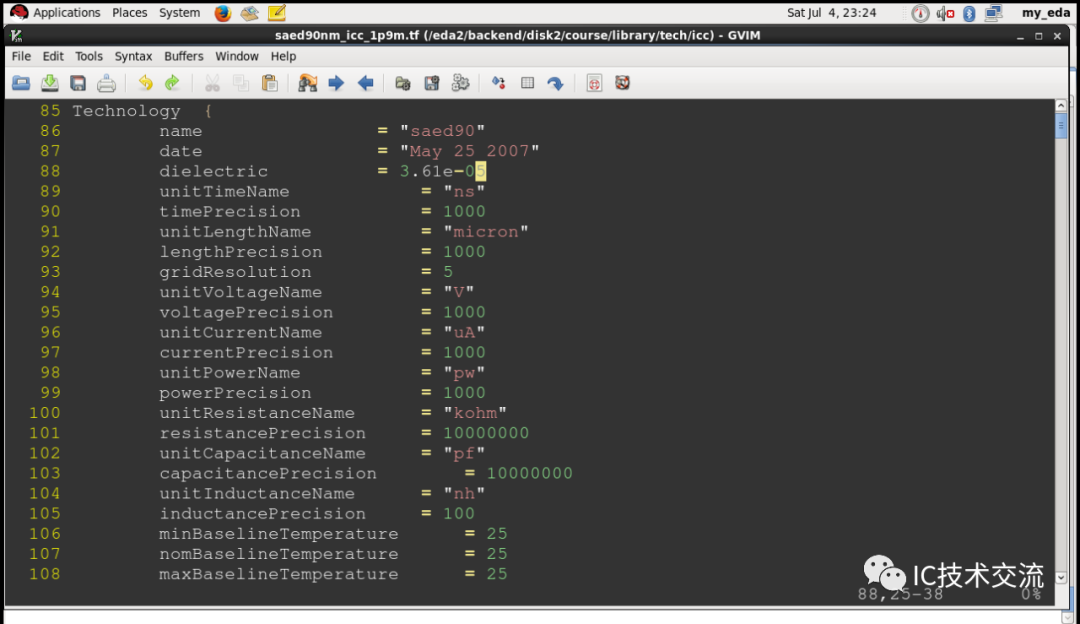

tf技術(shù)文件包括以下信息:

1、layer/via的數(shù)量和名字

2、每層layer的物理和電參數(shù)

3、每層layer的設(shè)計(jì)規(guī)則(最小線寬,線間距)

4、每個(gè)cell的單位和精度

5、每層的layer的顯示顏色和模式

技術(shù)文件內(nèi)容如上圖所示,里面定義了很多物理參數(shù)。

至于tlu+文件用于對線負(fù)載模型建模,ICC的RC估算比DC精確的多,已經(jīng)可以表達(dá)真實(shí)的線延遲。后端工具基于此可計(jì)算wire的寄生參數(shù):包括電阻、電容、耦合電容。

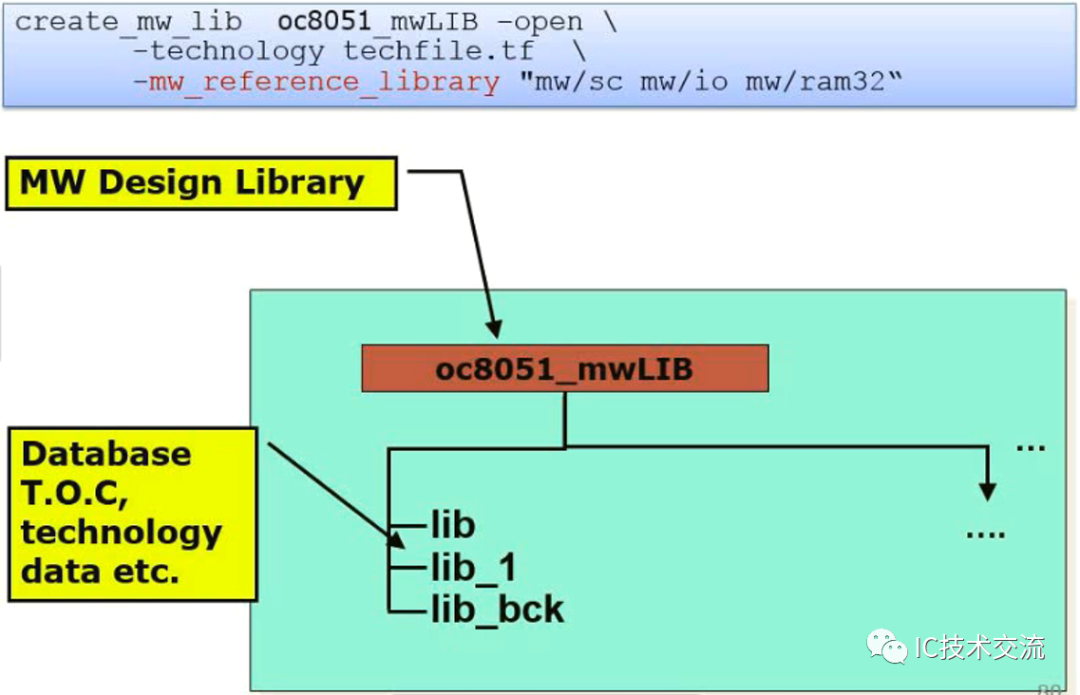

在ICC處理的第一步中就是創(chuàng)建milkway_lib,它會(huì)創(chuàng)建名為oc8051_mwLIB文件夾。并將技術(shù)文件和mw文件導(dǎo)入其中。

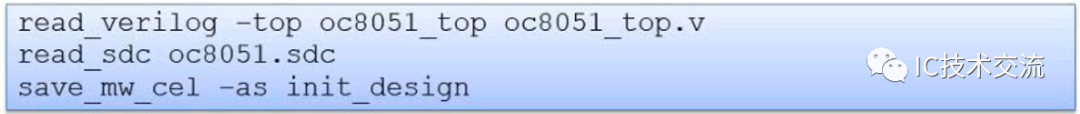

接下來讀入網(wǎng)表文件和約束文件,同時(shí)保存CEL View數(shù)據(jù)

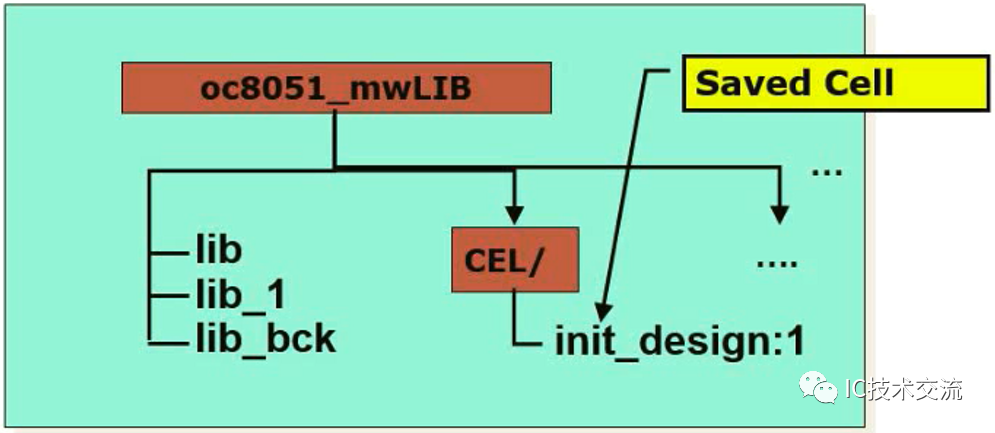

此時(shí)原有文件夾下會(huì)新建CEL文件,并將mw數(shù)據(jù)保存為init_design庫文件。在Design Setup & In階段,讀入所有文件后,此時(shí)并沒有floorplan操作,所有cell堆積在左下角。

floorplan步驟:先擺放大的mcro cell,然后擺放stdcell,這期間需要固定IO位置。對于最底層晶體管的供電而言,M1或M2與Row平行的會(huì)放置metal,依次與cell的VDD和VSS相連,在M6或M7放置供電網(wǎng),高層次的layer通過via與底層次的Layer相連,從而搭建整體的電源系統(tǒng)。這里需要說明一點(diǎn),如果M1是橫向的,那么M2必須是縱向的,以此減少線干擾,相隔兩層的metal必須正交,不能平行(與硬件PCB多層板布線很相似)。

floorplan本質(zhì)是包含三方面:PPA(功耗性能面積),這三方面需要折中處理。這之后就到了Placement階段,工具會(huì)自動(dòng)將每個(gè)cell放入site中。

在Route之前,ICC做place_opt進(jìn)行優(yōu)化時(shí)用Virtual Route估計(jì)連接線的長度和形狀,以此根據(jù)TLU+模型估計(jì)RC參數(shù)。事實(shí)上,在后面的CTS階段,由于沒有route,所以也通過同樣的方法估計(jì)RCPlacement階段,需要滿足sdc約束下的setup timing,所以完成place后,要分析Timing。

-

IC設(shè)計(jì)

+關(guān)注

關(guān)注

38文章

1295瀏覽量

103918 -

晶體管

+關(guān)注

關(guān)注

77文章

9682瀏覽量

138080 -

晶圓廠

+關(guān)注

關(guān)注

7文章

620瀏覽量

37857

原文標(biāo)題:IC后端概述(上)

文章出處:【微信號:IP與SoC設(shè)計(jì),微信公眾號:IP與SoC設(shè)計(jì)】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

IC前端和后端設(shè)計(jì)的區(qū)別

數(shù)字IC后端(CAD)

數(shù)字IC后端設(shè)計(jì)介紹,寫給哪些想轉(zhuǎn)IC后端的人!

后端集成電路SAA7158電子資料

數(shù)字IC后端設(shè)計(jì)電源規(guī)劃的學(xué)習(xí)資料分享

后端系統(tǒng),后端系統(tǒng)是什么意思

IC前端設(shè)計(jì)(邏輯設(shè)計(jì))和后端設(shè)計(jì)(物理設(shè)計(jì))的詳細(xì)解析

IC后端概述(上)

IC后端概述(上)

評論