在這個技術日新月異的時代,一個不爭的事實是,我們已經邁入了芯片集成度迅速提升的階段。隨著5G、自動駕駛、人工智能等領域的飛速發展,對芯片性能的需求也急劇增加。這種挑戰驅動芯片制造商走向更高的集成度,增加更多的晶體管,引入先進的光刻技術,并不斷探索尖端的芯片工藝和封裝方式。

一顆表面微小的芯片內部蘊藏著千絲萬縷的設計細節。因此,對芯片設計的電路布局、連線以及物理特性進行及時的驗證和確認至關重要。哪怕是一小步的差錯,都有可能導致整體失效,這凸顯了物理驗證在芯片設計中的關鍵地位。

物理驗證在先進芯片設計中的核心地位

近年來,“Shifting left”策略在芯片產業中受到了廣泛關注。其核心目標是應對現代芯片設計的高復雜度,盡早在物理設計階段進行驗證,幫助設計團隊及時糾正錯誤,以保證最后的設計準確無誤,為最終流片做好充分準備。在此策略中,物理驗證的重要性不言而喻。

物理驗證主要包括設計規則檢查(DRC)、布局與原理圖(LVS)檢查和面向制造設計檢查(DFM)。在整個芯片設計項目中,一旦系統芯片(SoC)的主要部分組裝完成,就可以開始進行DRC和LVS的驗證。開發團隊應當在每個設計階段,如宏設計、IP和塊級設計階段,無縫且清晰地進行物理驗證。與全芯片的組裝并行地進行物理驗證是更為高效的做法。

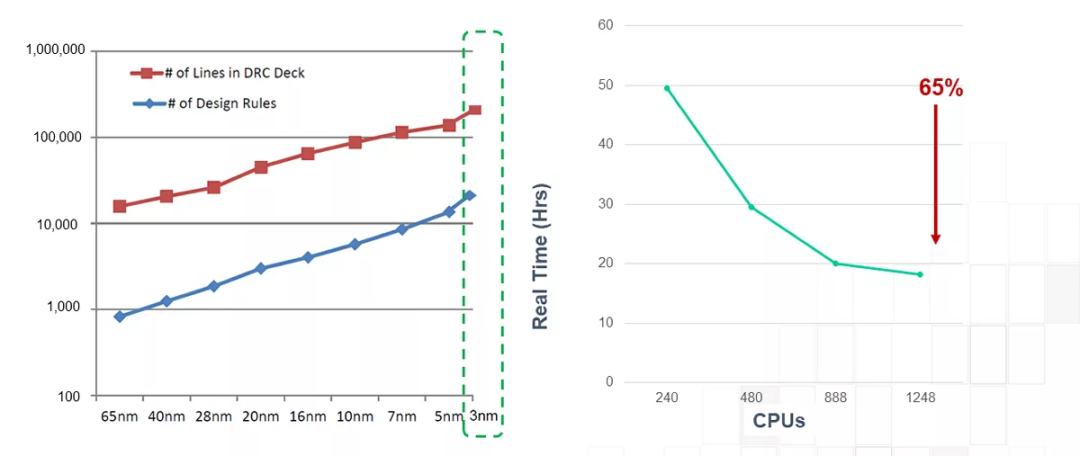

盡管物理驗證一直都是計算密集型的工作,但如今的芯片設計尺寸和復雜性又將這一挑戰提升到了一個全新的層次。對于擁有數十億晶體管的多芯片系統而言,一個DRC或LVS的任務可能需要使用數百個CPU核,運行數天。隨著工藝節點從7nm到5nm,再到3nm的進步,這一問題尤為突出。

在大型SoC的設計中,我們往往需要處理數百個組件,包括布局與路由塊、模擬單元、存儲器、第三方IP和I/O單元。盡管在設計過程中,這些組件各自可能都已經經過詳細的DRC檢查,但當它們被集成為一個完整芯片時,又會暴露出大量另外的設計問題,例如組件之間得位置不對齊,就可能觸發大量的DRC違規行為。傳統的DRC工具需要數日才能完成對如此龐大的設計的初次檢查,這可能導致在項目的最后階段,浪費流片輸出團隊大量額外的計算時間。

與此同時,LVS工具的發展也面臨著相似的挑戰。在現代的大規模電路設計中,LVS檢查可能耗費數天時間。初次整合所有設計組件后,LVS可能會揭示出如宏/IP問題、頂層整合錯誤和界面引腳對齊問題等新問題。雖然這些問題本身可能容易修復,但它們確實會延長LVS的運行時間并增加計算要求,從而阻礙設計師的快速迭代。

在如今競爭白熱化的芯片市場中,上市時間(Time-to-market)是很重要的競爭力。任何物理驗證過程的延誤都可能影響芯片的上市時間,這不僅會帶來巨大的經濟損失,還可能對企業的整體策略造成打擊。

因此,物理驗證工具必須不斷創新和改進,進一步智能化并提高效率。

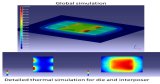

理想中的DRC工具應該能按制造商的基本規則自動運作,迅速評估設計質量。當設計基本合規時,它可以順暢地完成剩下的檢查任務。此外,如果DRC能為設計師提供一個錯誤“熱圖”則是極大的加分項,它幫助設計師直觀地在數百萬的小錯誤中標識出目標問題區域,使設計師能迅速定位并解決問題。

LVS工具應當能夠準確地識別出設計中哪些部分是關鍵,提供一個自動化的方法來迅速定位全芯片LVS運行中出現問題的根源。

這些壓力無疑給到了EDA供應商,但一旦解決,這也將成為他們的核心競爭力。

顛覆傳統,新思科技塑造下一代物理驗證

新思科技的IC Validator是一個專為現代設計的物理驗證工具,它采用業界先進的分布式處理算法,可擴展到超過 4,000個CPU核,實現了目前業內領先的超大芯片的物理驗證簽收。數十億個晶體管的設計,一天內就可完成設計規則檢查 (DRC)、布局與原理圖對照驗證 (LVS) 以及金屬填充的一次迭代。此外,IC Validator在僅有少量資源的情況下也可以立即啟動,在資源增加時使用更多的資源。

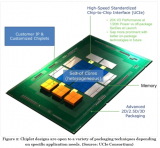

(圖源:新思科技)

近幾年來,新思科技不斷地對IC Validator進行升級,以滿足日益變化的芯片驗證需求。

1

Explorer DRC技術

早在2018年,新思科技就引入了Explorer DRC技術,為開發團隊提供了在同一天進行DRC檢查的功能,并在SoC整合過程中在幾小時內識別關鍵設計缺陷。它的性能相比傳統DRC流程大大提高,使運行時間加快五倍,使用的核心數量減少五倍。這意味著即使設計是“不干凈”的,16或32核的CPU也可以在幾小時之內完成一個典型5nm芯片的DRC驗證,幫助流片工程師快速找到主要的設計問題并立即開始修復。

值得關注的是,新思科技正在嘗試通過云計算進行IC驗證,并以DRC作為其測試場景。這種創新的動力來源包括一下幾方面:

(1)面對成本壓力、不斷縮小的市場窗口以及更好的性能和更多功能的市場需求,本地存儲已成為許多企業無法承受的負擔。在云端進行IC設計,并實現計算資源的彈性擴展的時機已經到來。

(2)單純地為DRC工具增加計算能力并不能縮短運行時間,因為在IC驗證過程中,某些計算資源可能會時常處于閑置狀態,這導致了資源的浪費,增加了企業成本。

云計算為現代IC驗證提供了有效的途徑。通過云驗證,企業可以輕松地從本地數百核擴展到云端的數千核。這種方式不僅提供了彈性、靈活性和擴展性,還確保了資源的合理利用。同時,DRC的任務也能分配到多個核心上并行執行,從而實現資源的最優化,節約時間和成本。

新思科技的IC Validator的動態彈性CPU管理與流行的作業隊列系統(如LSF和SGE)能夠無縫集成,并可在本地和云端等不同類型的計算網絡上使用。例如,在新思科技與臺積電和微軟的合作中,在云端進行的IC設計將臺積電 N3E工藝的驗證時間從約50小時縮短到不到20小時,效率提高了65%,同時成本和CPU使用時間也比本地減少了25%。如下圖所示。除了所有時間和成本優勢之外,新思科技的虛擬網絡(VNET)可以很好的確保云端部署EDA的安全性。

圖片來源:臺積電

2

Explorer LVS技術

2019年新思科技又推出了Explorer LVS技術,這也是行業首款是專為SoC時代設計的現代LVS解決方案。Explorer LVS可以在簽核準備驗收時的任何時候使用,以檢查頂層設計的完整性。而且使用Explorer LVS可以快速、高效地檢測到關鍵問題,使驗收工程師無需承受傳統LVS工具的低效率。當首次完成全芯片整合后立即運行時,其性能和效益可以達到最大。

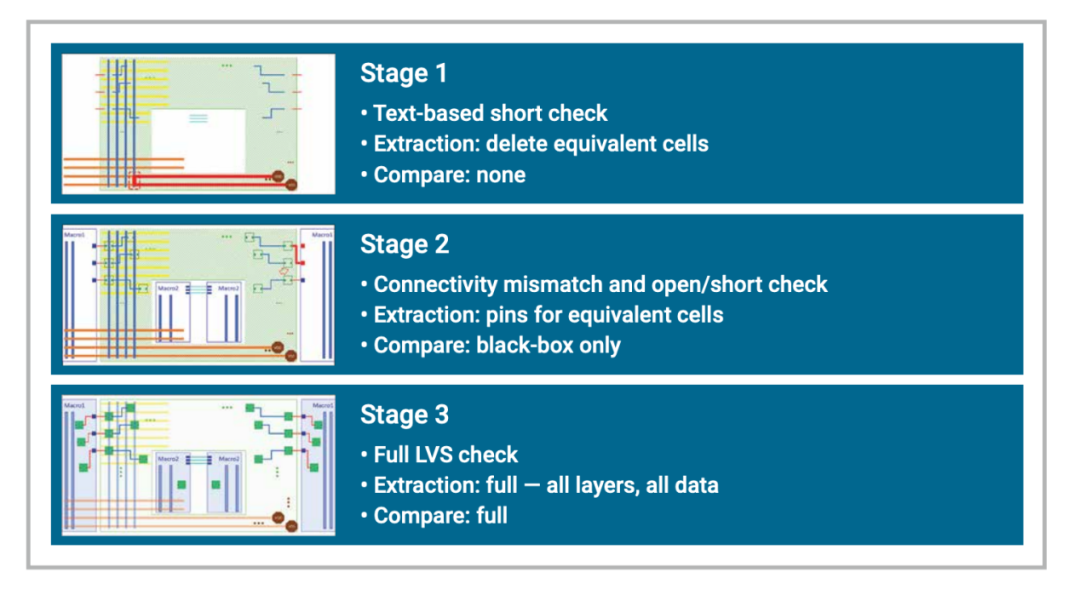

盡管Explorer LVS的主要設計目標是完整芯片的布局,但它適用于任何大小和復雜度的設計。設計越大、越復雜,其相對于前一代工具的性能就越好。Explorer LVS包括三個不同的階段,如下圖所示。

Explorer LVS檢查的3個階段

(圖源:新思科技)

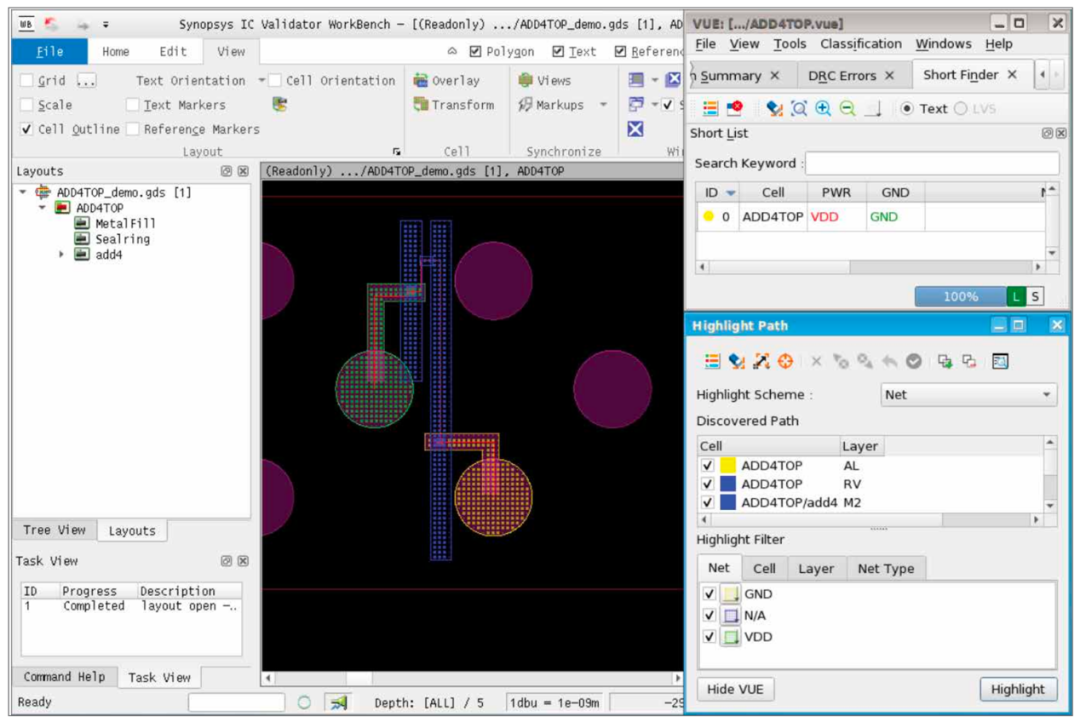

一旦Explorer LVS對設計執行,就會生成一個摘要文件,工程師可以使用摘要文件來檢查全芯片設計的整體質量,以簽署準備度來衡量。每個單獨的錯誤都可以通過文本格式的日志文件或交互工具進行檢查和調試。對于設計中的短路的調試,Explorer LVS的結果可以立即加載到IC Validator ShortFinder中,以便進行快速和簡便的基于GUI的交互調試,如下圖所示。

在LVS中調試設計缺陷

(圖源:新思科技)

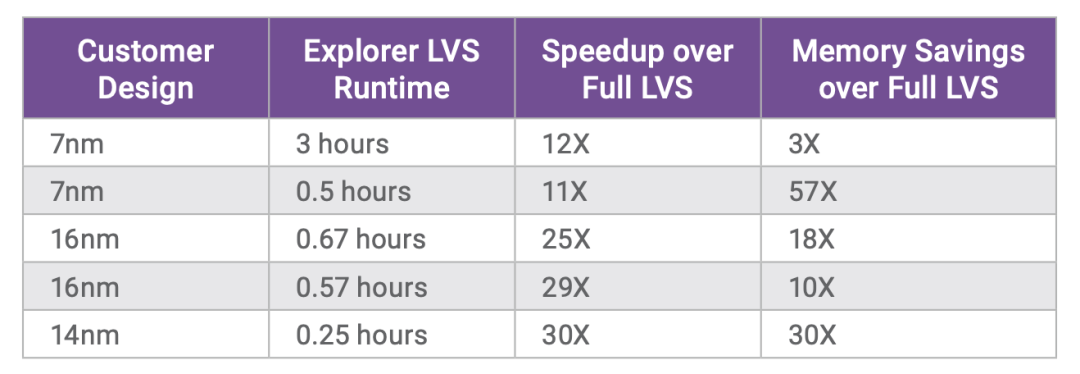

Explorer LVS可以與全面的LVS完美配合。在典型的流程中,當我們在初步的布局和路徑規劃后進行區塊或模塊設計時,可能會運行全面的LVS,以便在項目早期發現問題。當這些部分組裝成一個完整的芯片時,Explorer LVS提供快速的運行時間和直觀的調試來盡量清理設計,然后使用全面的LVS進行最終驗收。如果在驗收前發生了工程變更訂單(ECOs)或最后一刻的宏/模塊更新,Explorer LVS能確保設計的完整性不受損害。如下圖所示,在真實的客戶設計中,與全面的LVS相比,Explorer LVS的運行速度最快可提升30倍,且使用的內存減少了30倍。

Explorer LVS的實際性能結果

(圖源:新思科技)

結論與展望

隨著半導體技術的迅猛發展,面對日益增長的挑戰,我們亟需更為先進的設計驗證工具。新思科技在物理驗證技術上的持續創新,特別是通過Explorer DRC和Explorer LVS,再加上其在EDA云技術上的探索與突破,可以使芯片工程師更為高效和精確地完成設計驗證。這不僅確保了產品的卓越質量和穩健可靠性,而且為當下的芯片物理驗證流程注入了創新活力。

展望未來,隨著云計算的普及和技術的成熟,我們期望EDA工具能夠更加完美地集成到云環境中,實現真正的全球協作和無縫的設計驗證流程。同時這就需要像新思科技這樣的EDA廠商繼續在物理驗證技術上進行更深入的研究與創新。這將為整個半導體產業帶來更大的效率提升和成本節約。

審核編輯:劉清

-

芯片設計

+關注

關注

15文章

1015瀏覽量

54878 -

人工智能

+關注

關注

1791文章

47183瀏覽量

238264 -

DRC

+關注

關注

2文章

148瀏覽量

36158 -

DFM

+關注

關注

8文章

463瀏覽量

28198 -

自動駕駛

+關注

關注

784文章

13784瀏覽量

166394

原文標題:芯片集成度飆升,物理驗證成為關鍵

文章出處:【微信號:芯長征科技,微信公眾號:芯長征科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

三星芯片代工新掌門:先進與成熟制程并重

Chiplet在先進封裝中的重要性

混合鍵合在先進封裝領域取得進展

晶圓微凸點技術在先進封裝中的應用

AI網絡物理層底座: 大算力芯片先進封裝技術

英飛凌CEO:亞洲在芯片生產與研發計劃中占據核心地位

如何控制先進封裝中的翹曲現象

功放芯片的定義和分類

什么是IGBT芯片?它有哪些用途?

人工智能芯片在先進封裝面臨的三個關鍵挑戰

物理驗證在先進芯片設計中的核心地位

物理驗證在先進芯片設計中的核心地位

評論