隨著車輛電子化水平的提高,車輛上各種ECU逐漸增多,他們通過總線進行通信,以實現車輛各個系統之間的協調與控制,但由于車輛電子系統的復雜性和總線通信的高頻率,可能導致ECU總線干擾通信信號的丟失,影響各個控制單元之間的正常通信和數據傳輸,進而影響車輛系統的性能和功能,需要一款設備模擬干擾,VH6501由此誕生。

VH6501是一款CAN/CAN FD總線干擾儀,將干擾硬件和網絡接口卡集成在一起的一款設備,可以與CANoe進行無縫集成,通過CAPL腳本進行控制。主要功能是數字干擾和模擬干擾,可以通過自定義改變顯性或隱性序列實現干擾,也可以實現CAN線對電源或地短路及CAN高低之間短路或者改變兩者之間的電阻電容值來進行干擾。

它主要可以用來進行模擬干擾測試、Bus-off測試、采樣點測試,觀察被測控制器在故障狀態下的網絡行為、恢復策略及采樣點是否滿足相應需求;通過模擬真實的干擾場景,測試總線在干擾環境下的穩定性;提高總線的可靠性、檢測總線抗干擾能力、保證正常通信。

設備使用

下面將向大家介紹拿到設備后大家如何使用。

硬件連接

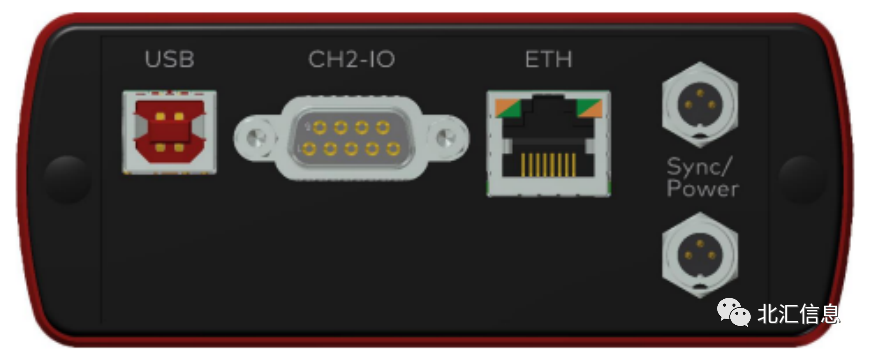

通過USB2.0接口與電腦端連接,此外VH6501 需要額外供電,選擇Sync/Power(任選其一)經電源線供電,另一個用于通過同步線與Vector其他硬件產品實現硬件時鐘同步;

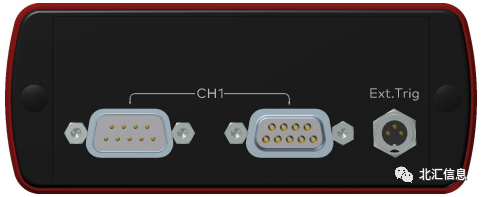

CH1通道有兩個DB9接口,公頭male和母頭female,兩個DB9接口內部互聯,且pin腳定義一致;通常情況下連接任意通道即可,如需進行CAN h與CAN l反接測試時,至少要連接母頭。

通過CH1與被測DUT連接從而施加干擾。

環境搭建

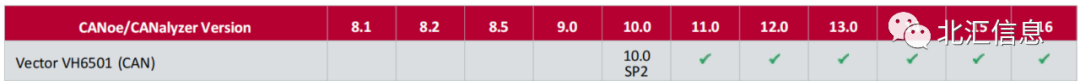

首先查看VH6501設備所支持CANoe的版本。

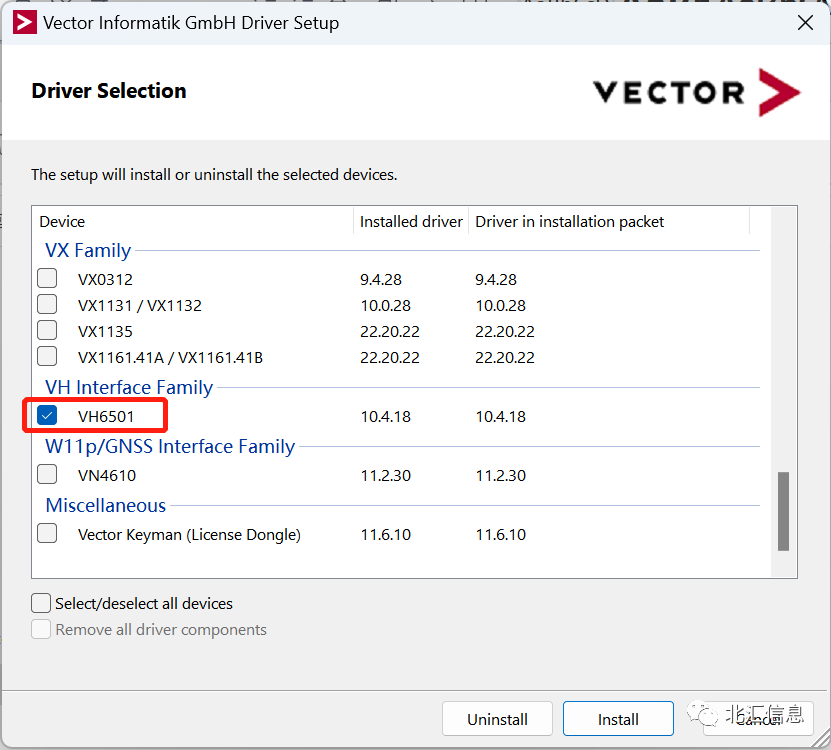

安裝VH6501硬件驅動。

本次以上位機軟件CANoe16.0 SP4為例

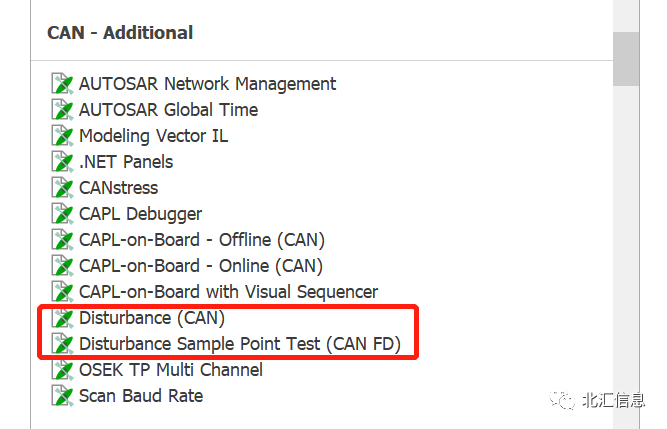

打開CANoe demo—Disturbance(CAN)工程,進行CAN總線干擾演示。

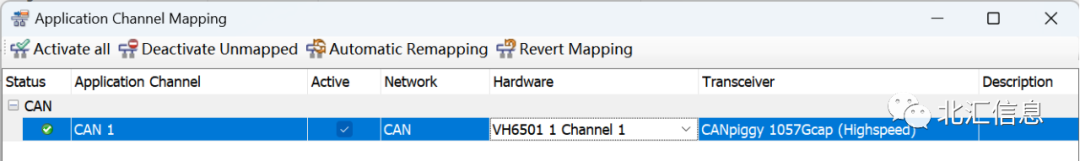

通道匹配。

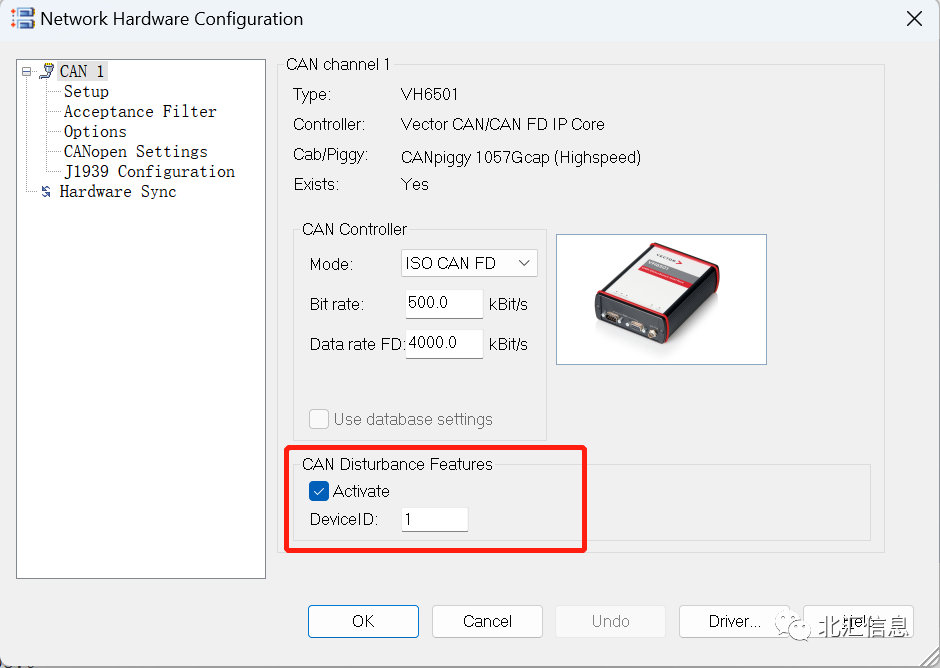

當我們用于總線干擾時,需要勾選active,否則只能用做網絡接口卡使用。

若CANoe接入多個VH6501,則需設置DevicelD通過不同的DevicelD標識不同的VH6501設備。

測試過程

首先是數字干擾。

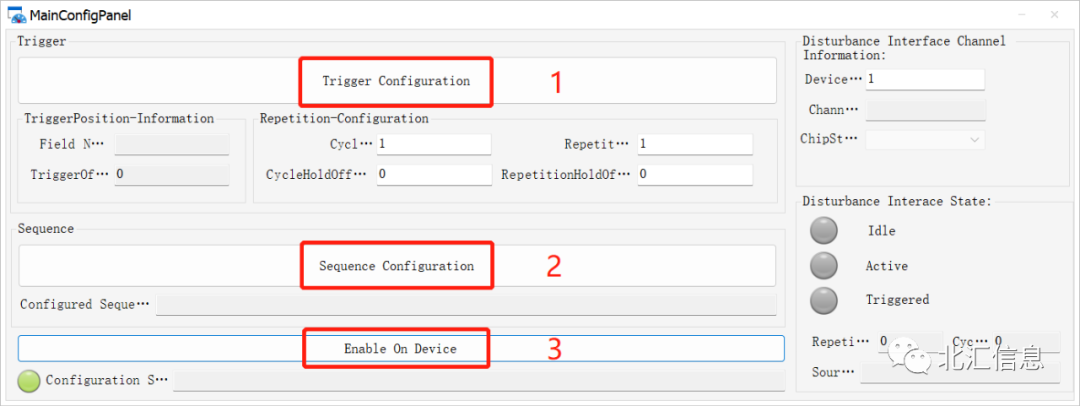

打開MainConfigPanel面板

點擊Trigger Configuration配置干擾報文及干擾位,如果是干擾所有報文,默認即可,如果干擾特定報文,填寫干擾報文ID、干擾位置 注意這里的干擾位置是實際干擾的前一位,TriggerOffset表示偏移量,可以干擾某個字節的具體位。

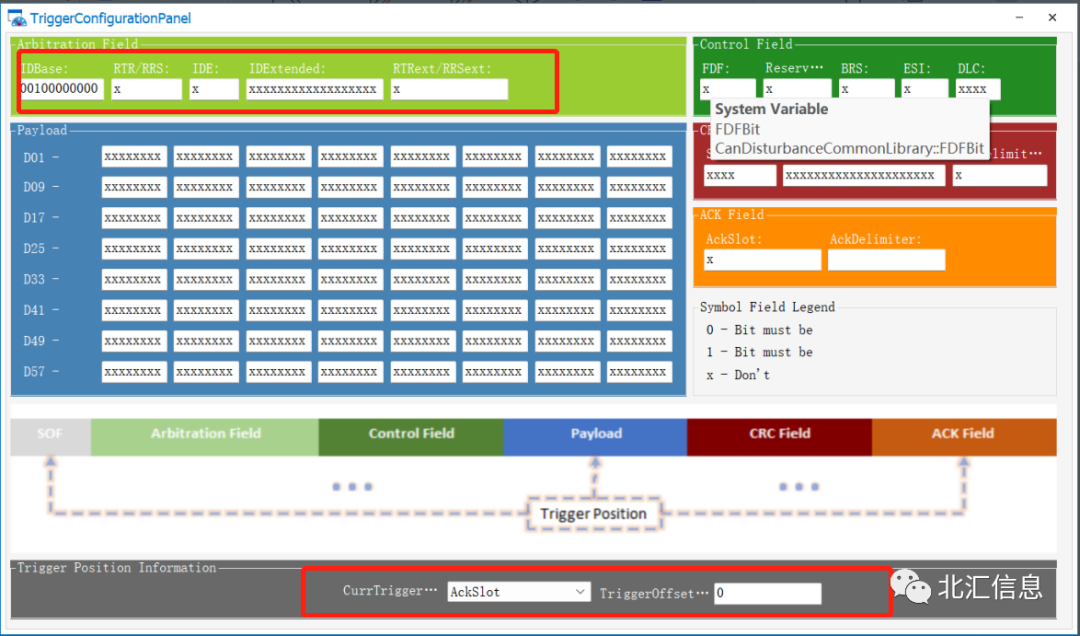

以ID=0x100為例,干擾AckDEL位。即在IDBase中填標準幀11位二進制ID,如果不滿11位,高位補零,湊齊11位,并將下方CurrTriggerField設置干擾前一位AckSlot位,Triggeroffset設置為0。

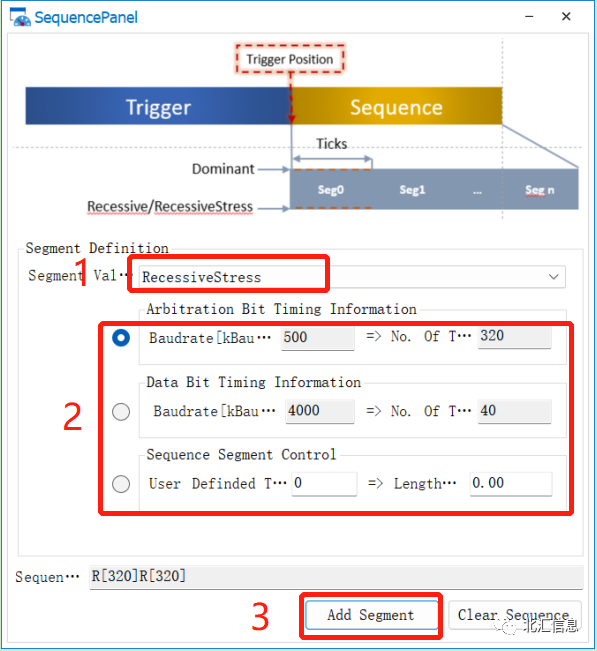

點擊Sequence Configuration 設置干擾序列

在這里可以將干擾序列設置為顯性Dominant、隱性Recessive、強制隱性RecessiveStress。

當CANoe正常運行時,sequence Panel面板會自動識別總線波特率,并提供可選擇的ticks長度,也可以用戶自定義設置;最后點擊Add Segment添加干擾。

注:在CAN FD通信過程中,如果干擾Ack Slot位,干擾結果是兩個連續的顯性位會被認為是有效的Ack應答,不會出現錯誤幀,導致這種方式無法干擾ACK slot位。

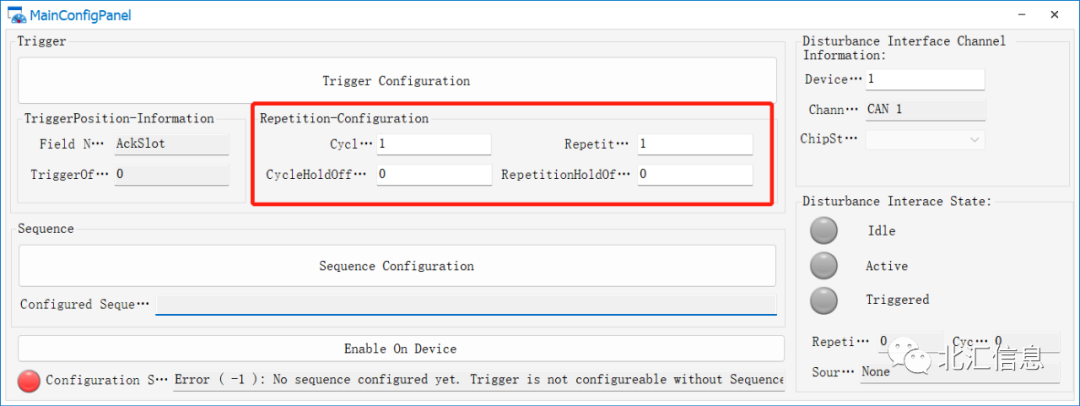

返回主面板,設置好干擾次數和循環次數。

如果進行Bus off測試時,Cycles表示Bus off的次數,Repetition中填寫固定干擾次數為32次(干擾一次,ECU的TEC累計次數+8,在連續干擾32次后,TEC的值為256,ECU便會進入Bus off狀態)。

注:如您想了解關于Bus off的詳細內容,可以觀看前期文章:《科普系列:CAN總線錯誤幀及排查方法簡介》

最后點擊Enable On Device激活使能干擾。

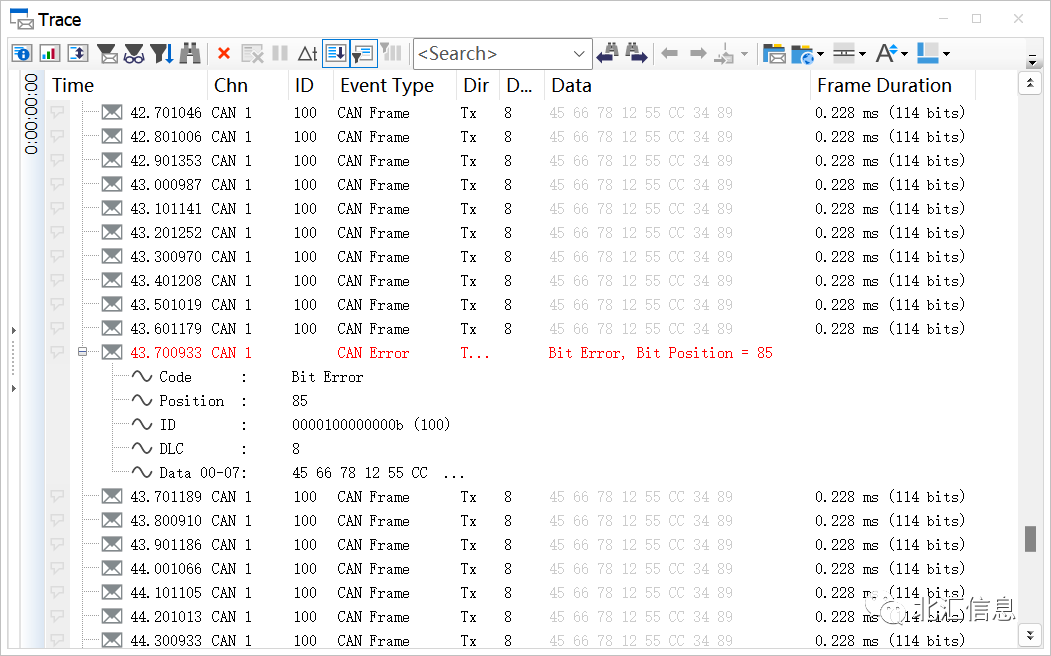

打開trace窗口,最終效果如圖所示。

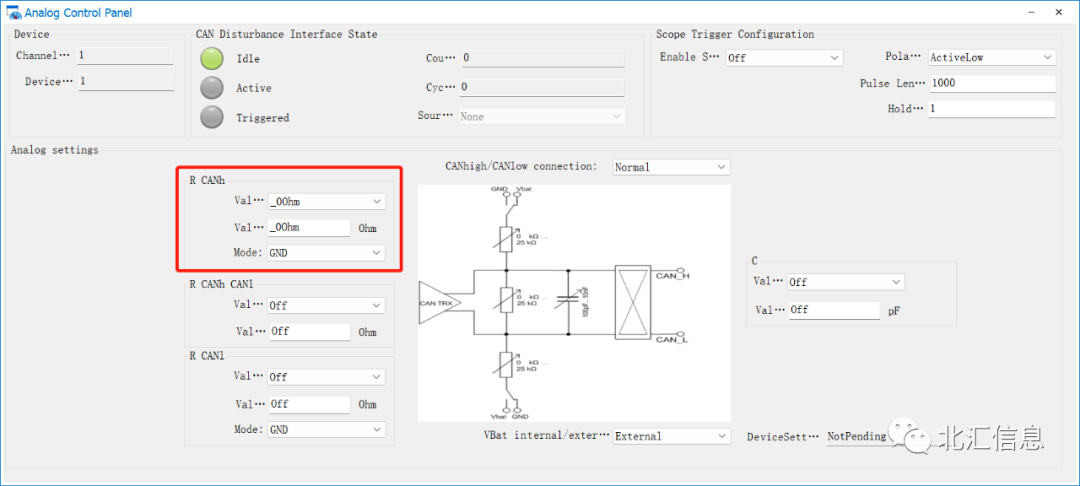

接下來是模擬干擾測試,可以進行CANH/L與電源/短路、CANH與CANL之間短路及增加電阻或電容、CANH與CANL之間反接。

運行工程后,打開Analog Control Panel面板進行操作,在R CAN 中,將Mode設置為VBat/GND,Vlaue值設置為0hm實現CAN h對電源或地短路。

注:CAN h或CAN l短接至電源時,需要將外部電源的VBat/GND分別連接公頭的Pin9和Pin3引腳。

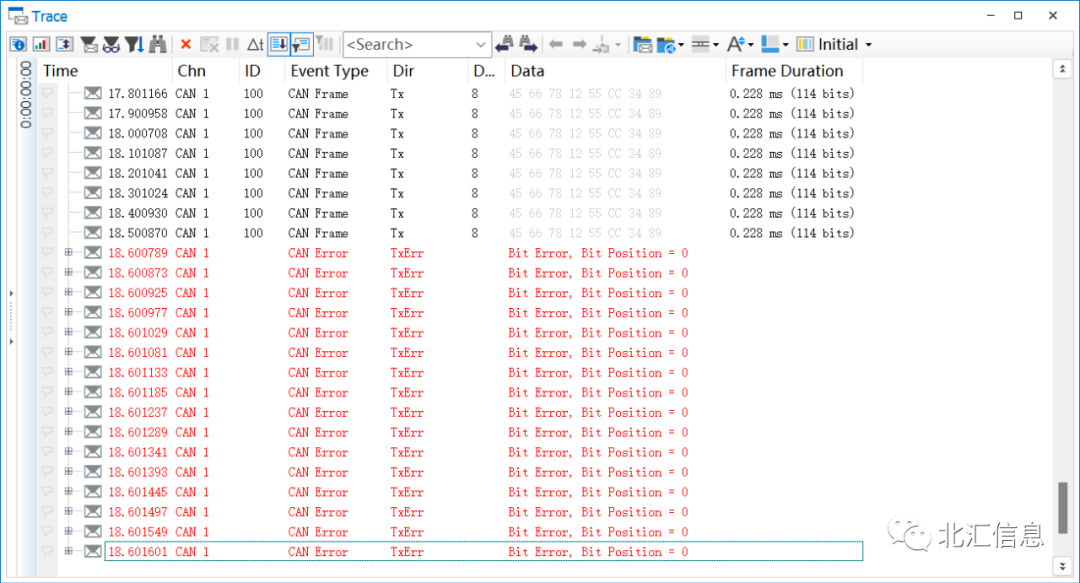

打開trace窗口,總線進入buss off狀態,結果如圖所示。

CAPL報文干擾相關函數介紹

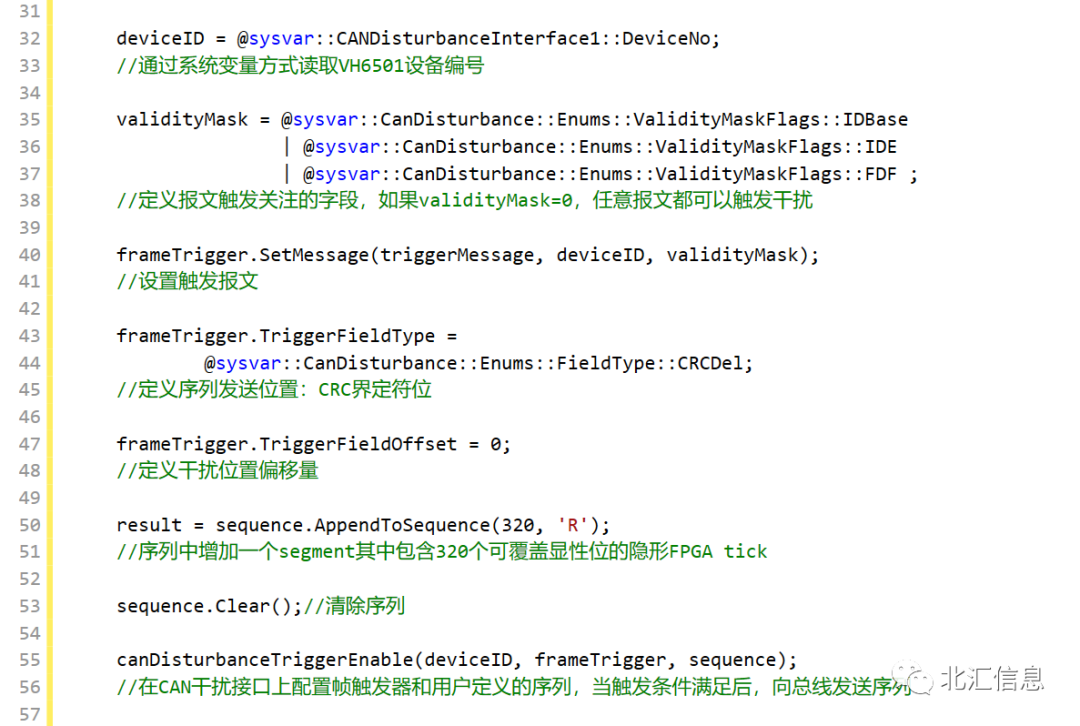

VH6501主要通過CAPL腳本進行控制,我們也可以通過編寫腳本實施干擾,下面將簡單介紹相關函數及使用方法:

注:因為VH6501的FPGA晶振是160M的,所以一個 FPGA ticks 周期 T0 = 1/160M = 6.25 ns(納秒);CAN總線是500kb/s速率,所以周期位T1 = 1/500K = 2000 ns (納秒) ; 而320 * 6.25 =2000 ,也就是說需要320個 FPGA ticks才能剛好干擾一個CAN bit 位。

如果想進一步了解干擾函數的使用方法,可以打開help文檔進行查看CAN Disturbance里面相關干擾函數,里面內容有詳細的描述說明。

關于VH6501的基本應用就展示到這里啦!希望上述內容對大家有所收獲。

總 結

北匯信息作為Vector中國的合作伙伴,始終專注于汽車電子領域的新技術和新產品,為整車廠和零部件企業提供完整的研發、測試解決方案,為工程師在汽車領域提供“趁手裝備”!我們不僅提供相應的工具和技術支持服務及培訓,還針對不同的應用提供相應的解決方案,助力中國客戶的研發效率提升。歡迎聯系北匯信息,我們將根據不同需求為您提供針對性的高效、靈活、穩定的解決方案!

-

通信

+關注

關注

18文章

6036瀏覽量

136061 -

總線

+關注

關注

10文章

2888瀏覽量

88133 -

ecu

+關注

關注

14文章

887瀏覽量

54537 -

汽車

+關注

關注

13文章

3531瀏覽量

37367

發布評論請先 登錄

相關推薦

SN6501DBVR和TD301配合時總線上出現錯誤字節怎么處理?

MT6501在線編程角度編碼器IC

艾畢勝電子MT6501IC展現智能娛樂機器人的“超級大腦”

MT6501磁編碼IC——縫紉機器人的新突破

艾畢勝電子MT6501磁編碼IC將在挖掘機鏈條軸數控機床的發展前景

MT6501磁編IC在涂膠機器人領域應用

MT6501磁編碼IC在機加工機器人的應用

MT6501磁編碼IC在軟包電池OCV測試分選設備中的應用

MT6501磁編碼IC在PACK產線中的應用

MT6501磁編碼IC在組裝流水線中的應用

VH6501基本使用介紹

VH6501基本使用介紹

評論